Architecture Exploration for Flash-Based Systems Presented by Darryl Koivisto CTO, Mirabilis Design Inc.

# What is Architecture Exploration in the context of FLASH Memory?

- The ability to model FLASH memory in the context of actual system use for this common resource.

- Model Abstraction

- Being able to accurately describe a FLASH memory in terms of system demands, application demands, and power considerations.

- Model Traffic and Power Use

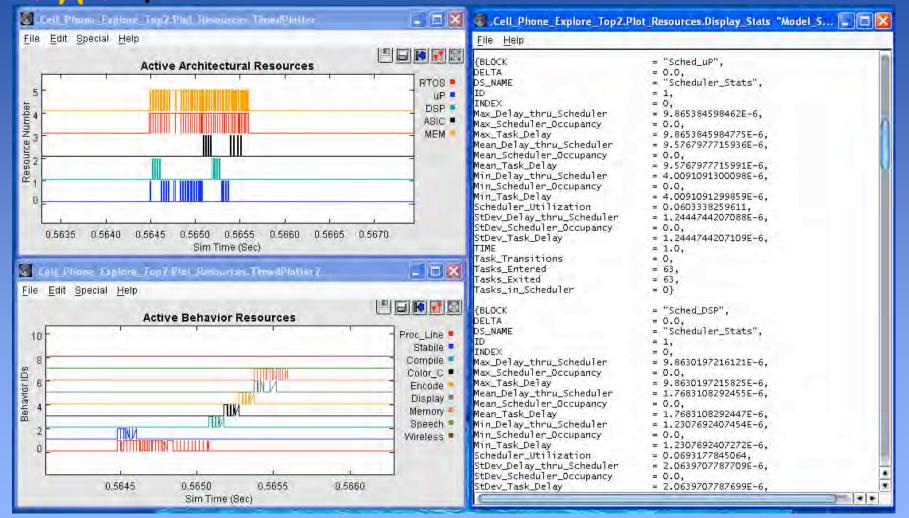

- Being able to obtain very useful statistics for elements of a typical system, such as processor, cache, SDRAM, or IO activity in terms of throughput, latency, or utilization.

- Model Statistics: min, mean, max, and stdev

#### What are the advantages of FLASH Memory Architecture Exploration?

- In FLASH memory, complexity and concurrency can be difficult to determine the design effects of fast reads and slow writes.

- Multi-Core Processors? Multiple DSP Hardware execution?

- What is my video frame rate under worst case assumptions?

- One can determine peak usage of FLASH memory, whereas EXCEL spreadsheets can only provide average, or mean, estimates.

- Is FLASH memory use less than 80% of peak utilization?

- Less Re-design, Re-spins.

- Better Price-Performance of end product.

- Higher Quality Design in less time.

- More insight into Future Derivatives.

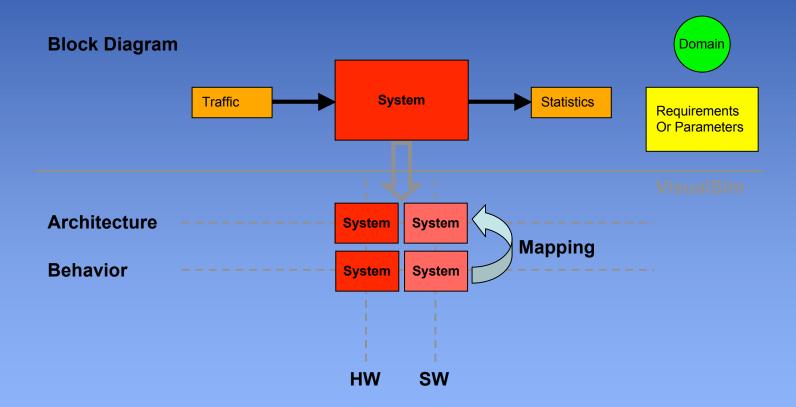

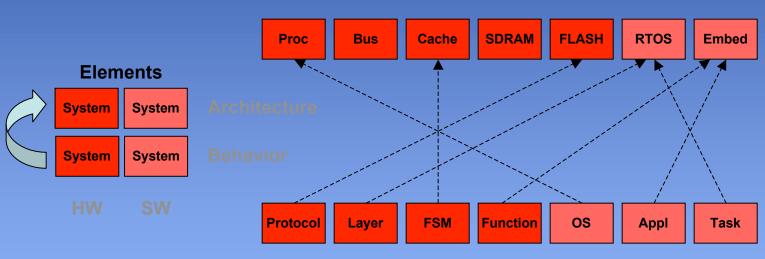

#### Modeling Views for FLASH Memory

Separating Behavior, Architecture, Software and Hardware.

## **Architectural View**

#### **Element Choices**

System Execution, Delays.

**System**

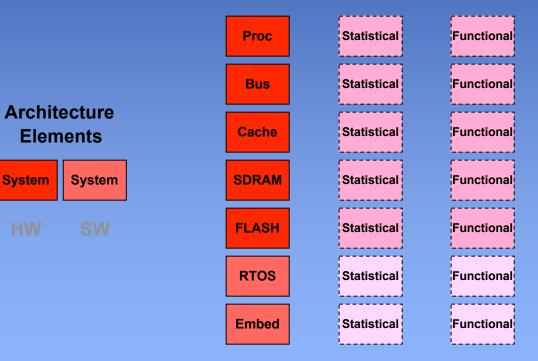

## Architectural View, Library

- Block Diagram oriented Hierarchical Blocks: Bus, Cache, RAM, FLASH, Processor (Registers, Pipelines, Parallel Execution, etc.), DSP, ASIC, FPGA, RTOS, SW Drivers, etc.

- Plug-n-Play meaning they can be used interactively and in some cases recursively, such as processor pipelines.

- Typical parameters include Speed\_Mhz, Word\_Width\_Bytes, OH\_Bytes, Burst\_Size\_Bytes, Source\_Field\_Name, Destination\_Field\_Name, Size\_Bytes, Priority\_Field\_Name, etc.

- Performance Statistics Blocks: Latency, Throughput, Utilization

- Plotting Blocks: Linked to Statistics to selectively plot

- Power, Cost, Reliability, Switch-Over Blocks support for common subsystems, above.

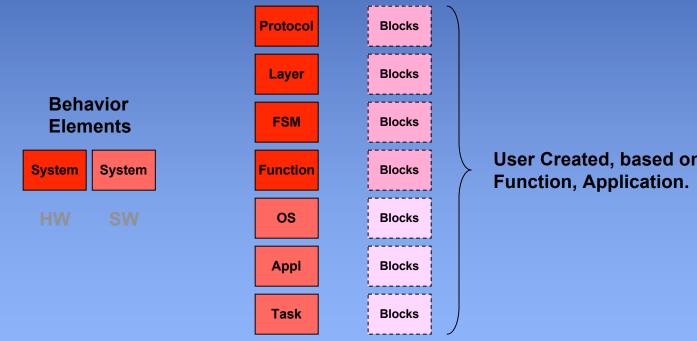

#### **Behavioral View**

#### **Element Choices**

User Created, based on

Typical System Flow, Algorithms, or States.

**Element Choices**

User Created, based on Function, Application.

Static and Dynamic Mapping of Behavior to Architecture.

#### **Model View**

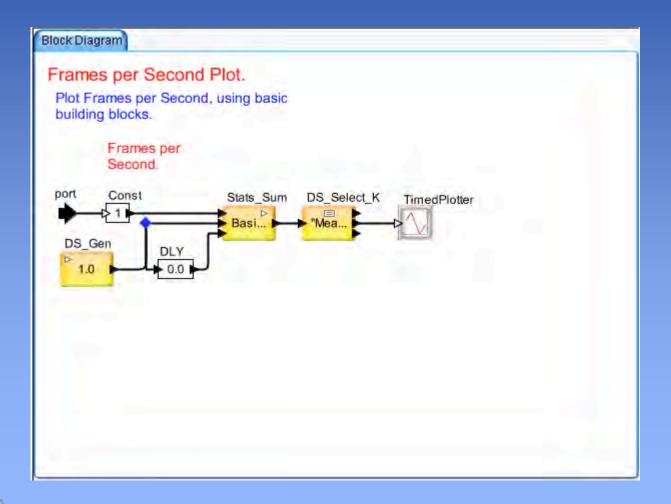

#### Block Diagram Cell Phone Exploration Model. This model quickly investigates different features competing for Parameters. **DE Simulator** uP, DSP, or ASIC platform resources, including priority of tasks. • Processor Speed Mhz 52.0 No buses are included at this level of abstraction. • Sim\_Time: 1.0 uP Resource DSP\_Resource ASIC\_Resource uP DSP ASIC Memory\_Resource Shared Memory Dispatch Tasks. RTOS\_Resource Plot Resources **RTOS Tasks** Most Plots to MEM. Inside. Architecture View Architecture View Process **Behavior View Behavior View** See Frames Priority=0 per Second. Plot\_FPS Process Lines Compile Picture Color\_Correct Encode Frame\_Traffic Display Sw Trigge Write Memory Stabilize Detailed Flow. Both Done Stabilze to Proceed. Priority=1 Speech Traffic Process Speech More Behavioral Flows can be added here. Wireless WiMax Traffic

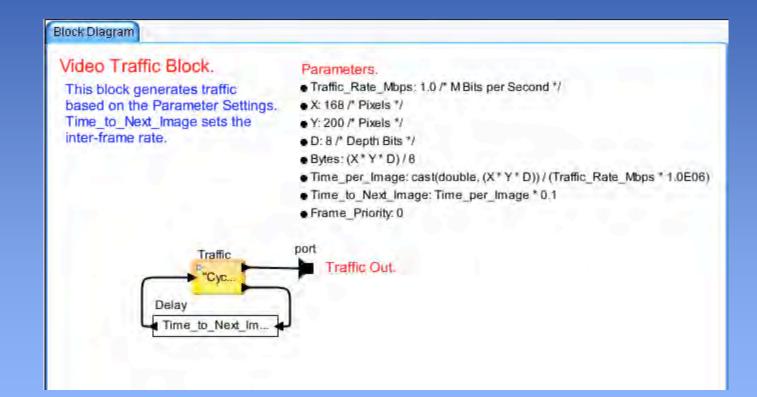

#### **Model Traffic**

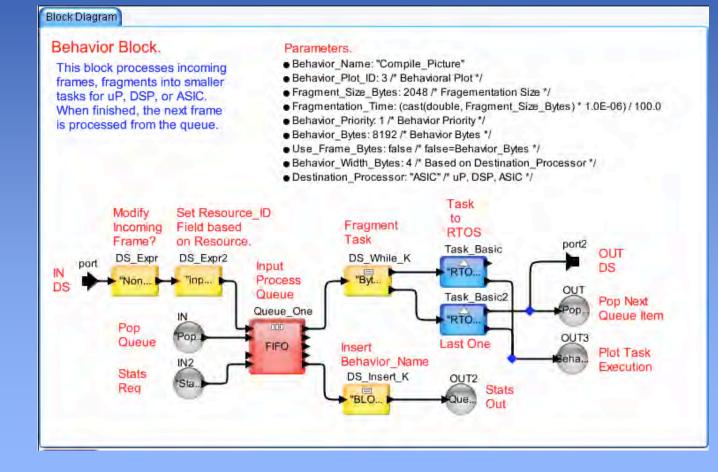

### **Model Behavioral Element**

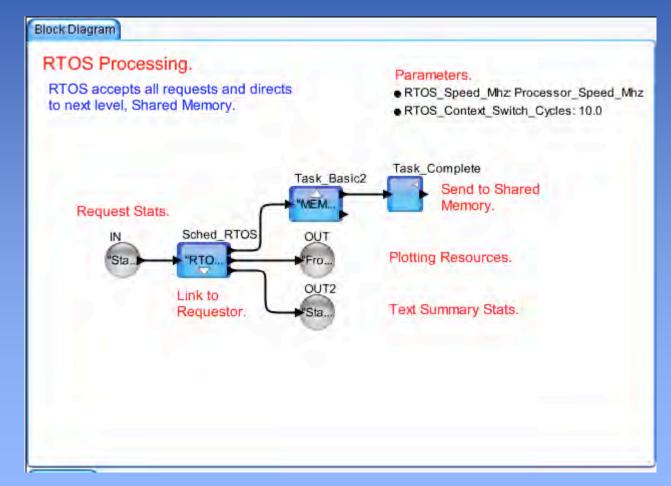

#### **Model Architectural Element**

#### **Model Statistics**

Shine SH Memory Output

#### **Darryl's Industry Association**

- Over 30 years of system design experience

- Developed first Channel Interface design package at Amdahl

- CTO of Mirabilis Design's VisualSim performance simulator

- Created new methodology for architecture exploration of memory subsystems and channels

- Chip Design

- Signetics/Philips.

- Hardware Architecture

- Amdahl.

- Software Architecture, System Architecture

- Ford Aerospace/Loral.

- Software Modeling Tools

- Systems and Networks, Cadence Design, Mirabilis Design.