# NAND Error Correction Code Choices

Pete Feeley

Strategic Marketing – NAND

Micron Technology, Inc

## NAND Error Correction Choices

- Leading edge NAND requires multiple bit error correction

- Hamming codes only correct single bit errors

- Reed-Solomon

- Binary BCH

- Metrics

- Overhead requirements

- Correction performance

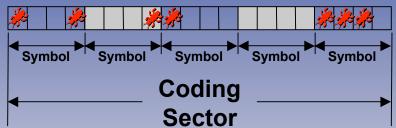

- Reed-Solomon and binary BCH have different underlying structures: one is symbol-based and the other is binary

# Comparing Symbol-Based to Flash Mem Synary Error Coding

#### Symbol-Based Code

- > Symbol length: m = 4 bits

- $\triangleright$  Code length: n = 5 symbols

- Bit errors = 7

- Symbol errors = 4

- $\triangleright$  Error correction: t = 4

- $\rightarrow$  Max error pattern: t \* m = 16 bits

#### **Binary Code**

- $\triangleright$  Symbol length: m = 1 bit

- $\triangleright$  Code length: n = 20 symbols

- $\triangleright$  Bit errors = 7

- ➤ Symbol errors = 7

- $\triangleright$  Error correction: t = 7

- $\blacktriangleright$  Max error pattern: t \* m = 7 bits

# Memory Binary Error Coding

#### Common ECC Choices for MLC NAND

#### **Reed-Solomon**

- >Symbol length: m = 9 bits

- Code length: n = 470 symbols

(528 bytes)

- $\triangleright$ Error correction: t = 4

- ➤ Redundancy<sup>1</sup>

requirements: 2tm = 72 bits

### **Binary BCH**

- $\triangleright$ Symbol length: m = 1 bit

- **Code length:** n = 4224 symbols

(528 bytes)

- $\triangleright$ Error correction: t = 4

- **≻**Redundancy¹

requirements: 3t = 52 bits

Max error pattern: (\*m = 4 bits

RS requires 39% more code redundancy for a given error correction.

RS can correct more bit errors but what does that mean for NAND Flash?

Note: (1) Redundancy is also referred as code overhead or parity and for NAND is typically stored in the spare area

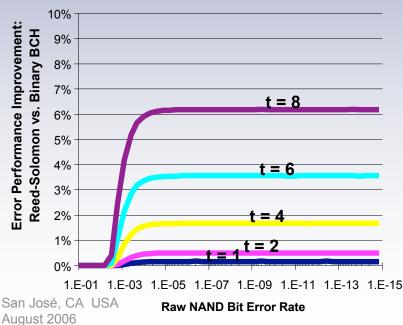

### Comparing Error Correction Performance

- Comparison of correction performance must be done in the context of the channel error conditions

- NAND error events are random and uncorrelated

- For NAND, Reed-Solomon corrects a few percent more error conditions than binary BCH

- A few percent change in error correction garners a generally insignificant improvement in the application bit error rate

| Designed<br>Error<br>Correction<br>Level | Typical Application<br>Bit Error Rates <sup>(1)</sup> |                      |

|------------------------------------------|-------------------------------------------------------|----------------------|

|                                          | Reed-<br>Solomon                                      | Binary<br>BCH        |

| t = 1                                    | 2.34e <sup>-15</sup>                                  | 2.34e <sup>-15</sup> |

| t = 2                                    | 7.69e <sup>-15</sup>                                  | 7.73e <sup>-15</sup> |

| t = 4                                    | 3.41e <sup>-15</sup>                                  | 3.47e <sup>-15</sup> |

| t = 6                                    | 3.59e <sup>-14</sup>                                  | 3.72e <sup>-14</sup> |

| t = 8                                    | 3.09e <sup>-15</sup>                                  | 3.28e <sup>-15</sup> |

<sup>1.</sup> Bit error rate is the ratio of error bits to the total number of bits read.

- Binary BCH is a better ECC solution for NAND than Reed-Solomon

- 39% Reduction in code redundancy

- Practically identical application-level performance

### **Thank You!**

Contact Information

Peter Feeley

Micron Technology

pfeeley@micron.com

208-363-2693