### <u>A design method for the automated layout of</u> <u>control logic for FLASH memory</u>

## Kevin Steptoe Jeremy Birch Pulsic Ltd

# FlashMemory

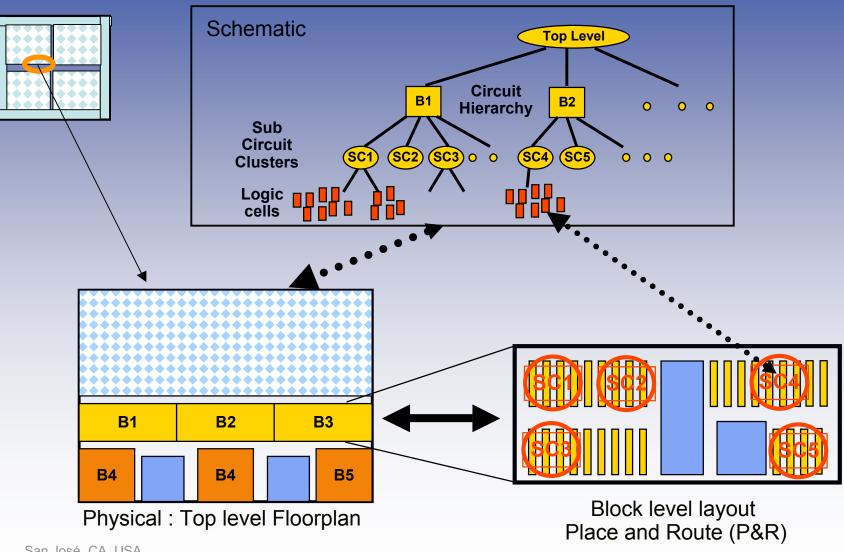

# Key Issues for layout of peripheral logic for FLASH

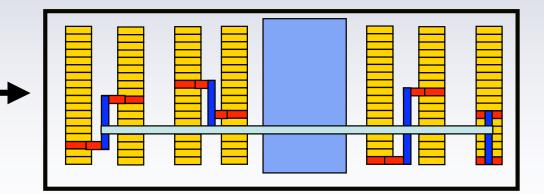

Memory Cell Arrays

Input/Output I/O Driver circuitry and pads

Area remaining to place and connect the peripheral controlling logic devices

- Characteristics and requirements for peripheral logic layout for FLASH

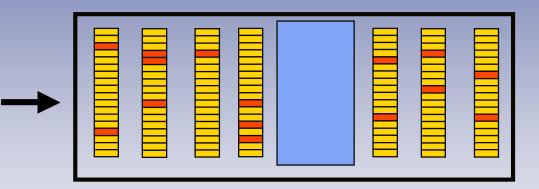

- Long and narrow aspect ratios of layout regions.

- Need for control of specific layers (e.g high resistive layers)

- Automation for low number of routing layers (e.g. 1-2 layer)

- For area performance and yield very specific placement and routing styles are required.

- nm process nodes are driving requirement for increased automation for productivity.

- Standard ASIC technology inappropriate and difficult to control to achieve required results.

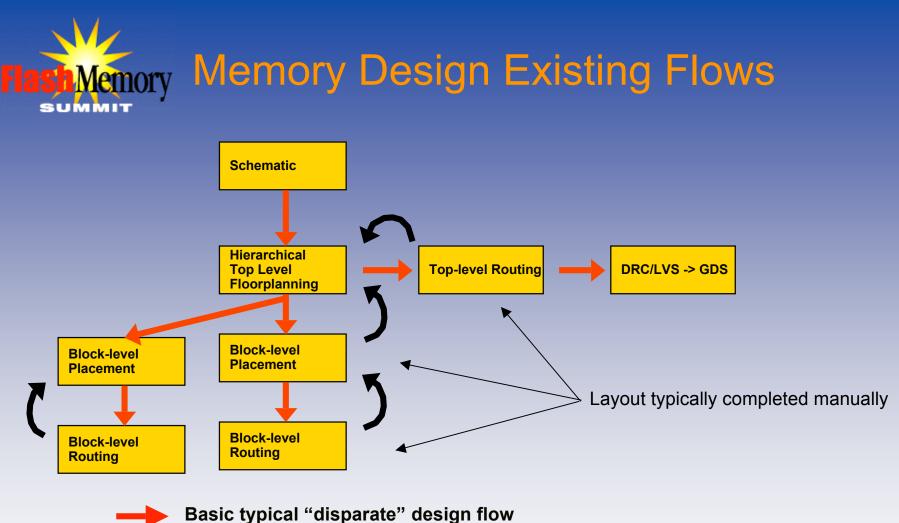

# Layout of Peripheral Logic – Objective is to physically place and connect logic cells

SUMMIT

- Busic typical disputate design new

- Needed 2 way flow with good feedback loop between tools

#### **Conclusion: Integrated and automated solution required**

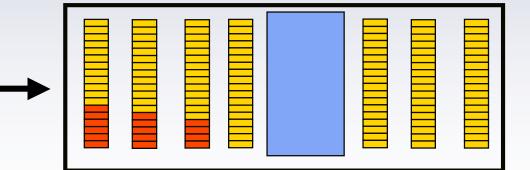

# **Block Level Placement (1)**

- Objective to place logic cells in Clusters

- Maintain hierarchical sub-circuit clusters

Placement WITHOUT clustering of subcircuits will result in longer net lengths & lower performance

Placement WITH clustering of subcircuit will result in shorter net lengths & increased performance

August 2006

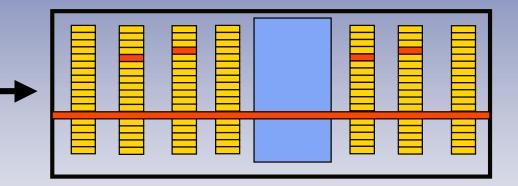

### **Block-Level Placement (2)**

#### Pre-Routing aware placement

Without pre-routing awareness – critical net lengths can be unacceptably long

Placement that is Pre-routing aware will minimize total net length

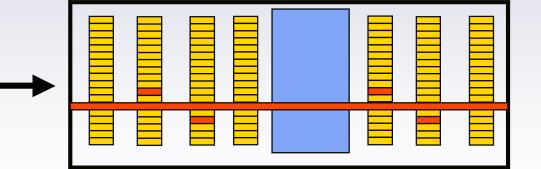

## **Block-Level Routing**

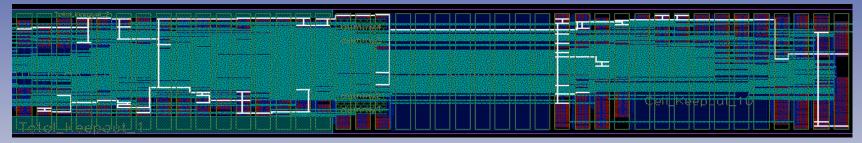

Normal autorouting approach will not achieve required results

Normal autoroute may min-connect the nets and be DRC correct – ––– but with more bends & segments

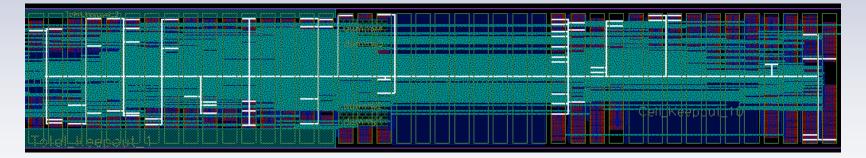

Spine & stitch route can achieve minimal bends and length to provide optimum performance & minimal area and still san meet all DRC's

August 2006

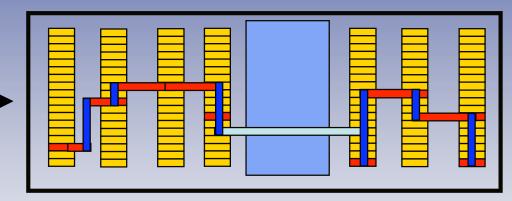

#### Without Methodology

#### With Methodology

Automation of the layout of peripheral logic is possible with a dedicated methodology involving specialised; floorplanning, placement and routing

- Integration of floorplanning together with placement and routing is mandatory

- Dedicated placement strategies are required for optimal results

- Cluster placement

- Routing aware placement

- Specialised routing techniques deliver smallest area, highest yield and best performance

- Shape based routing

- Spine and Stitch routing

- DFM aware routing