## An Introduction to Emerging Memory Technologies

Greg Komoto Manager, Strategic Planning Flash Memory Group Intel Corporation Email: greg.l.komoto@intel.com

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS and TECHNOLOGY. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

#### INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

- Intel may make changes to specifications and product descriptions at any time, without notice. This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

- Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained

from:

**Intel Corporation**

www.intel.com

or call 1-800-548-4725

Intel, and the Intel logo, Intel StrataFlash, and ETOX are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others. Copyright © 2007, Intel Corporation

- Overview of Emerging Memory Alternatives

- Near Term Candidates

- Longer Term, Litho Defined Candidates

- Non Litho Defined Candidates

- Conclusions

### Overview of Emerging Memory Alternatives

- Near Term Candidates

- Longer Term, Litho Defined Candidates

- Non Litho Defined Candidates

- Conclusions

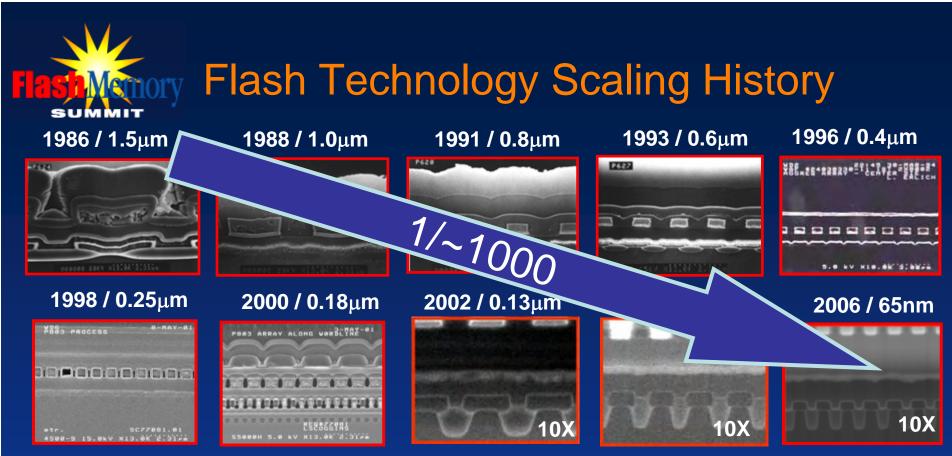

**Volume Production Year / Technology Generation**

Source: Intel

- Flash Invented in mid 1980's

- NOR flash evolved from EPROM

- NAND started as poly-poly erase cell later evolving to present structure

- ~20 years & 10 Generations of High Volume Production

- 8+ years & 5 Generations of MLC: 2bit / cell

|                           | Today                            | Тотоггом                                                       | Future                                                                          |  |

|---------------------------|----------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|--|

|                           | Evolutionary<br>SRAM             | Floating Trap<br>Metal Gate<br>Nano Dot<br>Barrier Engineering | Multi Layer 3D<br>3D Gate                                                       |  |

|                           | <i>Emerging<br/>Alternatives</i> | FeRAM<br>MRAM<br>PCM                                           | Multilayer 3D<br>RRAM<br>Bridging/Ionic<br>Molecular<br>Probe Storage<br>e-Beam |  |

| Focus of Today's Tutorial |                                  |                                                                |                                                                                 |  |

- Overview of Emerging Memory Alternatives

- → Near Term Candidates

- Longer Term, Litho Defined Candidates

- Non Litho Defined Candidates

- For Further Study

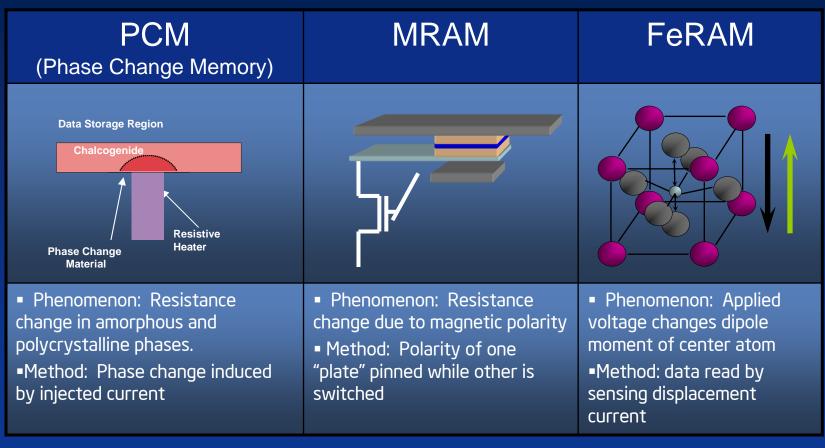

### **Key Attributes**

- 1C + 1 Transistor

- Cell Area: 25F<sup>2</sup> shipping

- Cell Area: 12-15F<sup>2</sup> demonstrated

#### **Advantages**

- Fast R/W performance

- Low power operation

- **Bit alterable (no erase)**

#### Issues

- Scaling path <100 nm

- **Destructive read**

- Read & Write limited ( $1e^6 \rightarrow$  $1e^{10}$ )

E<sub>App</sub> E<sub>Film</sub>

No path to flash/dram level costs

**Applied Electric Field** Moves Center Atom

> Perovskite Crystal Unit Cell PZT (PbO,ZrO<sub>2</sub>, TiO<sub>2</sub>) Lead-Zirconate-Titanate

Tetra/Pentavalent Atom

Di/Monovalent Metal Atoms

#### Non- Linear FRAM Capacitor

Top Electrode

PZT Film Polarized

#### **Bottom Electrode**

$\overrightarrow{\mathsf{E}}_{\mathsf{Net}} = \overrightarrow{\mathsf{E}}_{\mathsf{App}} - \overrightarrow{\mathsf{E}}_{\mathsf{Film}}$

**Key Attributes**

- 1MTJ + 1 Transistor

- Cell Area: 35F<sup>2</sup> shipping (Toggle)

- Cell Area: 6F<sup>2</sup> theoretical (STT)

#### **Advantages**

- "Unlimited" R/W endurance

- Fast R/W latency (<35 ns)</li>

- Bit alterable (no erase)

#### Issues

- Scaling path

- Write disturbs, power

- New materials, CMOS compatibility

- No path to flash/dram level costs

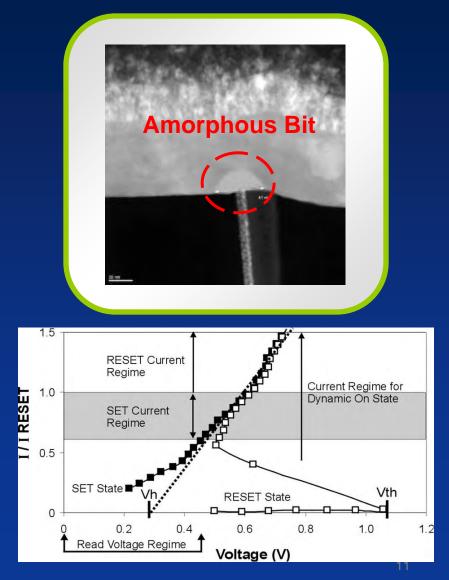

# Phase Change Memory (PCM)

#### **Key Attributes**

- IR + 1 select

- Cell Area: 5.5-12F2 sampling

- Cell Area: <6F2 demonstrated</p>

#### Advantages

- Clear scaling path to <20 nm</li>

- Ease of CMOS integration

- Fast, "unlimited" read

- Bit alterable (no erase)

#### Issues

- Write endurance limited: 1e6 to 1e12

- Write latency vs. DRAM

## Emerging Alternative Memory Attribute Comparison

| Key Metrics             | РСМ                                                         | MRAM                        | FeRAM                                                |

|-------------------------|-------------------------------------------------------------|-----------------------------|------------------------------------------------------|

| Cell Size               | ~SBC NOR/NAND<br>(5.5-12F <sup>2</sup> → <5F <sup>2</sup> ) | Larger<br>(35 F² → 6-16F²)  | Largest<br>(32F <sup>2</sup> → 12-15F <sup>2</sup> ) |

| <b>CMOS</b> Integration | Good                                                        | Fair to Poor                | Fair                                                 |

| Scaling                 | Excellent                                                   | Fair: current, materials    | Poor: materials,<br>3D                               |

| Read Latency            | Fast, ~NOR                                                  | Fastest, ~ xRAM             | Fast, ~NOR                                           |

| Write Speed/Power       | ~Flash → Higher                                             | Fastest latency, high power | Fast – RAM like                                      |

| Bit Alterable?          | Yes                                                         | Yes                         | Yes                                                  |

| Read Endurance          | Unlimited                                                   | Unlimited                   | Limited                                              |

| Write Endurance         | High                                                        | Unlimited                   | Higher                                               |

| Logic Integration       | Easiest                                                     | Harder                      | Easier                                               |

| Application Reach       | Flash + Most RAM +<br>Embedded Memory                       | Embedded/Cache<br>Memory    | Embedded<br>Memory                                   |

Source: Intel

- Overview of Emerging Memory Alternatives

- Near Term Candidates

- → Longer Term, Litho Defined Candidates

- Non Litho Defined Candidates

- For Further Study

## Future Research Trend: Extending in Multiple Layers

Source: Intel

R&D Example (circa 2003): Read/Write Eight Layer Memory using Ferroelectric Polymer

- Litho defined memories seeking to extend scaling in vertical dimension

- Industry work on everything from NAND to polymer

- Ideal Effective Cell Area: Z = 4F<sup>2</sup> / y Where y = # of layers

- Challenge is manufacturing cost of multiple layers

### Other NVM Candidates in the Longer Term Research & Discovery Phase (Part 1 of 2)

| Material                 | Structure                                                                         | Description                                                              | Effect                                                |  |  |

|--------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------|--|--|

| RRAM                     |                                                                                   | Resistance<br>change in CMO<br>(usually<br>crosspoint and<br>multilayer) | Resistance change<br>based on an applied<br>field     |  |  |

| Ferroelectric<br>Polymer | Word line<br>Word line<br>Polymer Layer<br>Bit line<br>Polymer Layer<br>Word line | Cross-point, multi-<br>layer capacitive<br>storage in<br>Polymer         | Change in capacitance<br>based on an applied<br>field |  |  |

| Resistive<br>Polymer     |                                                                                   | Cross-point, multi-<br>layer resistive<br>storage in<br>Polymer          | Change in resistance<br>based on an applied<br>field  |  |  |

| Source: Intel            |                                                                                   |                                                                          |                                                       |  |  |

Intel

### Other NVM Candidates in the Longer Term Research & Discovery Phase (Part 2 of 2)

| Material                      | Structure                                     | Description                                   | Effect                                                    |

|-------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|

| Programmable<br>Metallization |                                               | Silver Dissolved in<br>Chalcogenide           | Field Driven<br>"Electroplating"                          |

| Carbon<br>Nanotube            |                                               | Cross Point Array<br>of Nanotubes<br>Switches | Electrostatic Attraction<br>+ Van der Waals<br>Adhesion   |

|                               | Carbon<br>Nanotube                            | CNT as Circuit<br>Element                     | CNTs as replacement structure                             |

| Molecular                     | Image Courtesy of the University<br>of Sydney | Molecules in<br>CrossPoint Array              | Voltage Driven Change<br>in electronic states in<br>Redox |

\*Other names and brands may be claimed as the property of others.

Source: Intel

- Overview of Emerging Memory Alternatives

- Near Term Candidates

- Longer Term, Litho Defined Candidates

- Non Litho Defined Candidates

- For Further Study

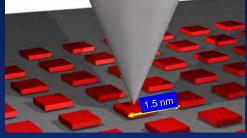

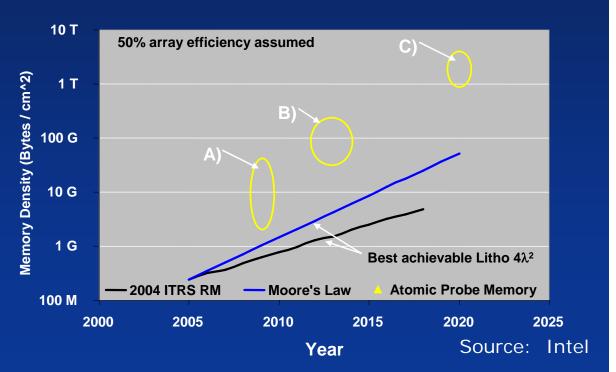

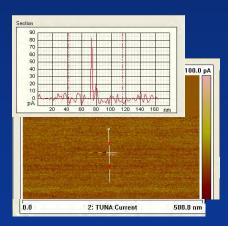

### Seek & Scan Probe Storage

Cartoon of Nano Dimension Atomic Level Probe contacting single molecule memory

Image Courtesy of the University of Sydney

Best achievable memory density projections over time:

- A) IBM Millipede today

- B) Improved storage media

- C) Full molecular memory storage capability

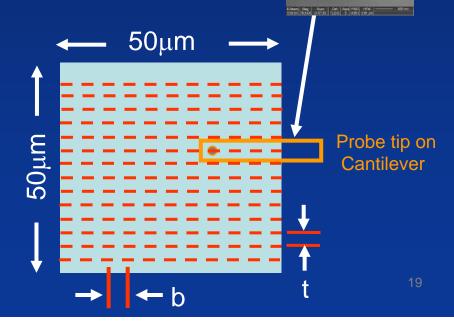

### Seek & Scan Probe (SSP):

- •MEMs device with nanopositioned probe tips

- •Employs alternative storage media

- •Molecular level storage is ultimate goal

\*Other names and brands may be claimed as the property of others.

- Bit size: Determined by Media & Tip interactions

- Track Pitch/Position: Determined by Nano-positioning

- Motor resolution < 1nm resolution reported

- Tip Scaling: Determined by tip field focusing

- Tip shape & media fields & current distribution

Probe tip

Source: Intel

- Overview of Emerging Memory Alternatives

- Near Term Candidates

- Longer Term, Litho Defined Candidates

- Non Litho Defined Candidates

- →Conclusions

- Flash memory technology working to address scaling challenges

- New memory technology is rare

- Last to break beyond a niche was flash ~20 years ago

- Phase Change Memory is the most promising of near-term candidates

- Multi-level, 3D and MEMS devices hold most promise for the future

## **Risk Factors**

This presentation contains forward-looking statements that involve a number of risks and uncertainties. These statements do not reflect the potential impact of any mergers, acquisitions, divestitures, investments or other similar transactions that may be completed in the future. The information presented is accurate only as of today's date and will not be updated. In addition to any factors discussed in the presentation, the important factors that could cause actual results to differ materially include the following: Intel operates in intensely competitive industries that are characterized by a high percentage of costs that are fixed or difficult to reduce in the short term, significant pricing pressures, and product demand that is highly variable and difficult to forecast. Additionally, Intel is in the process of transitioning to its next generation of products on 45 nm process technology, and there could be execution issues associated with these changes, including product defects and errata along with lower than anticipated manufacturing yields. Revenue and the gross margin percentage are affected by the timing of new Intel product introductions and the demand for and market acceptance of Intel's products; actions taken by Intel's competitors, including product offerings and introductions, marketing programs and pricing pressures and Intel's response to such actions; Intel's ability to respond quickly to technological developments and to incorporate new features into its products; and the availability of sufficient components from suppliers to meet demand. Factors that could cause demand to be different from Intel's expectations include customer acceptance of Intel's and competitors' products; changes in customer order patterns, including order cancellations; changes in the level of inventory at customers; and changes in business and economic conditions. The gross margin percentage could vary significantly from expectations based on changes in revenue levels; product mix and pricing; capacity utilization; variations in inventory valuation, including variations related to the timing of qualifying products for sale; excess or obsolete inventory; manufacturing yields; changes in unit costs; impairments of long-lived assets, including manufacturing, assembly/test and intangible assets; and the timing and execution of the manufacturing ramp and associated costs, including start-up costs. Expenses, particularly certain marketing and compensation expenses, vary depending on the level of demand for Intel's products, the level of revenue and profits, and impairments of long-lived assets. Intel is in the midst of a structure and efficiency program that is resulting in several actions that could have an impact on expected expense levels and gross margin. Intel's results could be affected by the amount, type, and valuation of share-based awards granted as well as the amount of awards cancelled due to employee turnover and the timing of award exercises by employees. Intel's results could be impacted by unexpected economic, social, political and physical/infrastructure conditions in the countries in which Intel, its customers or its suppliers operate, including military conflict and other security risks, natural disasters, infrastructure disruptions, health concerns and fluctuations in currency exchange rates. Intel's results could be affected by adverse effects associated with product defects and errata (deviations from published specifications), and by litigation or regulatory matters involving intellectual property, stockholder, consumer, antitrust and other issues, such as the litigation and regulatory matters described in Intel's SEC reports. A detailed discussion of these and other factors that could affect Intel's results is included in Intel's SEC filings, including the report on Form 10-Q for the quarter ended June 30, 2007.