Memory Management: So Complex it's Easy

Amir Fridman Director, Marketing Strategy, MHV division SanDisk amir.fridman@SanDisk.com

### Agenda

- NAND Flash Market Overview

- NAND technology challenges

- What is expected in next generation?

- How to bridge the GAP?

- Summary

# **NAND flash market overview**

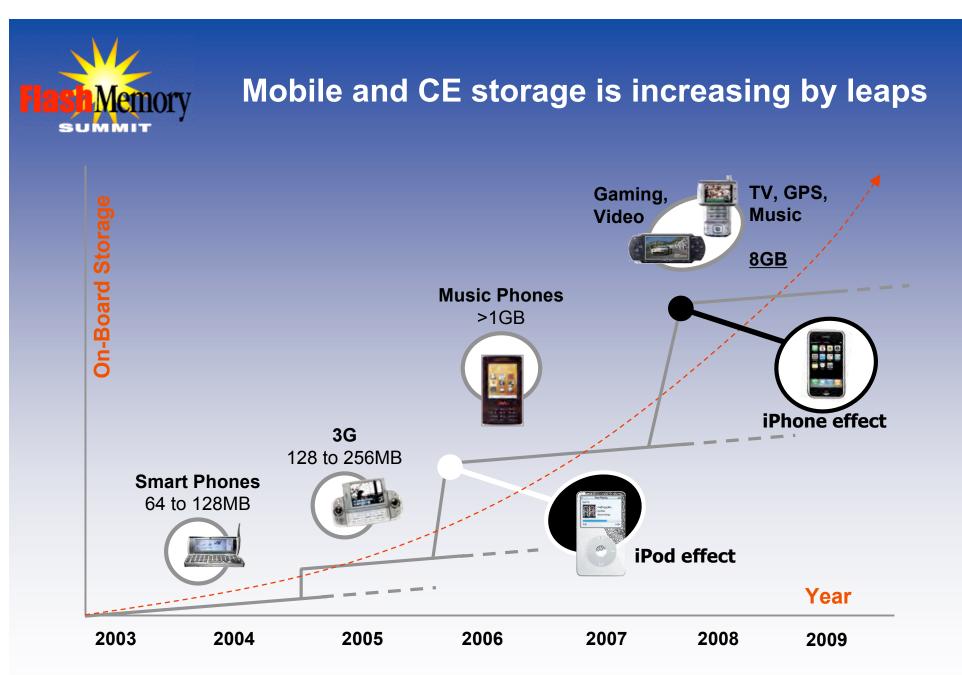

### **Explosion in NAND based devices**

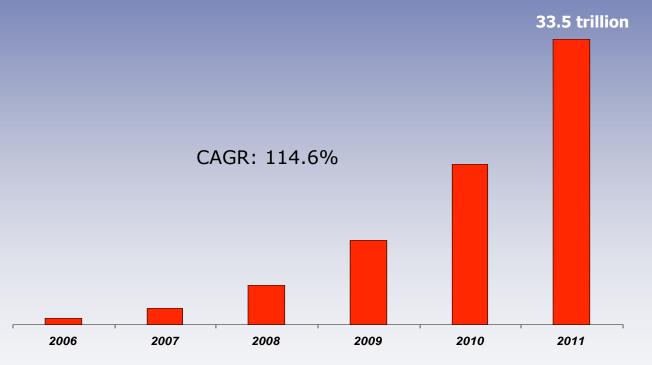

**Worldwide NAND Flash Shipments, 2006-2011**

#### (Millions of Megabytes)

Source – Gartner, Inc., Memory, Worldwide, 2006-2011 (2Q07 Update) By Richard Gordon, Andrew Norwood, Joseph Unsworth and Clare Hirst

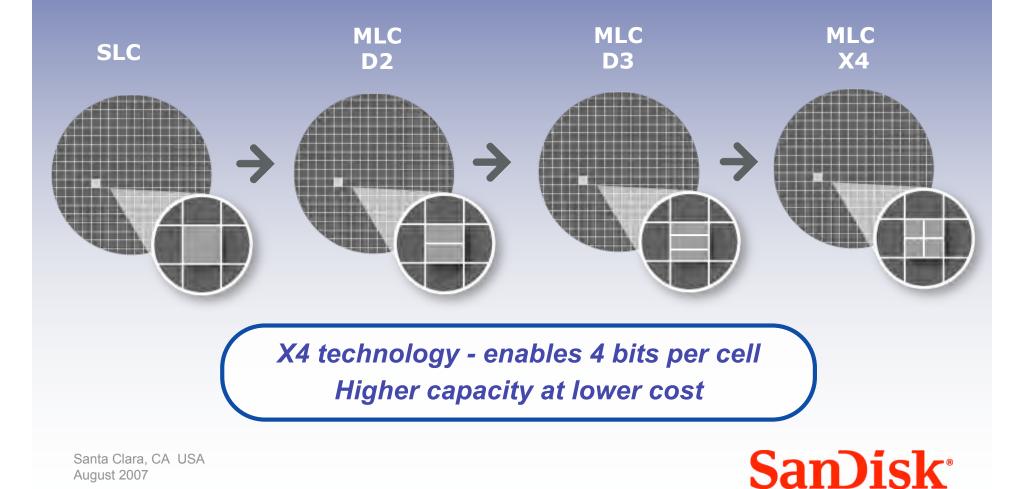

### Moving to advanced technology Enabling high-capacity

# NAND technology challenges

- MLC NAND industry is characterized by:

- Incompatibility between vendors

- Incompatibility between generations

- MLC Flash optimizes cost, but compromises systems' performance and reliability

- Different applications require different performance and reliability of storage

Santa Clara, CA USA August 2007 SanDisk<sup>®</sup>

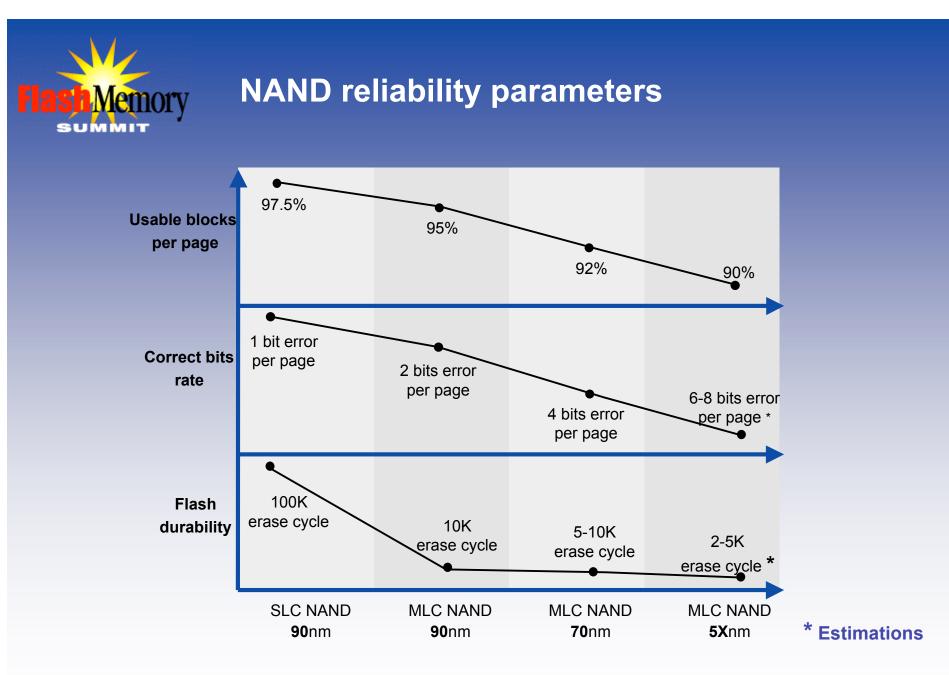

- NAND is currently the most dense FLASH technology – though it takes its toll by having to deal with:

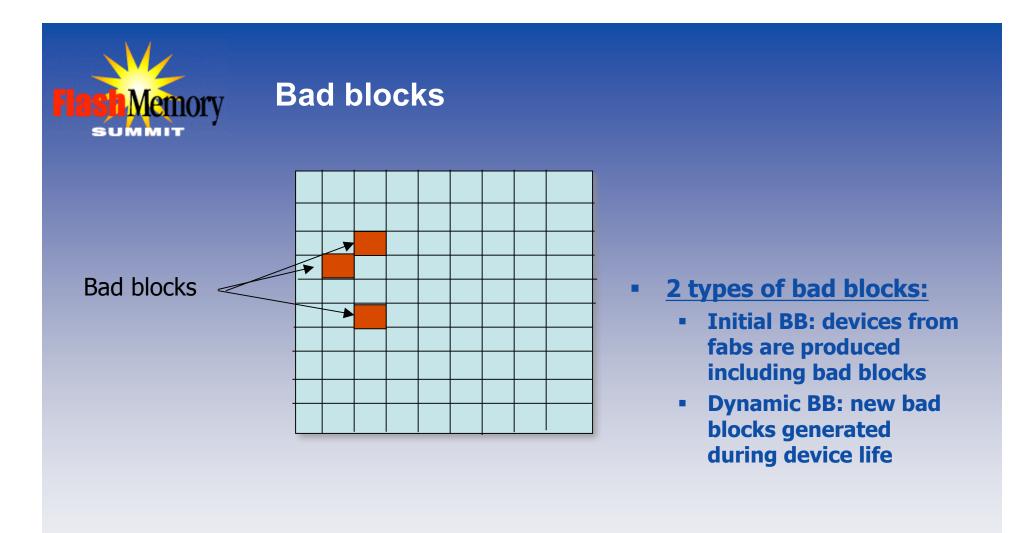

- Bad Block

- Endurance

- Bit Errors

- Data retention

- Bit pairing & Power failures

Advanced flash management SW technology detect and isolates initial and dynamic bad blocks

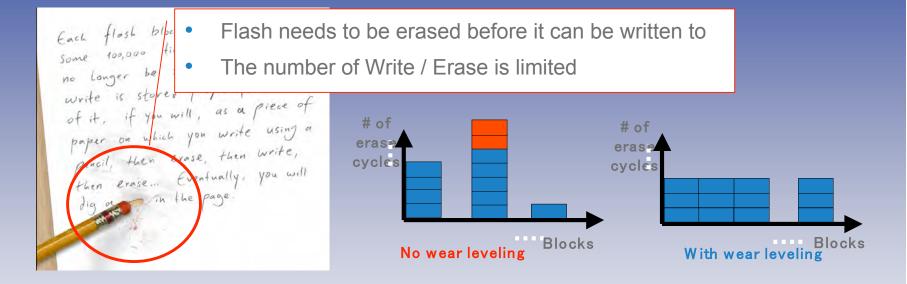

## Limited Write / Erase Cycle & Wear Leveling

Advanced flash management technology provides dynamic and static wear leveling:

- <u>Dynamic</u> wear leveling: updated files

- <u>Static wear</u> leveling: updated and static files

Santa Clara, CA USA August 2007

SUMMIT

#### Basic issues

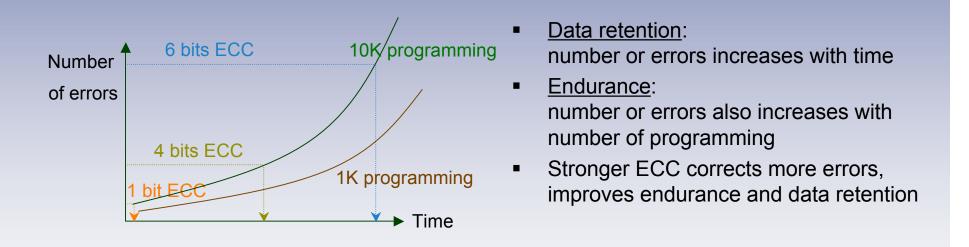

- <u>Read disturb</u> Many reads causes some of the cells to be programmed deeper (change logical states)

- <u>Program disturb</u> The content of the cell is changed due to programming of neighbor cells

- <u>Data Retention</u> The charge in the cells leaks causing change of logical state

- Requirements

- **<u>SLC</u>** single bit ECC shifting to 2 bits

- **MLC** 4 bits ECC shifting to 6-8 bits in 50nm and higher in 4Xnm

#### EDC/ECC beyond current flash needs enables faster migration to future technologies

### Data retention, endurance & EDC/ECC

- **Data retention** defines how long the data programmed remains valid

- Endurance defines how many times data can be programmed

- There is a clear <u>correlation</u> between those 2 parameters:

#### Stronger EDC/ECC beyond required in specifications, can increases device endurance & life span

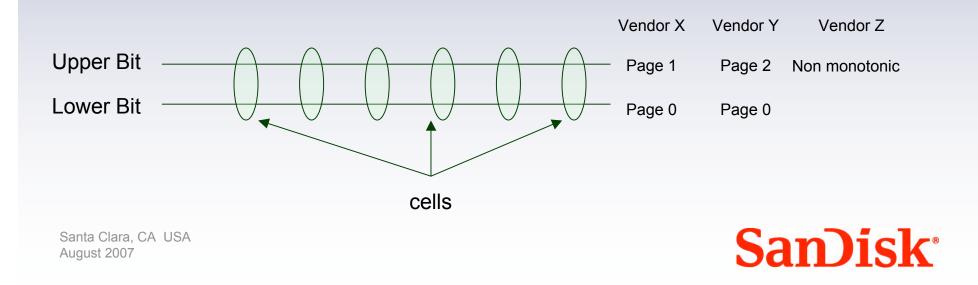

### **Bit pairing**

- In MLC product each cell includes 2 bits

- However in most cases each bit belongs to different logical page

- The arrangement is different from vendor to vendor

- The arrangement is different from generation to generation

- The arrangement is usually not documented in data sheets

- The knowledge of logical to physical is a must in order to handle power failure correctly

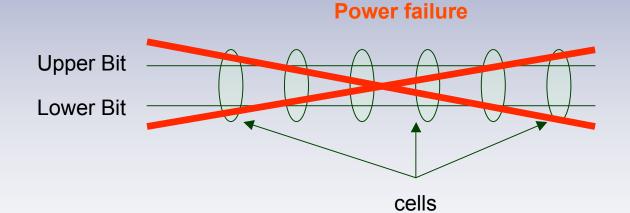

### Bit pairing impact on power failure

#### Consider the following case

- Lower page was written

- Later (1 day after for example) upper page is written

- During upper page program power failure occurs

- Impact: Data in lower page, considered safe, is lost.

Advanced flash management technology has optimized power failure protection, including bit pairing

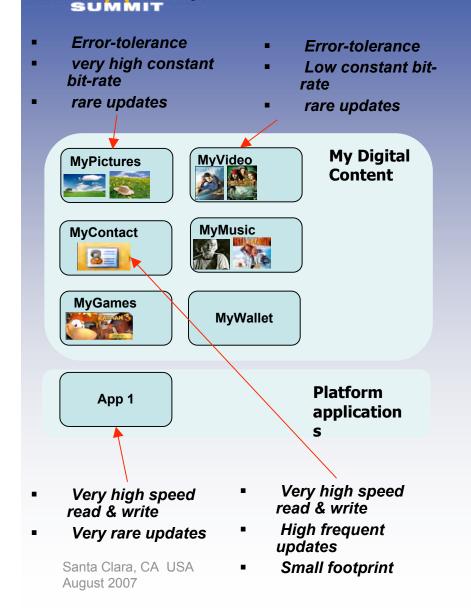

### **Different Applications = Different requirements**

- Content types & applications are treated equally with today's storage technology, regardless of their intrinsic requirements

- Performance

- Reliability

- Security

- Traditional design is challenged with the worst-case of all applications' requirements in terms of performances, data retention, endurance etc..

### **Booting from MLC Flash Disk**

# How fast can the market move from this?

#### To this!!!

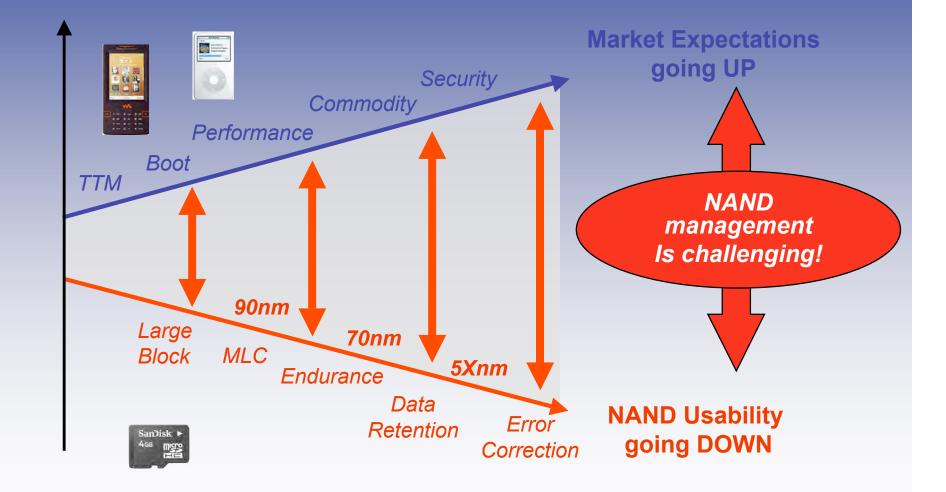

### Flash Storage Conflicting Trends

Santa Clara, CA USA August 2007 SanDisk

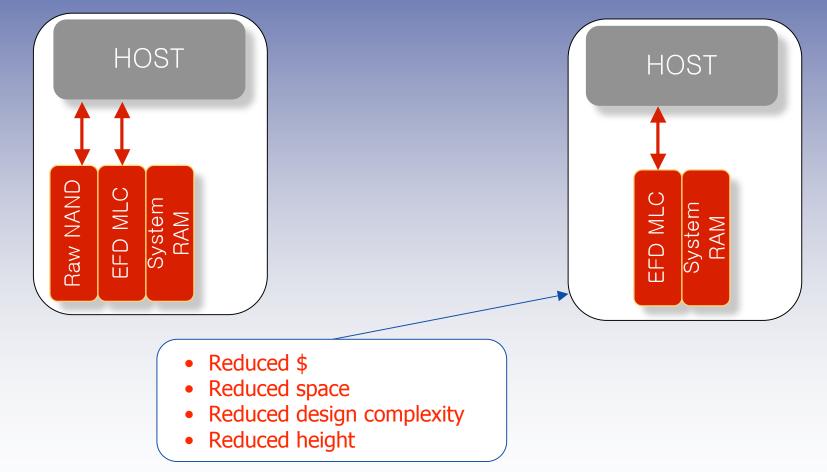

### **Embedded Flash Drive (EFD) Evolution**

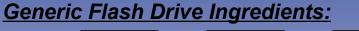

#### Legacy Solutions – Flash Management on Host

Example: Raw SLC NAND:

#### Embedded Flash Drive – Flash Management on Drive

Solving software complexity issues

- Flash manufacturers target is to move to new process & MLC based technologies as fast as possible!

- Embedded Flash Drive with advanced flash management technology solves

- NAND reliability limitations

- Power failure protection

- Fast migration to MLC latest process

**EFD** enables advanced MLC technology usage for boot and storage

# **Summary**

- NAND flash is the fastest growing memory segment

- Mobile and CE markets leads the flash consumption growth

- NAND market migrating from SLC to MLC technology and future X4

- MLC optimizes cost, but compromises systems' performance and reliability

- Migration to advance NAND technology becomes more difficult and complex, hence puts in risk the introduction of new models

- Mobile handset manufacturers need to design flash storage solutions that overcome evolving NAND technology and challenges and support storage hungry applications

# Thank you