# Introduction to Flash Memory (T1A)

Jim Cooke (jcooke@micron.com)

Staff Architect and Technologist, Architecture Development Group Micron Technology, Inc.

- The basics of Flash and NAND

- Flash cell comparison

- NAND and NOR attributes and interface comparison

- Detailed operations

- Commands, address, and data operations

- Connecting NAND to a RISC or DSP processor

#### More NAND Flash device detail

- SLC vs. MLC

- All NAND devices are not created equal

- Architecture, features, and performance comparisons

- Performance bottlenecks

- ONFI and high-speed NAND introduction

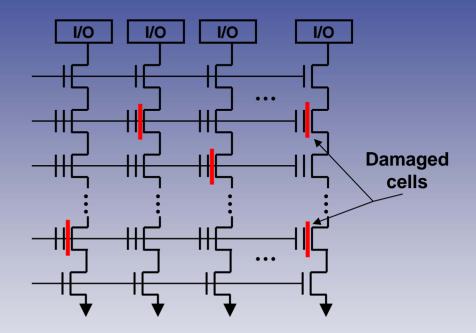

- NAND error modes

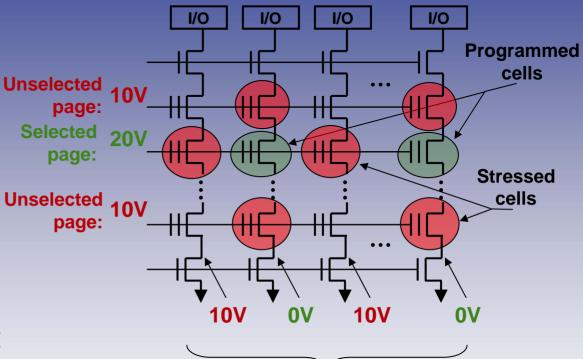

- Program disturb

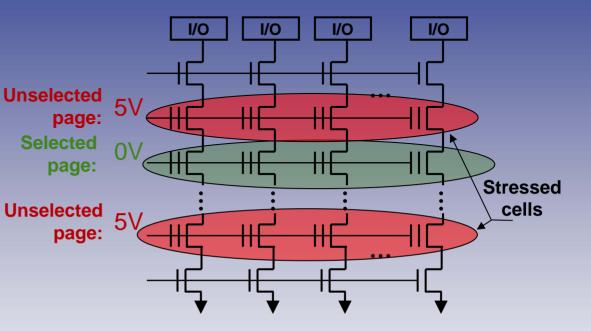

- Read disturb

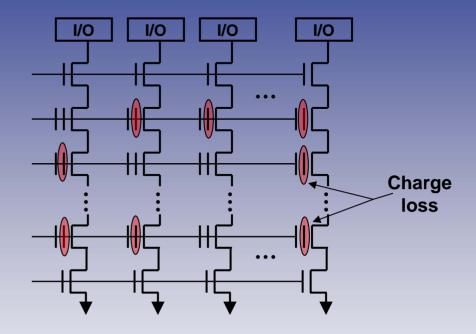

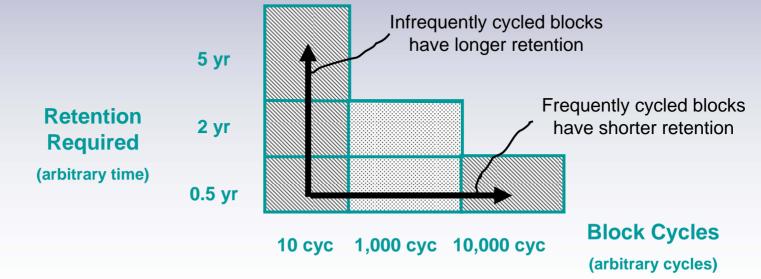

- Data retention

- Endurance

- Wear-leveling

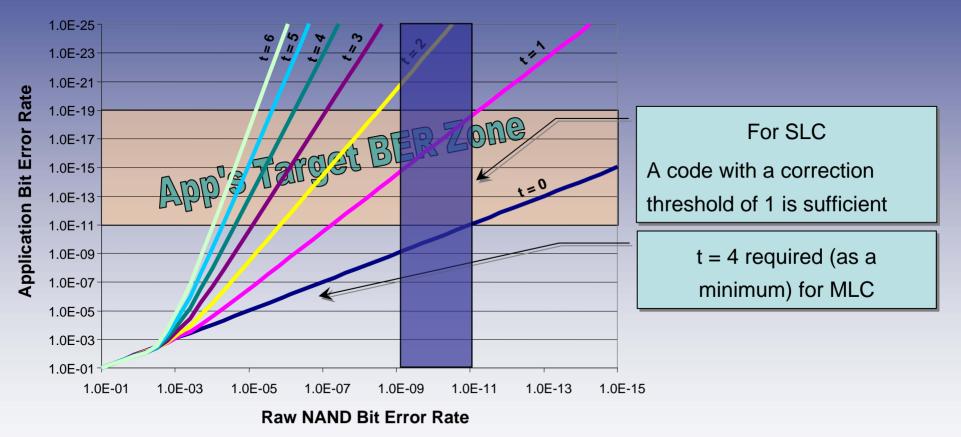

- ECC fixes almost everything

#### **A Quick Review of Flash Basics**

- Cell differences

- NAND attributes

- NAND vs. NOR

#### **Flash Basics**

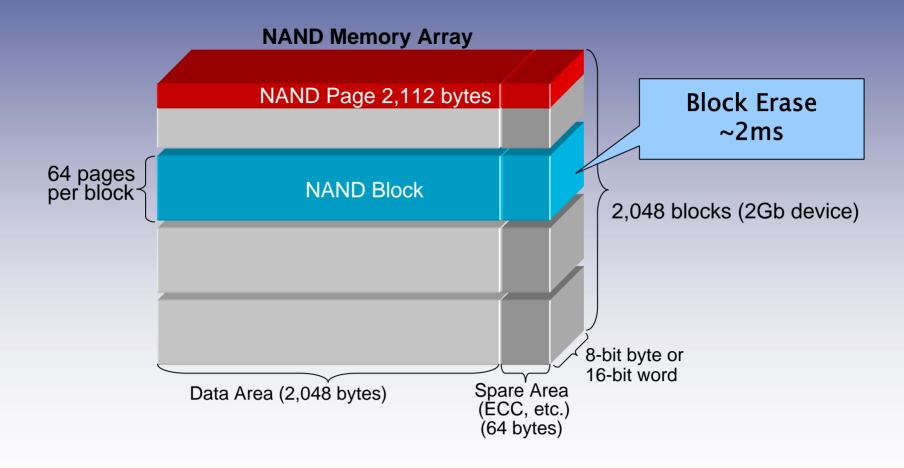

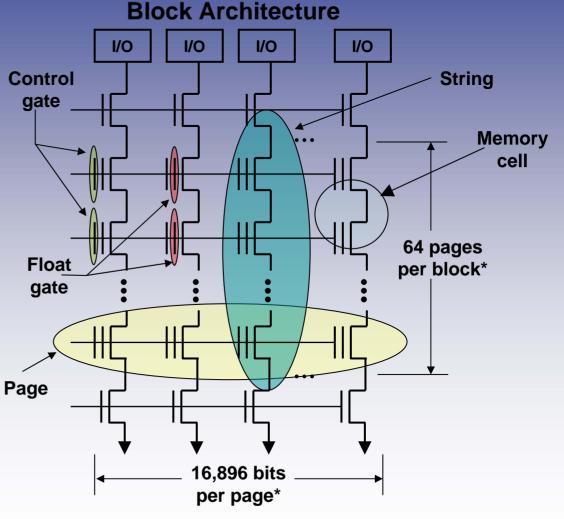

- Flash data is grouped into blocks, which are the smallest erasable entity

- Erasing a block sets all bits to "1" or bytes to FFh

- The programming operation changes erased bits from "1" to "0"

- The smallest entity that can be programmed is a bit

- While NAND cannot inherently perform random access, it is possible at the system level through shadowing

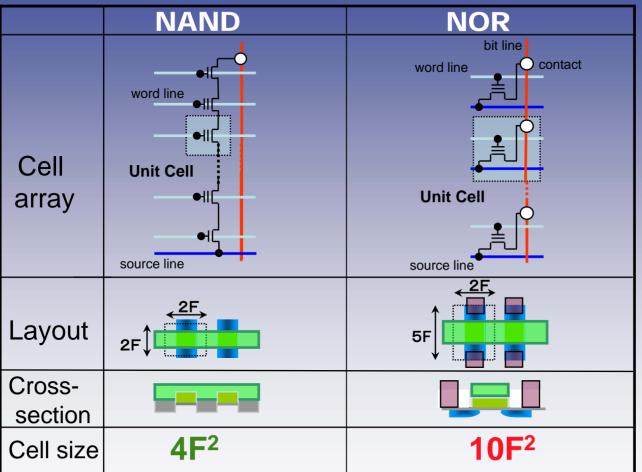

## Flash Memory Cell Comparison

• NAND Flash's small cell size enables high density and low cost

## **Basic NAND Attributes**

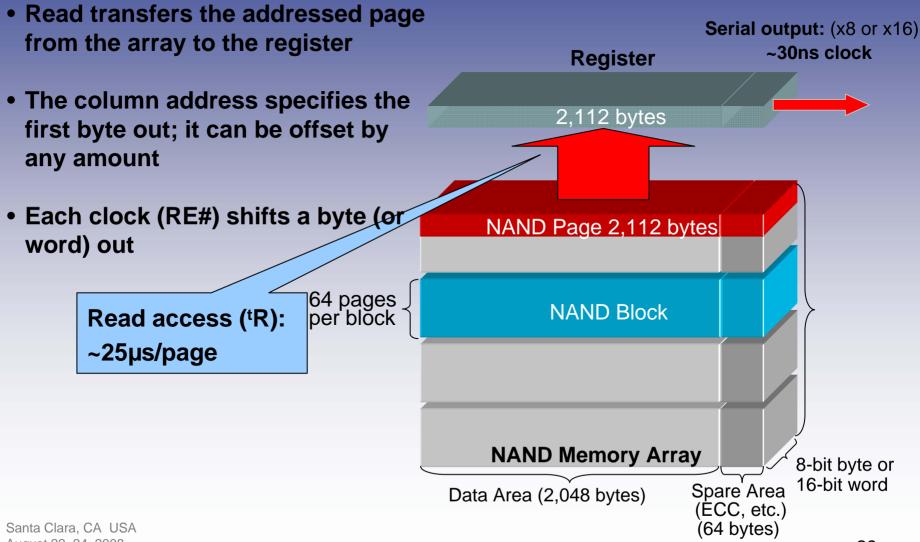

- NAND is very similar to a disk drive; it is sector-based (page-based) Flash and is well-suited for storage of sequential data (such as pictures, audio, and files)

- Like a disk drive, NAND is not well-suited for random access, such as executing code, although random access can be accomplished at the system level by shadowing the data to RAM (similar to what a PC does with BIOS)

- Like a disk drive, NAND devices have bad sectors or blocks and require management

- Like a disk drive, NAND requires error correction code (ECC)

- Unlike a disk drive, it is possible to wear out the NAND cell; with good wear-leveling, this is typically not an issue

## **Basic NAND Attributes**

- NAND is available in large capacities and is the lowest cost Flash memory available today

- NAND is finding its way into many embedded applications and is used in virtually all removable cards

- USB cards

SD secure digital

- Memory stick

CF compact Flash

- MMC multimedia card

- Multiplexed interface provides similar pinout over all devices

- x8 signal pinout has not changed from 64Mb pinout

- x8 devices are used mostly in high capacity (3.3V) consumer applications; the x16 devices are mostly used in embedded (1.8V) applications

# **Basic NAND/NOR Comparison**

#### NAND

- Advantages

- Fast writes

- Fast erases

- Disadvantages

- Slow random access

- Byte writes difficult

- Applications

- File (disk) applications

- Voice, data, video recorder

- Any large sequential data

#### NOR

- Advantages

- Random access

- Byte writes possible

- Disadvantages

- Slow writes

- Slow erase

- Applications

- Replacement of EPROM

- Execute directly from nonvolatile memory

### Flash Memory Comparison

|   | Characteristic                                                         | NAND Flash<br>MT29F2G08                                                                                                 | NOR<br>MT28F128J3 |  |  |  |  |  |  |  |

|---|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|--|--|--|

|   | Random access read                                                     | 25µs (first byte)<br>0.03µs each for<br>remaining 2,111 bytes                                                           | 0.12µs            |  |  |  |  |  |  |  |

|   | Sustained read                                                         | 23 MB/s (x8) or                                                                                                         | 20.5 MB/s (x8) or |  |  |  |  |  |  |  |

|   | speed (sector basis)                                                   | 37 MB/s (x16)                                                                                                           | 41 MB/s (x16)     |  |  |  |  |  |  |  |

|   | Random write speed                                                     | ~300µs/2,112 bytes                                                                                                      | 180µs/32 bytes    |  |  |  |  |  |  |  |

|   | Sustained write speed (sector basis)                                   | 5 MB/s                                                                                                                  | 0.178 MB/s        |  |  |  |  |  |  |  |

|   | Erase block size                                                       | 128KB                                                                                                                   | 128KB             |  |  |  |  |  |  |  |

|   | Erase time per block<br>(typ)                                          | 2ms                                                                                                                     | 750ms             |  |  |  |  |  |  |  |

|   |                                                                        |                                                                                                                         |                   |  |  |  |  |  |  |  |

| Ą | NAND Flash is ideal for<br>data or image files; if<br>be shadowed to R | NOR Flash is ideal for<br>direct code execution (boot<br>code) although it still<br>needs to be shadowed (for<br>speed) |                   |  |  |  |  |  |  |  |

## Flash Interface Comparison

- NOR Flash

- Random-access interface typically composed of: -

- CE# chip enable

- WE# write enable

- OE# output enable

- D15-D0 data bus

- A20-A0 address bus

- WP# write protect

#### NAND Flash

- I/O device-type interface composed of:

- CE# chip enable

- WE# write enable

- RE# read enable

- CLE command latch enable

- ALE address latch enable

- I/O 7-0 data bus (I/O 15-0 for x16 parts)

41 pins

23 pins

(for x16)

- WP# write protect

- R/B# ready/busy

#### NAND Flash Physical Interface (TSOP 1)

| x16                                                                                                    | x8                                                                                                            |                                                                                                   |                                                                   |                                                                                                                                                     |                                                                                                                                                                                               | x8                                                                                                                                                                   | x16                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NC<br>NC<br>NC<br>NC<br>R/B#<br>RE#<br>NC<br>CE#<br>NC<br>Vcc<br>Vcc<br>Vcc<br>NC<br>CLE<br>ALE<br>WE# | NC<br>NC<br>NC<br>NC<br>R/B#<br>RE#<br>CE#<br>NC<br>CE#<br>NC<br>Vcc<br>Vcc<br>Vcc<br>NC<br>CLE<br>ALE<br>WE# | 1 ●<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | Pin Name<br>R/B#<br>RE#<br>CE#<br>CLE<br>ALE<br>WE#<br>WE#<br>WP# | Definition<br>Ready Busy<br>Read Enable (L)<br>Chip Enable (L)<br>Command Latch Enable<br>Address Latch Enable<br>Write Enable (L)<br>Write Protect | 48         47         46         45         44         43         42         41         40         39         38         37         36         35         34         33         32         31 | Vss <sup>2</sup><br>DNU<br>NC<br>I/O7<br>I/O6<br>I/O5<br>I/O4<br>NC<br>Vcc <sup>2</sup><br>DNU<br>Vcc<br>Vss<br>NC<br>Vcc <sup>2</sup><br>NC<br>I/O3<br>I/O3<br>I/O2 | Vss<br>I/O15<br>I/O14<br>I/O13<br>I/O7<br>I/O6<br>I/O5<br>I/O4<br>I/O12<br>Vcc<br>DNU<br>Vcc<br>Vss<br>NC<br>Vcc<br>I/O11<br>I/O3<br>I/O2 |

| WP#<br>NC                                                                                              | WP#<br>NC                                                                                                     | 19<br>20                                                                                          |                                                                   |                                                                                                                                                     | 30                                                                                                                                                                                            | I/O1<br>I/O0                                                                                                                                                         | I/O1<br>I/O0                                                                                                                              |

| NC<br>NC                                                                                               | NC<br>NC                                                                                                      | 21<br>22                                                                                          |                                                                   |                                                                                                                                                     | 28<br>27                                                                                                                                                                                      | NC<br>NC                                                                                                                                                             | I/O10<br>I/O9                                                                                                                             |

| NC<br>NC                                                                                               | NC<br>NC                                                                                                      | 22<br>23<br>24                                                                                    |                                                                   |                                                                                                                                                     | 26<br>25                                                                                                                                                                                      | DNU<br>Vss <sup>2</sup>                                                                                                                                              | I/O9<br>I/O8<br>Vss                                                                                                                       |

#### Indirect addressing enables no pinout changes among densities Note 2: Additional Vcc and Vss recommended for new PCB designs

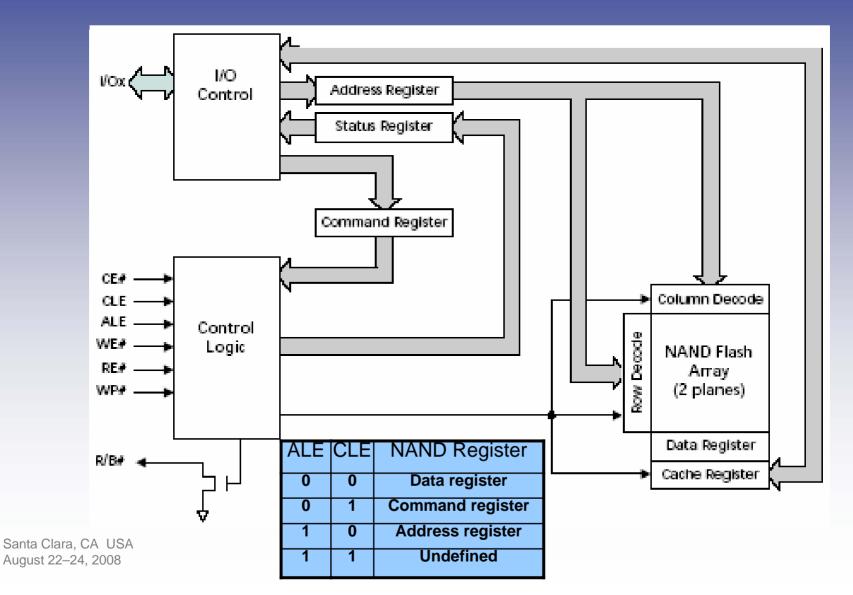

#### NAND Block Diagram

### **Detailed Operations**

Architecture Addressing Basic commands

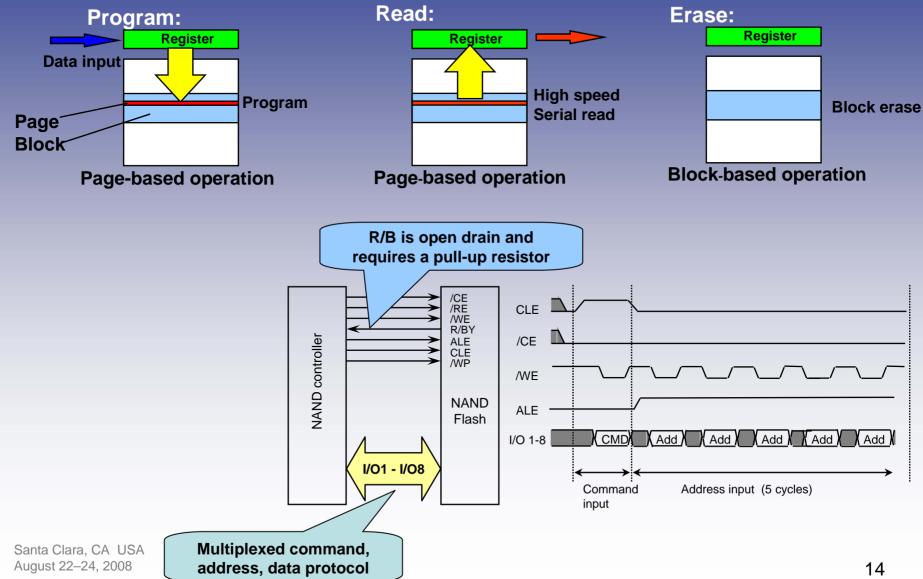

### **Basic NAND Flash Operations**

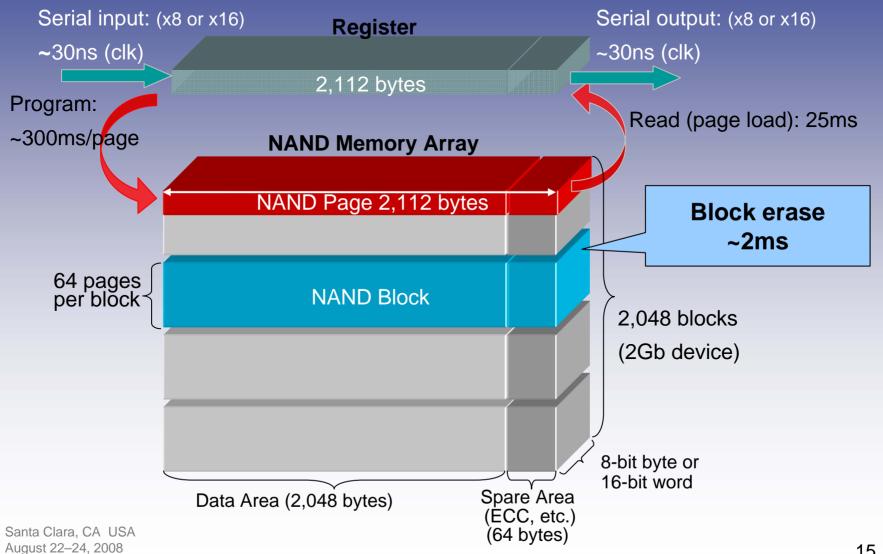

# **SLC NAND Flash Memory Diagram**

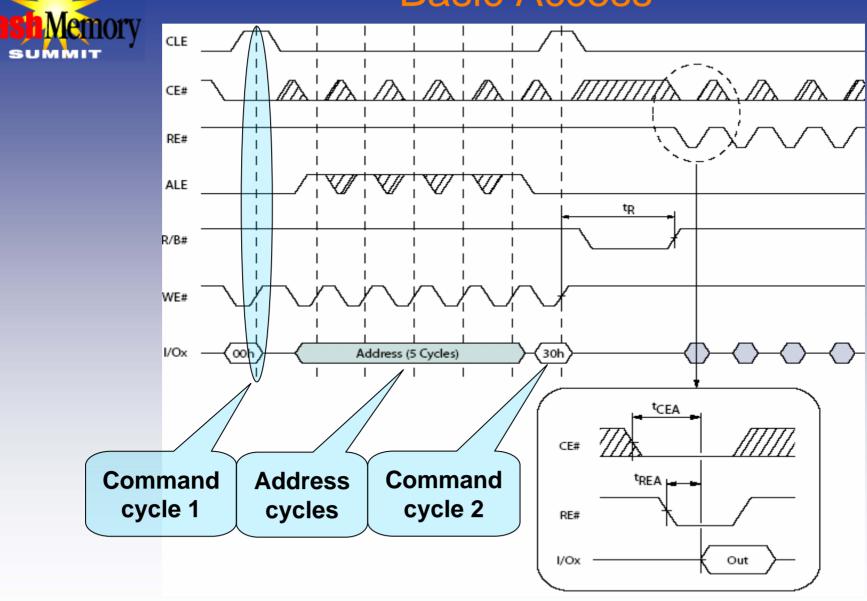

#### **Basic Access**

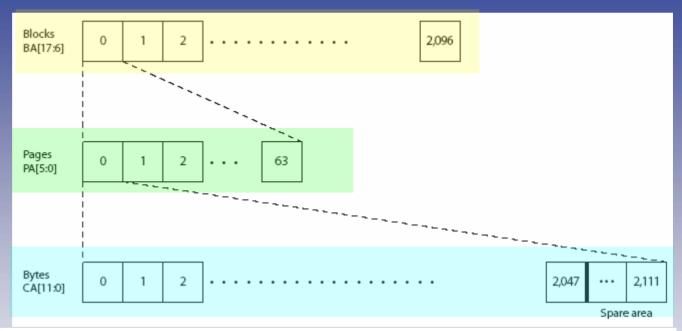

# Large-Block NAND Addressing

CAx = column address; RAx = row address.

| Cycle  | I/07 | I/06 | I/05 | I/04 | I/03 | I/02 | I/01              | I/00 |

|--------|------|------|------|------|------|------|-------------------|------|

| First  | CA7  | CA6  | CA5  | CA4  | CA3  | CA2  | CA1               | CA0  |

| Second | LOW  | LOW  | LOW  | LOW  | CA11 | CA10 | CA9               | CA8  |

| Third  | RA19 | RA18 | RA17 | RA16 | RA15 | RA14 | RA13              | RA12 |

| Fourth | RA27 | RA26 | RA25 | RA24 | RA23 | RA22 | RA21              | RA20 |

| Fifth  | LOW  | LOW  | LOW  | LOW  | LOW  | LOW  | RA29 <sup>1</sup> | RA28 |

Notes: 1. Die address boundary: 0 = 0 - 2Gb, 1 = 2Gb - 4Gb.

#### NAND Command List Standard 2Gb (256MB) NAND

| Command                         | Command<br>Cycle 1 | Number of<br>Address<br>Cycles | Data<br>Cycles<br>Required <sup>1</sup> | Command<br>Cycle 2 | Valid<br>During<br>Busy |

|---------------------------------|--------------------|--------------------------------|-----------------------------------------|--------------------|-------------------------|

| PAGE READ                       | 00h                | 5                              | No                                      | 30h                | No                      |

| PAGE READ CACHE MODE START      | 31h                | —                              | No                                      | —                  | No                      |

| PAGE READ CACHE MODE START LAST | 3Fh                | —                              | No                                      | —                  | No                      |

| READ for INTERNAL DATA MOVE     | 00h                | 5                              | No                                      | 35h                | No                      |

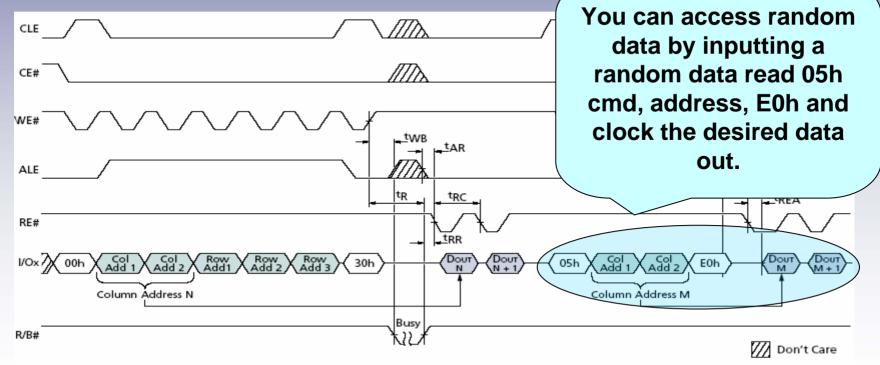

| RANDOM DATA READ                | 05h                | 2                              | No                                      | E0h                | No                      |

| READ ID                         | 90h                | 1                              | No                                      | —                  | No                      |

| READ STATUS                     | 70h                | —                              | No                                      | —                  | Yes                     |

| PROGRAM PAGE                    | 80h                | 5                              | Yes                                     | 10h                | No                      |

| PROGRAM PAGE CACHE MODE         | 80h                | 5                              | Yes                                     | 15h                | No                      |

| PROGRAM for INTERNAL DATA MOVE  | 85h                | 5                              | Optional                                | 10h                | No                      |

| RANDOM DATA INPUT               | 85h                | 2                              | Yes                                     | —                  | No                      |

| BLOCK ERASE                     | 60h                | 3                              | No                                      | D0h                | No                      |

| RESET                           | FFh                | —                              | No                                      |                    | Yes                     |

For ease of presentation:

**Basic command**

**Advanced command**

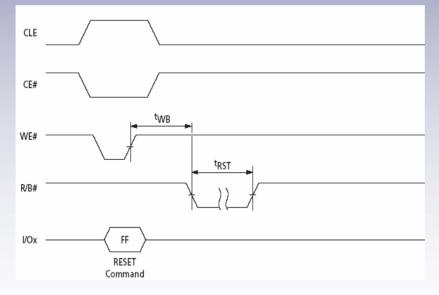

### **Reset Operation**

| Command                         | Command<br>Cycle 1 | Number of<br>Address<br>Cycles | Data<br>Cycles<br>Required <sup>1</sup> | Command<br>Cycle 2 | Valid<br>During<br>Busy |

|---------------------------------|--------------------|--------------------------------|-----------------------------------------|--------------------|-------------------------|

| PAGE READ                       | 00h                | 5                              | No                                      | 30h                | No                      |

| PAGE READ CACHE MODE START      | 31h                | —                              | No                                      | _                  | No                      |

| PAGE READ CACHE MODE START LAST | 3Fh                | —                              | No                                      | _                  | No                      |

| READ for INTERNAL DATA MOVE     | 00h                | 5                              | No                                      | 35h                | No                      |

| RANDOM DATA READ                | 05h                | 2                              | No                                      | E0h                | No                      |

| READ ID                         | 90h                | 1                              | No                                      | _                  | No                      |

| READ STATUS                     | 70h                | —                              | No                                      | _                  | Yes                     |

| PROGRAM PAGE                    | 80h                | 5                              | Yes                                     | 10h                | No                      |

| PROGRAM PAGE CACHE MODE         | 80h                | 5                              | Yes                                     | 15h                | No                      |

| PROGRAM for INTERNAL DATA MOVE  | 85h                | 5                              | Optional                                | 10h                | No                      |

| RANDOM DATA INPUT               | 85h                | 2                              | Yes                                     | —                  | No                      |

| BLOCK ERASE                     | 60h                | 3                              | No                                      | D0h                | No                      |

| RESET                           | FFh                | —                              | No                                      | _                  | Yes                     |

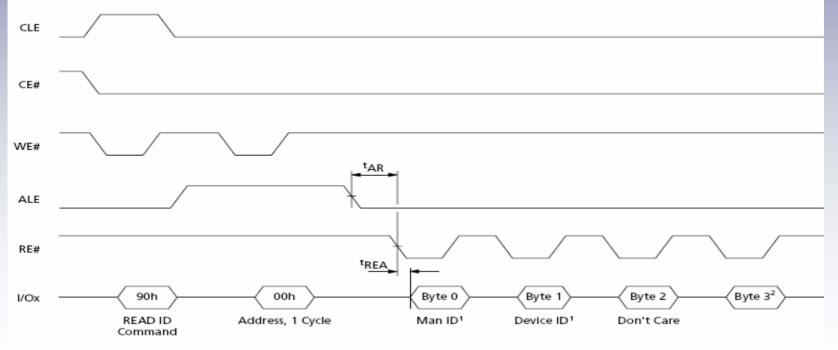

### **Read ID Operation**

| Command                         | Command<br>Cycle 1 | Number of<br>Address<br>Cycles | Data<br>Cycles<br>Required <sup>1</sup> | Command<br>Cycle 2 | Valid<br>During<br>Busy |

|---------------------------------|--------------------|--------------------------------|-----------------------------------------|--------------------|-------------------------|

| PAGE READ                       | 00h                | 5                              | No                                      | 30h                | No                      |

| PAGE READ CACHE MODE START      | 31h                | —                              | No                                      | _                  | No                      |

| PAGE READ CACHE MODE START LAST | 3Fh                | —                              | No                                      | _                  | No                      |

| READ for INTERNAL DATA MOVE     | 00h                | 5                              | No                                      | 35h                | No                      |

| RANDOM DATA READ                | 05h                | 2                              | No                                      | E0h                | No                      |

| READ ID                         | 90h                | 1                              | No                                      | —                  | No                      |

| READ STATUS                     | 70h                | —                              | No                                      | _                  | Yes                     |

| PROGRAM PAGE                    | 80h                | 5                              | Yes                                     | 10h                | No                      |

| PROGRAM PAGE CACHE MODE         | 80h                | 5                              | Yes                                     | 15h                | No                      |

| PROGRAM for INTERNAL DATA MOVE  | 85h                | 5                              | Optional                                | 10h                | No                      |

| RANDOM DATA INPUT               | 85h                | 2                              | Yes                                     | _                  | No                      |

| BLOCK ERASE                     | 60h                | 3                              | No                                      | D0h                | No                      |

| RESET                           | FFh                | _                              | No                                      | —                  | Yes                     |

#### **Device IDs**

| Density | x8/x16 | 1.8V/3.3V | # of Die | Byte 0<br>Manf. ID | Byte 1<br>Device ID |

|---------|--------|-----------|----------|--------------------|---------------------|

| 1Gb     | x8     | 1.8V      | 1        | 2Ch                | A1h                 |

| 1Gb     | x8     | 3.3V      | 1        | 2Ch                | F1h                 |

| 1Gb     | x16    | 1.8V      | 1        | 2Ch                | B1h                 |

| 1Gb     | x16    | 3.3V      | 1        | 2Ch                | C1h                 |

| 2Gb     | x8     | 1.8V      | 1        | 2Ch                | AAh                 |

| 2Gb     | x8     | 3.3V      | 1        | 2Ch                | DAh                 |

| 2Gb     | x16    | 1.8V      | 1        | 2Ch                | BAh                 |

| 2Gb     | x16    | 3.3V      | 1        | 2Ch                | CAh                 |

| 4Gb     | x8     | 1.8V      | 2        | 2Ch                | ACh                 |

| 4Gb     | x8     | 3.3V      | 2        | 2Ch                | DCh                 |

| 4Gb     | x16    | 1.8V      | 2        | 2Ch                | BCh                 |

| 4Gb     | x16    | 3.3V      | 2        | 2Ch                | CCh                 |

| 8Gb     | x8     | 1.8V      | 4        | 2Ch                | ACh                 |

| 8Gb     | x8     | 3.3V      | 4        | 2Ch                | DCh                 |

| 8Gb     | x16    | 1.8V      | 4        | 2Ch                | BCh                 |

| 8Gb     | x16    | 3.3V      | 4        | 2Ch                | CCh                 |

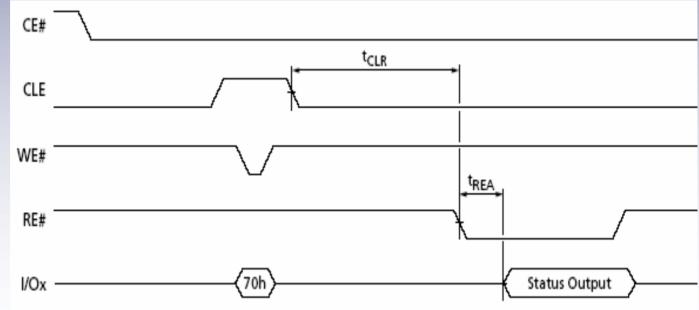

## **Read Status Operation**

| Command                         | Command<br>Cycle 1 | Number of<br>Address<br>Cycles | Data<br>Cycles<br>Required <sup>1</sup> | Command<br>Cycle 2 | Valid<br>During<br>Busy |

|---------------------------------|--------------------|--------------------------------|-----------------------------------------|--------------------|-------------------------|

| PAGE READ                       | 00h                | 5                              | No                                      | 30h                | No                      |

| PAGE READ CACHE MODE START      | 31h                | —                              | No                                      | _                  | No                      |

| PAGE READ CACHE MODE START LAST | 3Fh                | —                              | No                                      | _                  | No                      |

| READ for INTERNAL DATA MOVE     | 00h                | 5                              | No                                      | 35h                | No                      |

| RANDOM DATA READ                | 05h                | 2                              | No                                      | E0h                | No                      |

| READ ID                         | 90h                | 1                              | No                                      | —                  | No                      |

| READ STATUS                     | 70h                | —                              | No                                      | —                  | Yes                     |

| PROGRAM PAGE                    | 80h                | 5                              | Yes                                     | 10h                | No                      |

| PROGRAM PAGE CACHE MODE         | 80h                | 5                              | Yes                                     | 15h                | No                      |

| PROGRAM for INTERNAL DATA MOVE  | 85h                | 5                              | Optional                                | 10h                | No                      |

| RANDOM DATA INPUT               | 85h                | 2                              | Yes                                     | —                  | No                      |

| BLOCK ERASE                     | 60h                | 3                              | No                                      | D0h                | No                      |

| RESET                           | FFh                | —                              | No                                      | —                  | Yes                     |

## NAND Flash Read Status Results

| Program<br>Page | Program Page<br>Cache Mode                              | Page Read                                                                                               | Page Read<br>Cache Mode                                                                                                                                 | Block Erase                                                                                                                                                                                  | Definition                                                                                                                                                                                                                                                         |

|-----------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pass/fail       | Pass/fail (N)                                           | -                                                                                                       | -                                                                                                                                                       | Pass/fail                                                                                                                                                                                    | 0 = Successful PROGRAM/ERASE<br>1 = Error in PROGRAM/ERASE                                                                                                                                                                                                         |

| -               | Pass/fail (N-1)                                         | -                                                                                                       | -                                                                                                                                                       | -                                                                                                                                                                                            | 0 = Successful PROGRAM<br>1 = Error in PROGRAM                                                                                                                                                                                                                     |

| -               | -                                                       | -                                                                                                       | -                                                                                                                                                       | -                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                  |

| -               | -                                                       | -                                                                                                       | -                                                                                                                                                       | -                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                  |

| -               | -                                                       | -                                                                                                       | -                                                                                                                                                       | -                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                  |

| Ready/busy      | Ready/busy <sup>2</sup>                                 | Ready/busy                                                                                              | Ready/busy <sup>2</sup>                                                                                                                                 | Ready/busy                                                                                                                                                                                   | 0 = Busy<br>1 = Ready                                                                                                                                                                                                                                              |

| Ready/busy      | Ready/busy<br>cache <sup>3</sup>                        | Ready/busy                                                                                              | Ready/busy<br>cache <sup>3</sup>                                                                                                                        | Ready/busy                                                                                                                                                                                   | 0 = Busy<br>1 = Ready                                                                                                                                                                                                                                              |

| Write protect   | Write protect                                           | Write protect                                                                                           | Write protect                                                                                                                                           | Write protect                                                                                                                                                                                | 0 = Protected<br>1 = Not protected                                                                                                                                                                                                                                 |

|                 | Page<br>Pass/fail<br>-<br>-<br>Ready/busy<br>Ready/busy | PageCache ModePass/failPass/fail (N)-Pass/fail (N-1)Ready/busyReady/busy²Ready/busyReady/busy<br>cache³ | PageCache ModePage ReadPass/failPass/fail (N)Pass/fail (N-1)Ready/busyReady/busy²Ready/busyReady/busyReady/busyReady/busyReady/busyReady/busyReady/busy | PageCache ModePage ReadCache ModePass/failPass/fail (N)Pass/fail (N-1)Ready/busyReady/busy²Ready/busyReady/busy²Ready/busyReady/busyReady/busyReady/busycache³Ready/busyReady/busyReady/busy | PageCache ModePage ReadCache ModeBlock ErasePass/failPass/fail (N)Pass/fail-Pass/fail (N-1)Pass/fail (N-1)Ready/busyReady/busy²Ready/busyReady/busy²Ready/busyReady/busyReady/busyReady/busyReady/busyReady/busyReady/busyReady/busyReady/busyReady/busyReady/busy |

#### Read status typically = E0h when the NAND is ready with no error

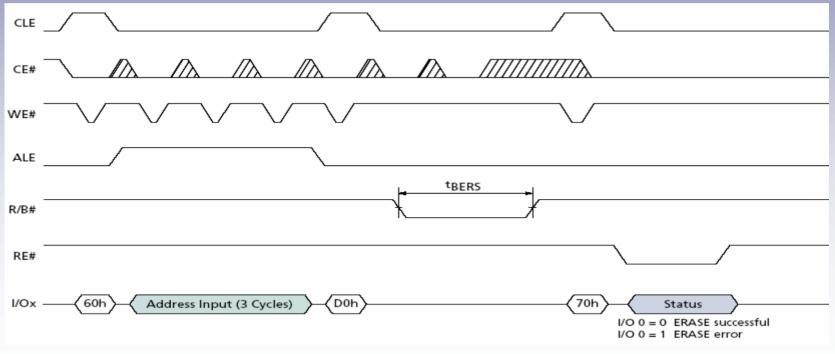

#### **Block Erase Operation**

Register

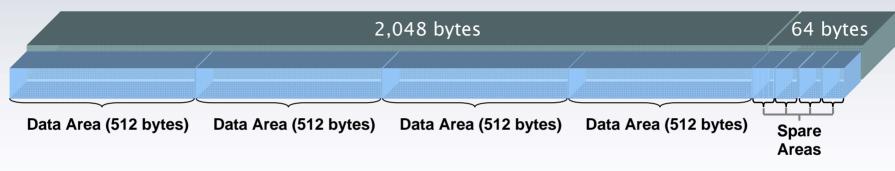

#### 2,112 bytes

| Flash Memory |

|--------------|

#### **Block Erase Operation**

| Command                         | Command<br>Cycle 1 | Number of<br>Address<br>Cycles | Data<br>Cycles<br>Required <sup>1</sup> | Command<br>Cycle 2 | Valid<br>During<br>Busy |

|---------------------------------|--------------------|--------------------------------|-----------------------------------------|--------------------|-------------------------|

| PAGE READ                       | 00h                | 5                              | No                                      | 30h                | No                      |

| PAGE READ CACHE MODE START      | 31h                | —                              | No                                      | —                  | No                      |

| PAGE READ CACHE MODE START LAST | 3Fh                | —                              | No                                      | —                  | No                      |

| READ for INTERNAL DATA MOVE     | 00h                | 5                              | No                                      | 35h                | No                      |

| RANDOM DATA READ                | 05h                | 2                              | No                                      | E0h                | No                      |

| READ ID                         | 90h                | 1                              | No                                      | —                  | No                      |

| READ STATUS                     | 70h                | —                              | No                                      | —                  | Yes                     |

| PROGRAM PAGE                    | 80h                | 5                              | Yes                                     | 10h                | No                      |

| PROGRAM PAGE CACHE MODE         | 80h                | 5                              | Yes                                     | 15h                | No                      |

| PROGRAM for INTERNAL DATA MOVE  | 85h                | 5                              | Optional                                | 10h                | No                      |

| RANDOM DATA INPUT               | 85h                | 2                              | Yes                                     | _                  | No                      |

| BLOCK ERASE                     | 60h                | 3                              | No                                      | D0h                | No                      |

| RESET                           | FFh                | —                              | No                                      | _                  | Yes                     |

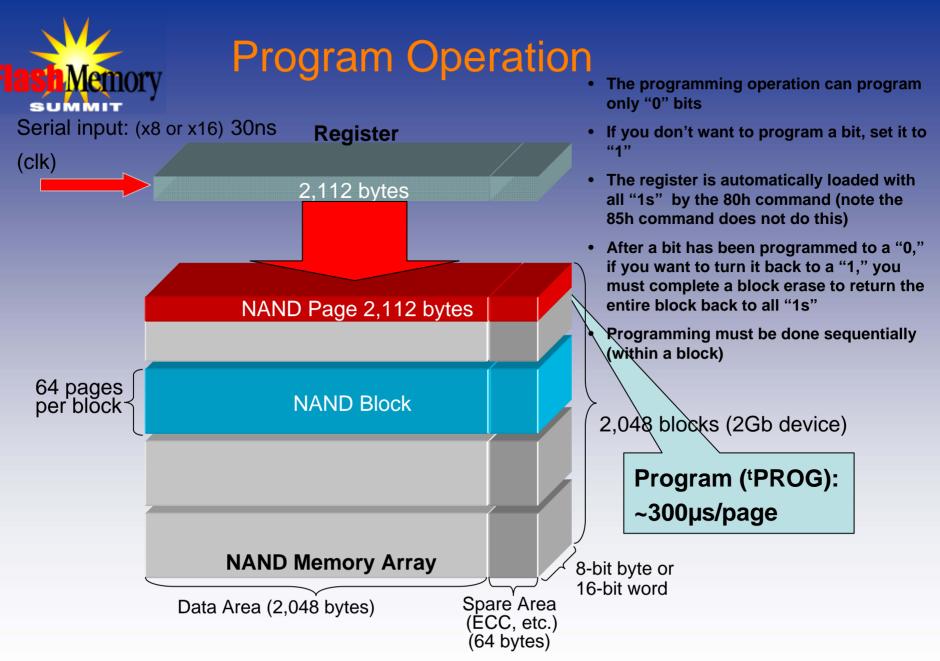

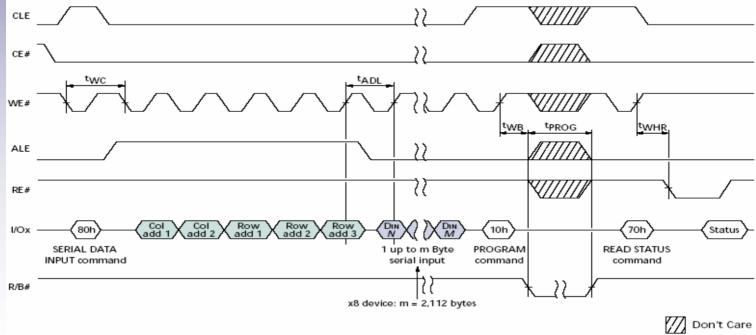

#### **Program Operation**

|    | Command                         | Command<br>Cycle 1 | Number of<br>Address<br>Cycles | Data<br>Cycles<br>Required <sup>1</sup> | Command<br>Cycle 2 | Valid<br>During<br>Busy |

|----|---------------------------------|--------------------|--------------------------------|-----------------------------------------|--------------------|-------------------------|

|    | PAGE READ                       | 00h                | 5                              | No                                      | 30h                | No                      |

|    | PAGE READ CACHE MODE START      | 31h                | -                              | No                                      | -                  | No                      |

|    | PAGE READ CACHE MODE START LAST | 3Fh                | -                              | No                                      | _                  | No                      |

|    | READ for INTERNAL DATA MOVE     | 00h                | 5                              | No                                      | 35h                | No                      |

|    | RANDOM DATA READ                | 05h                | 2                              | No                                      | E0h                | No                      |

|    | READ ID                         | 90h                | 1                              | No                                      | _                  | No                      |

|    | READ STATUS                     | 70h                | -                              | No                                      | _                  | Yes                     |

|    | PROGRAM PAGE                    | 80h                | 5                              | Yes                                     | 10h                | No                      |

|    | PROGRAM PAGE CACHE MODE         | 80h                | 5                              | Yes                                     | 15h                | No                      |

|    | PROGRAM for INTERNAL DATA MOVE  | 85h                | 5                              | Optional                                | 10h                | No                      |

| ·  | RANDOM DATA INPUT               | 85h                | 2                              | Yes                                     | _                  | No                      |

|    | BLOCK ERASE                     | 60h                | 3                              | No                                      | D0h                | No                      |

|    | RESET                           | FFh                | -                              | No                                      | -                  | Yes                     |

| 22 |                                 | /////<br>///\}     |                                |                                         |                    |                         |

rv

SUMMIT

#### Random Data Input/Program The page is programmed when you issue the 10h confirmation. Each You can input as of these counts many address and toward the data combinations as partial-page vou want. programming limit (of 8). CLE CE# AD WBL TPROG ALE RE# V//// DIN Row Row Row I/Ox 85 (70h Status 10h SERIAL DATA RANDOM DATA Column Address ROGRAM READ STATUS INPUT Command Serial Input INPUT Command Serial Input Command Command R/B#

Don't Care

8

<

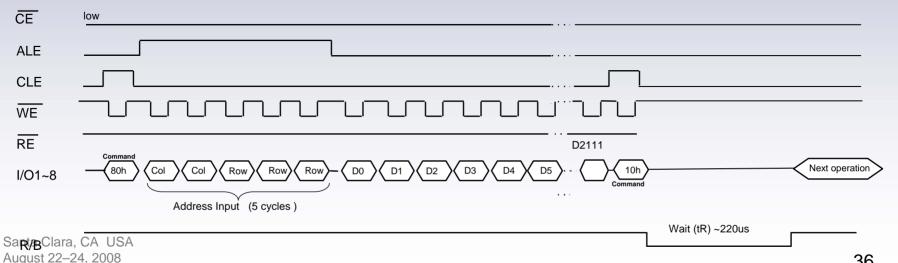

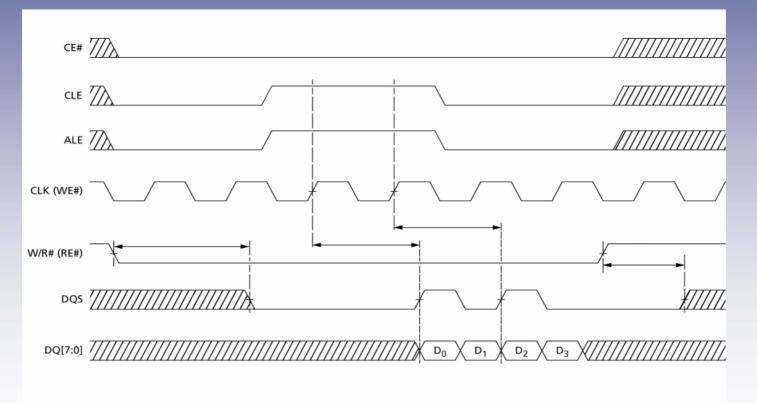

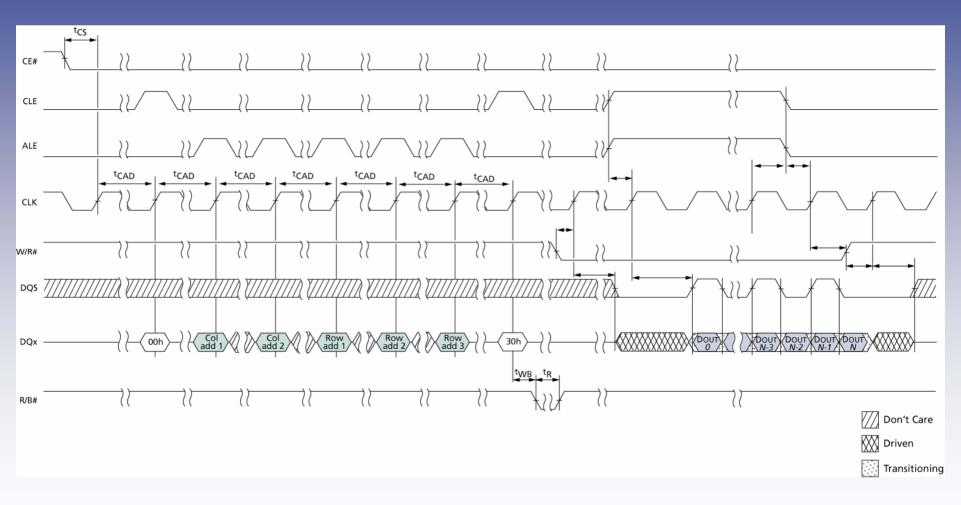

**Read Operation**

## **Random Read Operation**

- The RANDOM READ command allows you to specify a new two-byte column address

- Can use the RANDOM READ command to jump around anywhere on the page

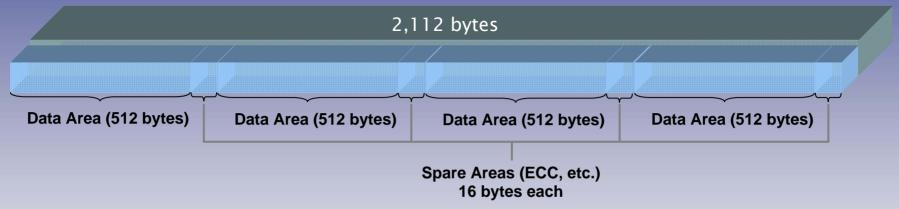

## **Partial-Page Programming**

- NOP specifies the number of programming operations that can be executed on the same page

- Pages are programmed in groups due to the large page sizes (SLC only)

- Typical PC sector size is 512, so four PC sectors fit into one 2K page

- Programming ECC info separately from the data could require an additional four operations

- The user can have other info (logical mapping or wear-leveling) in the spare area

- It is best to minimize partial-page programming

- The number of partial-page program operations is the number of complete programming operations (with confirm 10h) to the same location without an erase

- MLC devices have an NOP of 1

#### Methods for Data and Spare Information Placement

#### Data and spare information adjacent

#### Data and spare information separate

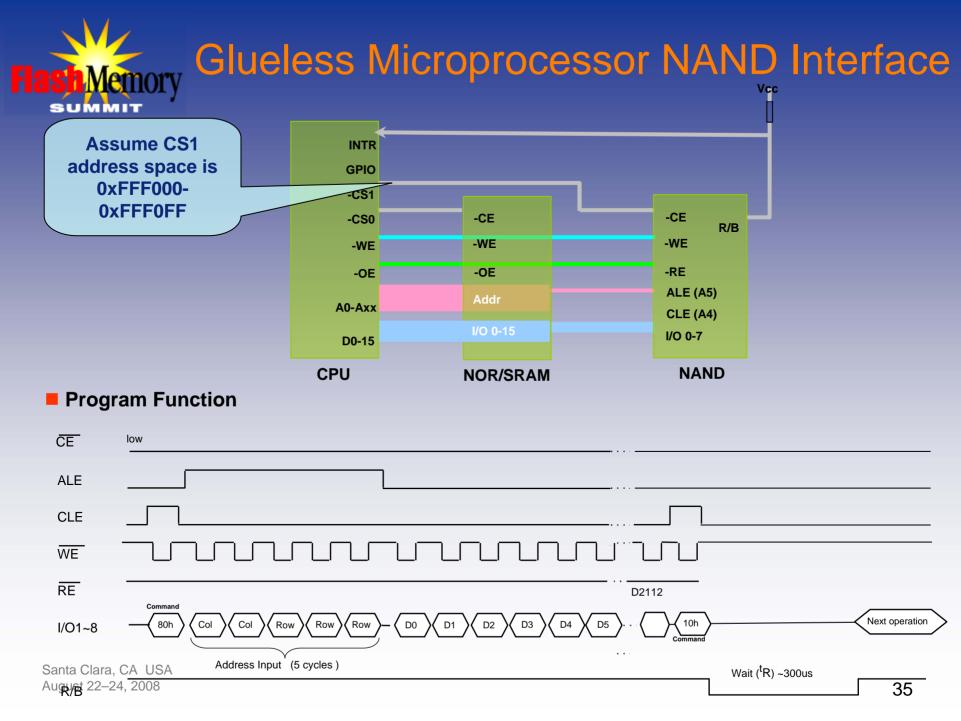

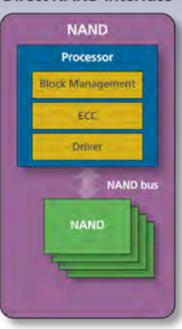

## Connecting NAND to a RISC Processor or DSP That Does not Include a NAND Controller

### **Direct Connection to RISC Processor**

#### Memory Mapped NAND Interface

- If microprocessor address 4 is connected to CLE and address 5 is connected to ALE, the NAND can be accessed by a software that uses only three address locations

- Command register can be accessed by writing to address XX010h

- Address register can be accessed by writing to address XX020h

- Data register can be accessed by writing/reading to address XX000h

|     | / | 47 | A6                    | A5 | A4 | A3 | A | 2                     | A1                     | A0 |  |  |

|-----|---|----|-----------------------|----|----|----|---|-----------------------|------------------------|----|--|--|

| A5  | A | \4 |                       |    |    |    |   |                       |                        |    |  |  |

| ALE | C | LE | Memory Address Offset |    |    |    |   |                       | NAND Register Selected |    |  |  |

| 0   |   | 0  | 0                     |    |    |    |   | Data register         |                        |    |  |  |

| 0   |   | 1  | 1                     |    |    |    |   |                       | Command register       |    |  |  |

| 1   |   | 0  | 2                     |    |    |    |   | Address register      |                        |    |  |  |

| 1   |   | 1  | 3                     |    |    |    |   | Undefined (don't use) |                        |    |  |  |

# Glueless Microprocessor NAND Interface

| SIMUCIIIOIY Pseudo-Code      |

|------------------------------|

| SUMMIT Example for PROGRAM:  |

| (All numbers in HEX)         |

| 80 -> FFF010 ; CMD = 80      |

| ColL -> FFF020 ; low column  |

| ColH -> FFF020 ; high column |

| RowL -> FFF020 ; low ROW     |

| RowM -> FFF020 ; Mid ROW     |

| RowH -> FFF020 ; High ROW    |

| D0 -> FFF000 ; Data 0        |

| D1 -> FFF000 ; Data 1        |

|                              |

(Complete remaining data) D2111 -> FFF000 : Data 2111 10 -> **FFF010** ; CMD = 10LOOP1:  $PA \rightarrow Acc$ : Read status BIT #6 set ; JMP NZ LOOP1 Jmp if Busy to Loop : ; DONE !

#### Program Function

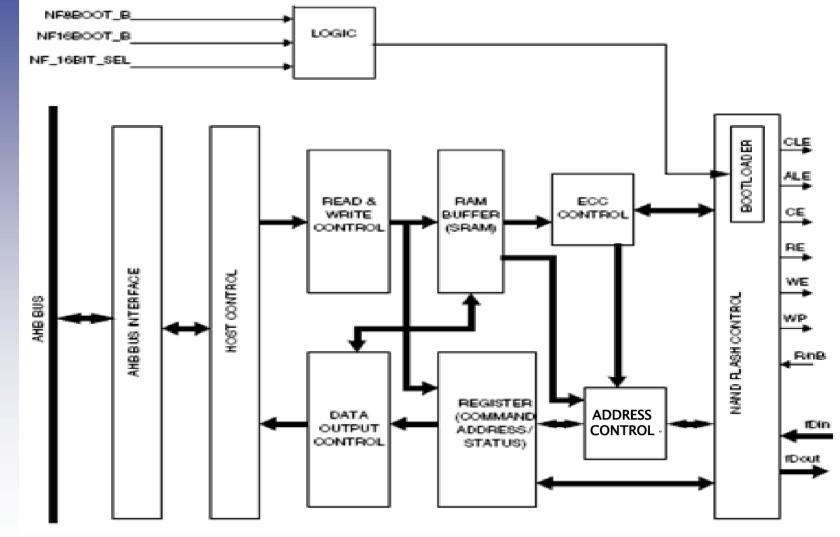

**Processor Support**

- Processors with native NAND controller built-in with support for 2K page:

- Motorola i.MX21 and i.MX31 and others

- TI Omap 2420 and 2430 and others

- Other vendors are adding direct-NAND interface; check with your vendor

### Native NAND Interface on Freescale i.MX21

Santa Clara, CA USA August 22–24, 2008

diagram courtesy Freescale Semiconductor

# Single-Level Cell (SLC) vs. Multi-Level Cell (MLC)

Santa Clara, CA USA August 22–24, 2008

# What is the Difference?

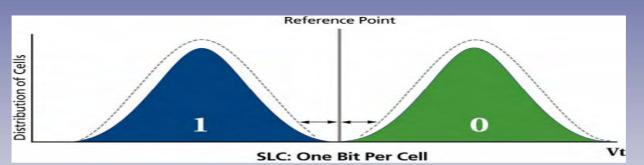

- SLC (single-level cell)

- SLC stores <u>2</u> states per memory cell and allows <u>1</u> bit programmed/read per memory cell

- MLC (multi-level cell)

- MLC NAND stores <u>4</u> states per memory cell and allows <u>2</u> bits programmed/read per memory cell

### SLC vs. MLC

- SLC NAND Flash products offer higher performance and reliability; typical applications include:

- High performance media cards

- Solid state drives (SSDs)

- Many embedded (NAND built inside) designs including:

- Cell phones (for executing code); MLC will still be considered for high density storage

- Multi-level cell (MLC) NAND Flash will lead in the lowest cost for consumer applications where performance and reliability are not as important; typical applications include:

- Media players (audio and video)

- Cell phones (SLC will still be considered for code execution)

- Consumer media cards (such as USB, SD/MMC, and CF cards)

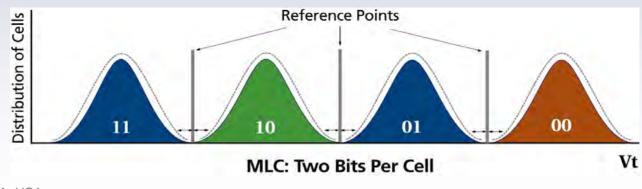

# **SLC** Attributes

- Key attributes:

- Single bit per cell

- Supports low voltage (1.8V); required for many mobile applications

- Offered in wide data bus (16 bits) as well as 8-bit

- Supported by all controllers because SLC generally requires only 1-bit ECC

- Higher performance

- Higher reliability

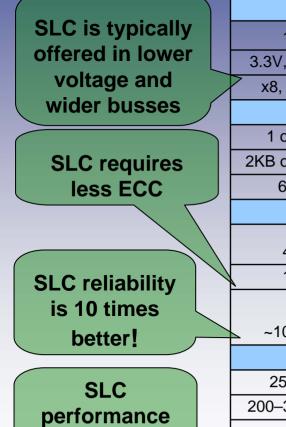

| Features                         |                |

|----------------------------------|----------------|

| Bits per cell                    | 1              |

| Voltage                          | 3.3V, 1.8V     |

| Data width (bits)                | x8, x16        |

| Architecture                     |                |

| Number of planes                 | 1 or 2         |

| Page size                        | 2K or 4K bytes |

| Pages per block                  | 64             |

| Reliability                      |                |

| NOP (partial-page programming)   | 4              |

| ECC (per 512 bytes)              | 1              |

| Endurance (ERASE/PROGRAM cycles) | ~100K          |

| Array Operations                 |                |

| <sup>t</sup> R (Max)             | 25µs           |

| <sup>t</sup> PROG (Typ)          | 200–300µs      |

| <sup>t</sup> BERS (Typ)          | 1.5–2ms        |

### **MLC** Attributes

- Key attributes:

- Two bits per cell; twice the density of similar SLC device

- Offered only in 3.3V

- Offered only in x8 data bus

- Supported only by controllers that include 4-bit (or more) ECC

- Compared to SLC NAND:

- Lower performance

- Lower reliability

- Lower price

| Features                         |                |

|----------------------------------|----------------|

| Bits per cell                    | 2              |

| Voltage                          | 3.3V           |

| Data width (bits)                | x8             |

| Architecture                     |                |

| Number of planes                 | 2              |

| Page size                        | 2K or 4K bytes |

| Pages per block                  | 128            |

| Reliability                      |                |

| NOP (partial-page programming)   | 1              |

| ECC (per 512 bytes)              | 4+             |

| Endurance (ERASE/PROGRAM cycles) | ~10K           |

| Array Operations                 |                |

| <sup>t</sup> R (Max)             | 50µs           |

| <sup>t</sup> PROG (Typ)          | 600–900µs      |

| <sup>t</sup> BERS (Typ)          | 3ms            |

# SLC vs. MLC

| SUMMIT              |                  |                                        |            |  |  |  |

|---------------------|------------------|----------------------------------------|------------|--|--|--|

| SUMMIT              |                  |                                        |            |  |  |  |

|                     | SLC              |                                        | MLC        |  |  |  |

|                     |                  | Features                               |            |  |  |  |

| SLC is typically    | 1                | Bits per cell                          | 2          |  |  |  |

| offered in lower    | 3.3V, 1.8V       | Voltage                                | 3.3V       |  |  |  |

| voltage and         | x8, x16          | Data width (bits)                      | x8         |  |  |  |

| wider busses        | Architecture     |                                        |            |  |  |  |

|                     | 1 or 2           | Number of planes                       | 2          |  |  |  |

| SLC requires        | 2KB or 4KB       | Page size                              | 2KB or 4KB |  |  |  |

| less ECC            | 64               | Pages per block                        | 128        |  |  |  |

|                     |                  | Reliability                            |            |  |  |  |

|                     | 4                | NOP (partial-page programming)         | 1          |  |  |  |

| SLC reliability     | 1                | ECC (per 528 bytes)                    | 4+         |  |  |  |

| is 10 times better! | ~100K            | Endurance<br>(ERASE/PROGRAM<br>cycles) | ~10K       |  |  |  |

|                     | Array Operations |                                        |            |  |  |  |

| SLC                 | 25µs             | <sup>t</sup> R (Max)                   | 50µs       |  |  |  |

| performance         | 200–300µs        | <sup>t</sup> PROG (Typ)                | 600–900µs  |  |  |  |

| is ~3 times         | 1.5–2ms          | <sup>t</sup> BERS (Typ)                | 3ms        |  |  |  |

| better              |                  |                                        |            |  |  |  |

**MLC** density is 2 times that of similar SLC

Santa Clara, CA USA August 22-24, 2008

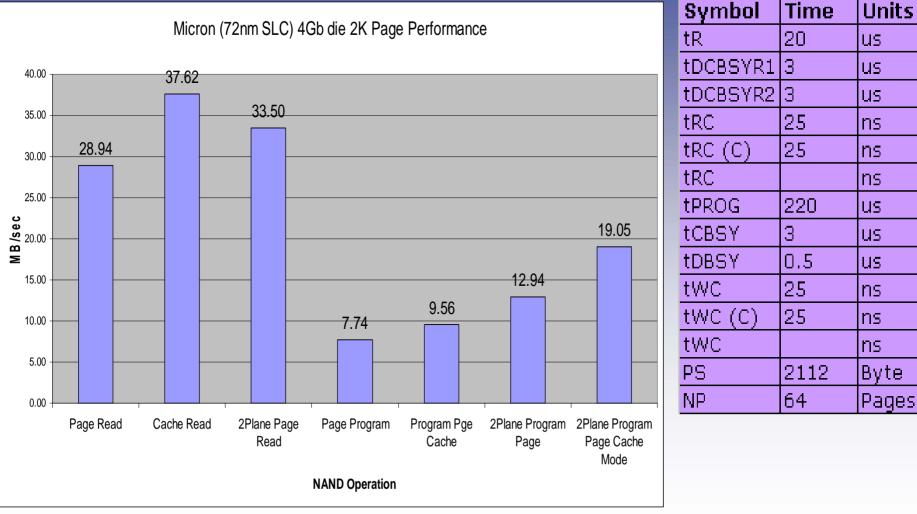

### **4Gb SLC Performance**

|         |           |             | (72nm S     | LC) 4Gb Pe  | erformanc | e           |         |            | Symbol   | Time | Units |

|---------|-----------|-------------|-------------|-------------|-----------|-------------|---------|------------|----------|------|-------|

|         |           |             |             |             |           |             |         |            | tR       | 20   | us    |

| 45.00   |           |             |             | 38.65       |           |             |         |            | tDCBSYR1 | 3    | us    |

| 40.00 - |           | 37.62       | 00 50       | 50.05       |           |             |         |            | tDCBSYR2 | 3    | us    |

| 35.00 - | 00.04     |             | 33.50       | _           |           |             |         |            | tRC      | 25   | ns    |

| 30.00 - | 28.94     |             |             | _           |           |             |         |            | tRC (C)  | 25   | ns    |

| 25.00 - |           |             |             |             |           |             |         |            | tRC      |      | ns    |

| 20.00 - |           |             |             |             |           |             |         | 19.05      | tPROG    | 220  | us    |

| 15.00 - |           |             |             |             |           |             | 12.94   |            | tCBSY    | 3    | us    |

| 10.00 - |           |             |             |             | 7.74      | 9.56        |         |            | tDBSY    | 0.5  | us    |

|         |           |             |             |             |           |             |         |            | tWC      | 25   | ns    |

| 5.00 -  |           |             |             |             |           |             |         |            | tWC (C)  | 25   | ns    |

| 0.00 +  | Page Read | Cache Read  | 2Plane Page | 2Plane Page | Page      | Program Pge | 2Plane  | 2Plane     | tWC      |      | ns    |

|         | raye neau | Caulle Reau | Read        | Read Cache  | Program   | Cache       | Program | Program    | PS       | 2112 | Byte  |

|         |           |             |             | Mode        |           |             | Page    | Page Cache | NP       | 64   | Pages |

|         |           |             |             |             |           |             |         | Mode       |          |      |       |

### **8Gb MLC Performance**

|         | (72nm MLC) 8Gb Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Symbol   | Time | Units |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|

| 45.00 - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tR       | 50   | us    |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tDCBSYR1 | 7    | us    |

| 40.00 - | 37.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tDCBSYR2 | 7    | us    |

| 35.00 - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tRC      | 25   | ns    |

| 30.00 - | 27.06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tRC (C)  | 25   | ns    |

| 25.00   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tRC      | 25   | ns    |

| 25.00 - | 20.51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tPROG    | 650  | us    |

| 20.00 - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tCBSY    | 30   | us    |

| 15.00 - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tDBSY    | 0.5  | us    |

| 10.00 - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tWC      | 25   | ns    |

|         | 3.00 3.25 5.58 6.49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tWC (C)  | 25   | ns    |

| 5.00 -  | 3.00 3.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | tWC      | 25   | ns    |

| 0.00 -  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PS       | 2112 | Byte  |

|         | Page Read         Cache Read         2Plane Page         Page         Program         2Plane         2Plane | NP       | 128  | Pages |

|         | Mode Page Page Cache<br>Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |      |       |

### **SLC Requires Less ECC**

- While it is possible to implement 1-bit correct (Hamming code) in software, it generally does not provide a high performance solution

- Many microprocessors include NAND controllers that support 1-bit ECC

- Some newer processors are looking to include 4-bit ECC (or more) in their on-chip NAND controllers

# SLC vs. MLC Conclusions

- MLC will always provide the lowest cost per bit

- SLC will always provide the highest performance

- SLC will always provide the highest reliability

- Choose the right NAND device for the application

# All NAND Flash Devices Are Not Created Equal

- Differences include:

- Cell types

- Architecture

- Performance

- Timing parameters

- Command set

- Open NAND Flash Interface (ONFI) drives a standard interface

Santa Clara, CA USA August 22–24, 2008

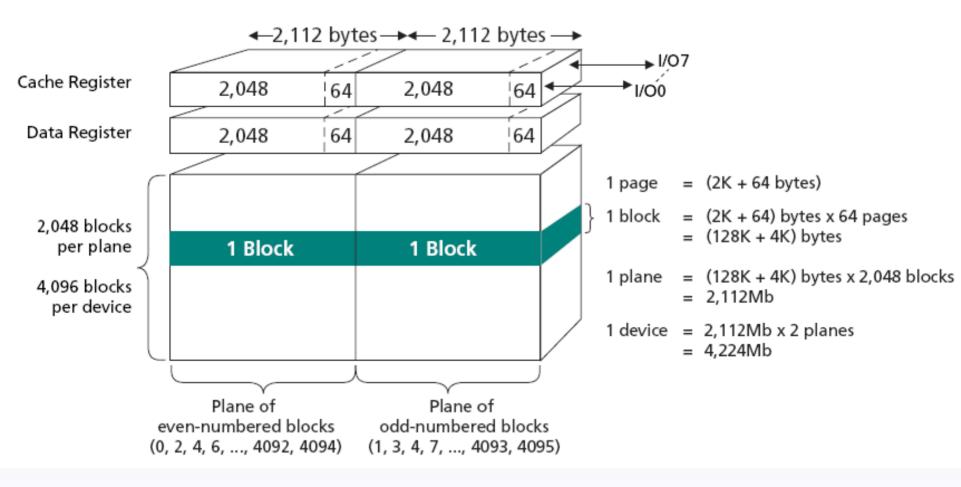

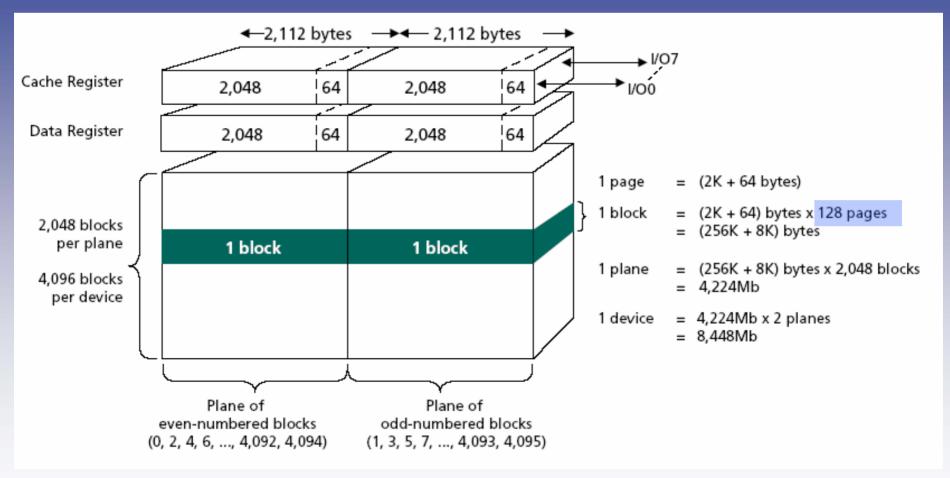

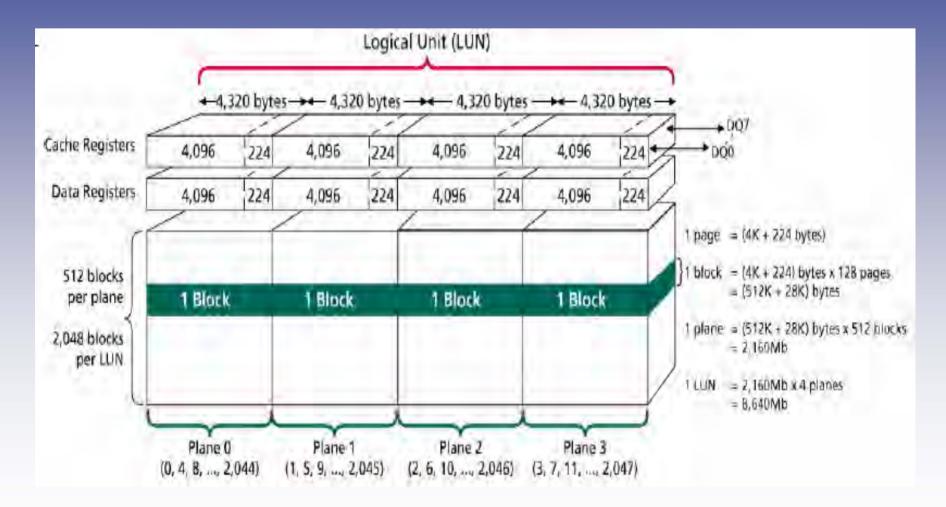

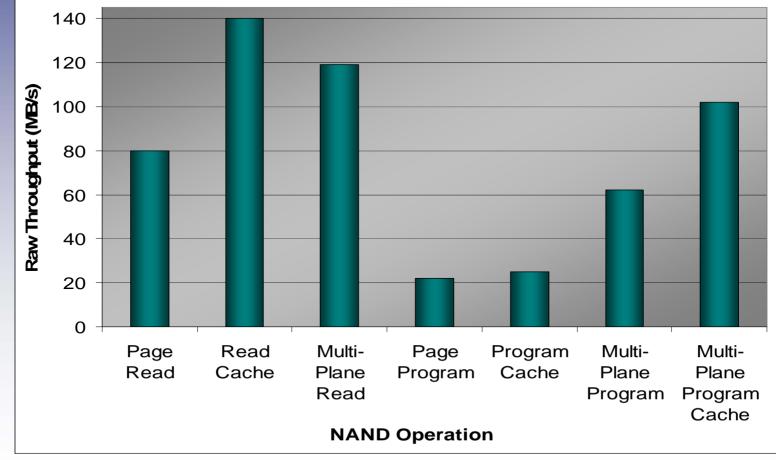

### **Two-Plane Features**

- Device is divided into two physical planes, odd/even blocks

- Users have the ability to:

- · Concurrently access two pages for read

- Erase two blocks concurrently

- Program two pages concurrently

- The page addresses of blocks from both planes must be the same during two-plane READ/PROGRAM/ERASE operations

### 4Gb, Two-Plane, 2K-Page SLC NAND Architecture

### 4Gb, 2K-Page SLC NAND Performance

### 8Gb, Two-Plane, 2K-Page MLC NAND Architecture

Santa Clara, CA USA August 22–24, 2008

**1**Memory

SUMMIT

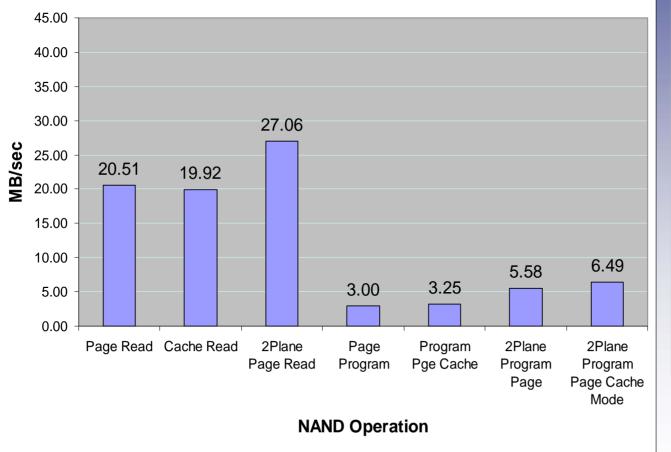

# 8Gb, 2K-Page MLC Performance

Micron (72nm MLC) 8Gb die 2K Page Performance

| Time | Units                                                                         |

|------|-------------------------------------------------------------------------------|

| 50   | us                                                                            |

| 7    | us                                                                            |

| 7    | us                                                                            |

| 25   | ns                                                                            |

| 25   | ns                                                                            |

| 25   | ns                                                                            |

| 650  | us                                                                            |

| 30   | us                                                                            |

| 0.5  | us                                                                            |

| 25   | ns                                                                            |

| 25   | ns                                                                            |

| 25   | ns                                                                            |

| 2112 | Byte                                                                          |

| 128  | Pages                                                                         |

|      | 50<br>7<br>25<br>25<br>25<br>650<br>30<br>0.5<br>25<br>25<br>25<br>25<br>2112 |

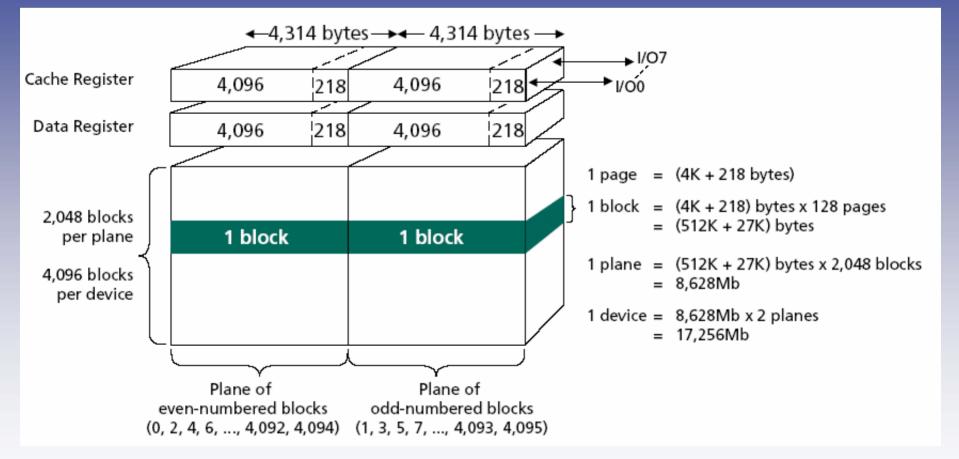

### 16Gb, Two-Plane, 4K-Page MLC NAND Architecture

### Two-Plane, 4K-Page MLC NAND **Architecture**

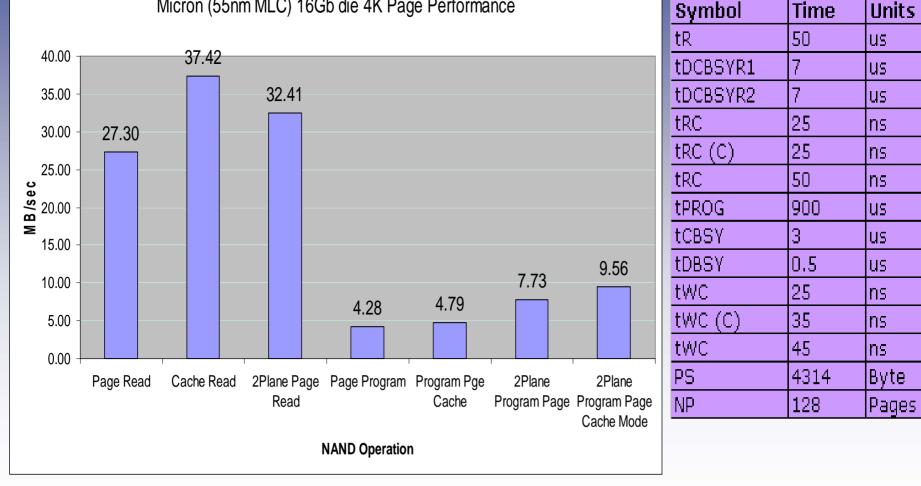

#### Micron (55nm MLC) 16Gb die 4K Page Performance

Time

Units

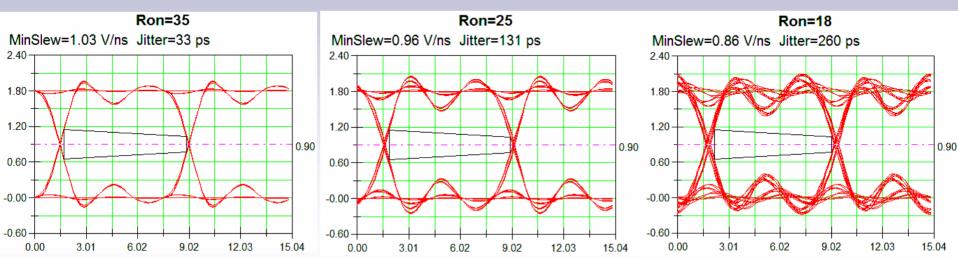

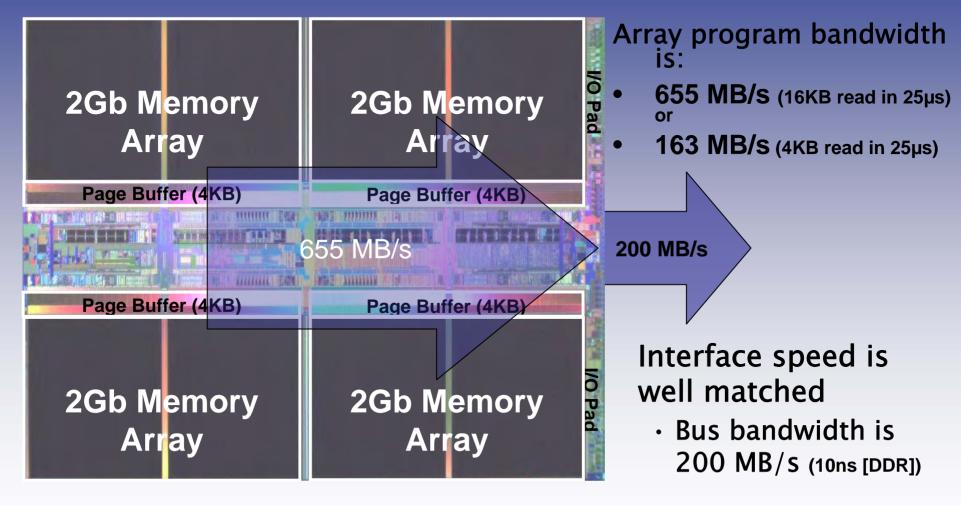

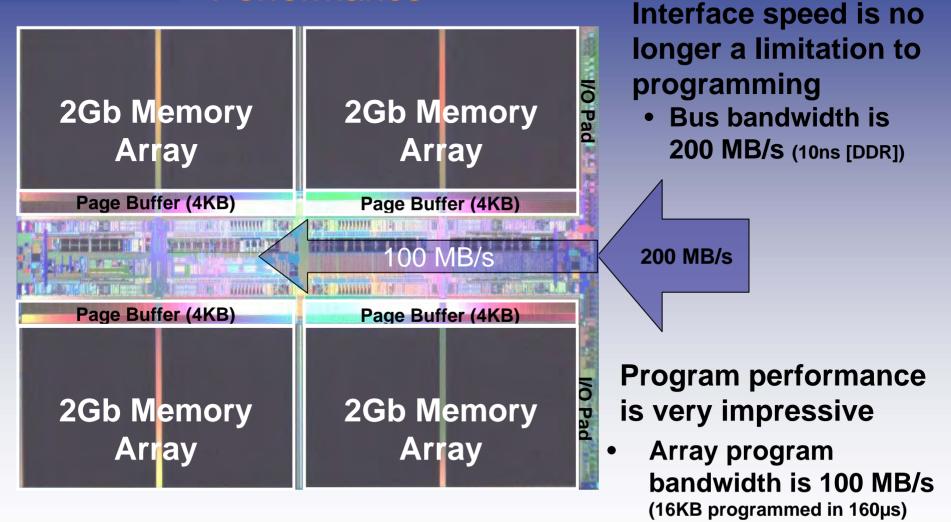

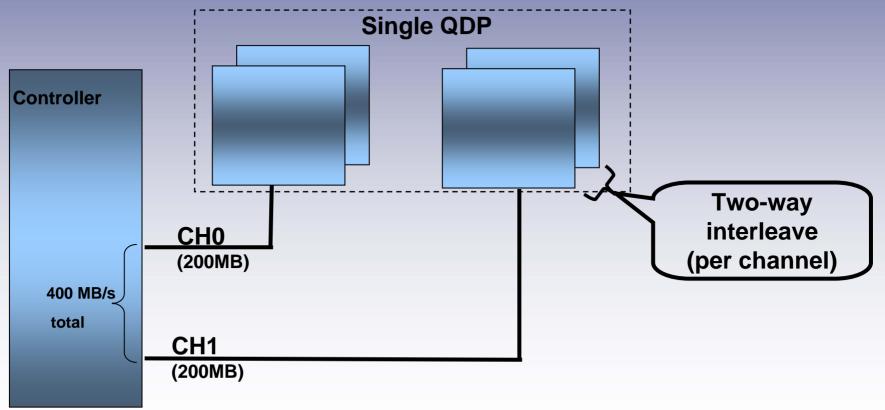

### **Performance Bottlenecks**

Santa Clara, CA USA August 22–24, 2008

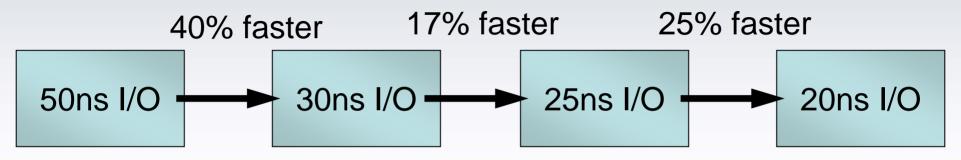

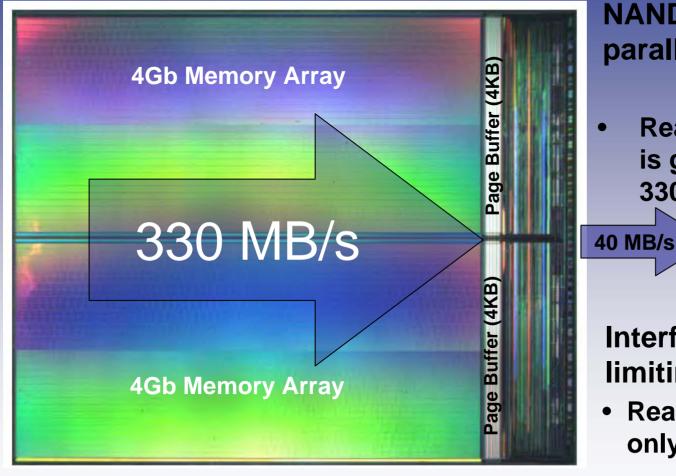

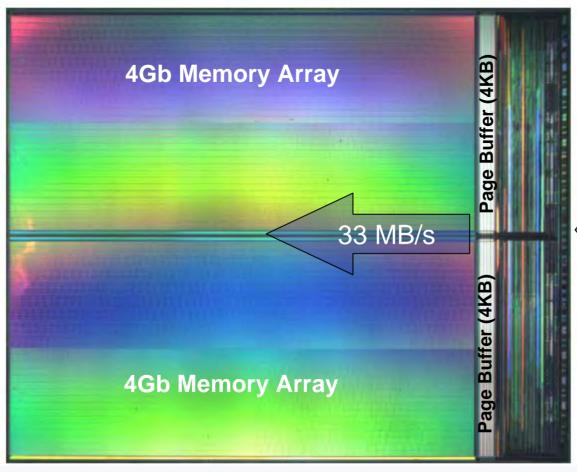

### Read Throughput Limitations in NAND Today

- Read throughput limited by I/O frequency