# Improving Power Budgeting Estimates in NAND Applications

Michael Abraham (mabraham@micron.com) Applications Engineering Manager Micron Technology, Inc.

#### Abstract

- Current NAND Flash ICC specifications do not give an accurate representation of active system power.

- This presentation shows a better approach to measuring ICC that provides better predictability in the system of how much current devices will draw.

- This methodology is particularly useful for battery powered applications like mobile phones, MP3 players, and GPS units as well as large-scale NAND solutions like SSDs.

### **Power Budgeting**

- Accurate system power consumption is important for determine a power budget

- A power budget is used to

- Estimate system battery life

- Determine voltage regulator sizes

- Determine needed bulk capacitance

- An application-specific usage model is required to correctly calculate the power budget

- # of active NAND die

- Single- vs. multi-plane operations

- Active vs. Standby

- Reads vs. writes

- I/O vs. array

- In NAND Flash data sheets today, there are few lcc definitions

- Read

- Program

- Erase

- Standby

| Parameter               | Conditions                                | Symbol | Typical | Мах | Unit |

|-------------------------|-------------------------------------------|--------|---------|-----|------|

| Sequential read current | tRC = tRC (MIN);<br>CE# = Vil; lout = 0mA | lcc1   | 20      | 30  | mA   |

| Program current         |                                           | lcc2   | 20      | 30  | mA   |

| Erase current           |                                           | lcc3   | 20      | 30  | mA   |

| Standby current         | CE# = Vcc – 0.2V;<br>WP# = 0V/Vcc         | Isb    | 10      | 50  | μA   |

# Shortcomings of the Original Icc Test Methodology

- Icc parameters not sufficiently defined for an application-specific usage model

- Current related to I/O and the data path should be separate from current related to array operations (program, read, erase)

- Idle current is not defined

- Icc test methodology is not usable in high volume manufacturing (HVM)

- Designed for single-site device characterization

- Unable to correlate bench testing to HVM testing

- Icc test methodology is not reproducible

- Icc1 (Read) implies data output as it shows I<sub>OUT</sub> = 0mA

- A program page operation requires data input, yet Icc2 shows no condition for it

- Does Icc2 measurement include data input or only the current during tPROG?

- Because of these shortcomings, NAND Flash ICC specifications do not give an accurate representation of active system power.

#### Goals of an Icc Test Methodology

- HVM capable

- Reproducible

- Usable for application-specific power budgets

- Adaptable to multiple NAND interfaces

- Asynchronous (up to 50MB/s per x8 bus)

- Synchronous DDR (up to 200MB/s per x8 bus)

# Icc Test Methodology Implementation Checklist

- Basic power-related device operations

- General test conditions

- Interface-specific test conditions

- Test sequences

- Formulas for correlation

#### **Basic Power-related Operations**

- Array read

- Array program

- Array erase

- I/O burst read (data output)

- I/O burst write (data input)

- Bus Idle

- Standby

#### All NAND behaviors build on and be modeled from these basic operations.

#### **NAND Operation Examples**

#### Page Program is comprised of

- Data Input

- Array Program

- Bus idle and/or standby

- Page Program Cache is comprised of

- Data Input

- Array Program + Data Input

- Bus idle and/or standby

- Between operations there is dead time

- Bus Idle CE# remains LOW

- Standby CE# is pulled HIGH

#### **Icc Parameters**

#### Icc parameters added to allow applicationspecific power budget modeling

| Parameter               | Conditions                 | Symbol | Тур | Мах | Unit |

|-------------------------|----------------------------|--------|-----|-----|------|

| Array read current      | See general and interface- | lcc1   | 20  | 30  | mA   |

| Array program current   | specific test conditions   | lcc2   | 20  | 30  | mA   |

| Array erase current     |                            | lcc3   | 20  | 30  | mA   |

| I/O burst read current  |                            | lcc4r  | 20  | 30  | mA   |

| I/O burst write current |                            | lcc4w  | 20  | 30  | mA   |

| Bus idle current        |                            | lcc5   | 2   | 3   | mA   |

| Standby current (CMOS)  | CE# = Vccq - 0.2V;         | Isb    | 10  | 50  | μA   |

|                         | WP# = 0V/Vccq              |        |     |     |      |

| Parameter                                     | Testing Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General<br>conditions                         | <ol> <li>Vcc = Vcc(min) to Vcc(max)</li> <li>VccQ = VccQ(min) to VccQ(max)</li> <li>CE# = 0 V</li> <li>WP# = VccQ</li> <li>IOUT = 0 mA</li> <li>Measured across operating temperature range</li> <li>N data input or data output cycles, where N is the number of bytes or words in the page</li> <li>No interleaved operations.</li> <li>Sample 250 times at 1 millisecond intervals and average the results</li> <li>Choose the first good even/odd block pair beginning at blocks 2-3</li> </ol> |

| Array<br>preconditioning<br>for lcc1 and lcc3 | The array is preconditioned to match the data input pattern for Icc2.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fixed wait time<br>(no R/B# polling)          | lcc1: tR = tR(max)<br>lcc2: tPROG = tPROG(max)<br>lcc3: tBERS = tBERS(max)                                                                                                                                                                                                                                                                                                                                                                                                                          |

- Common across all NAND interfaces

- Fixed wait time is important for multi-site HVM testing

# Define Interface-specific Test Conditions

| Parameter                                                | Asynchronous                                                                                                       | Synchronous DDR                                                                                |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| AC Timing<br>Parameters                                  | tWC = tWC(min)<br>tRC = tRC(min)<br>tADL = 8 * tWC(min)<br>tCCS = 8 * tWC(min)<br>tRHW = 8 * tWC(min)              | tCK = tCK(avg)<br>tADL = 16 * tCK(avg)<br>tCCS = 32 * tCK(avg)<br>tRHW = 16 * tCK(avg)         |

| Bus idle data<br>pattern                                 | IO[7:0] = FFh<br>IO[15:0] = FFFFh                                                                                  | DQ[7:0] = FFh                                                                                  |

| Repeated data<br>pattern<br>(Used for Icc2<br>and Icc4w) | IO[7:0] = A5h, AAh, 5Ah, 55h<br>IO[15:0] = A5A5h, AAAAh, 5A5Ah, 5555h                                              | DQ[7:0] = A5h, AAh, 5Ah, 55h                                                                   |

| Array<br>preconditioning<br>for Icc4r                    | The array is preconditioned to match the<br>following repeating data pattern:<br>IO[7:0] = A5h<br>IO[15:8] = A5A5h | The array is preconditioned to match the<br>following repeating data pattern:<br>DQ[7:0] = A5h |

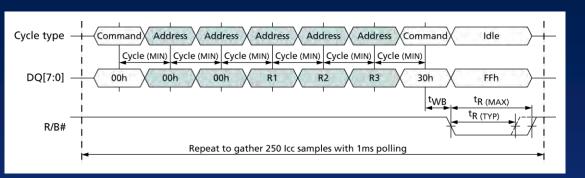

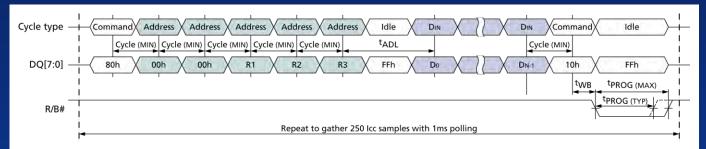

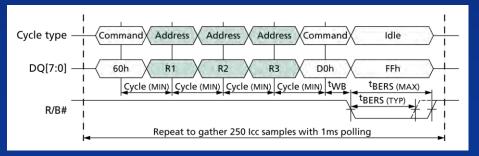

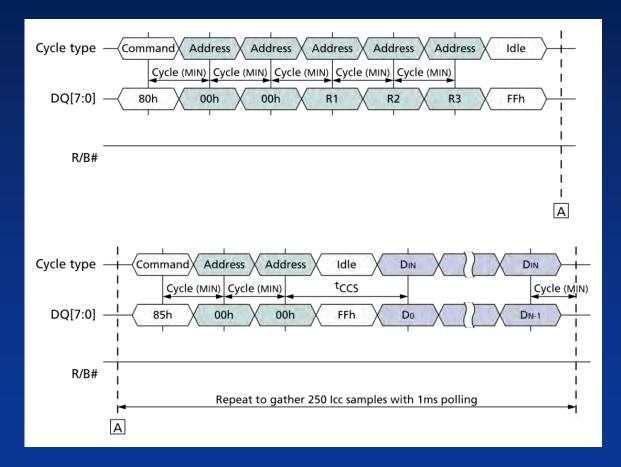

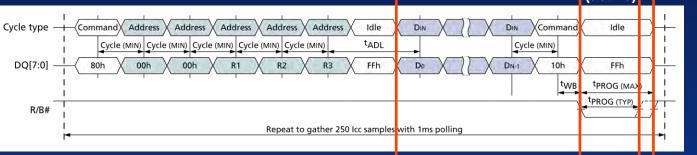

#### **Test Sequences: Array**

Icc1 (Array read) Icc2 (Array program) Icc3 (Array erase)

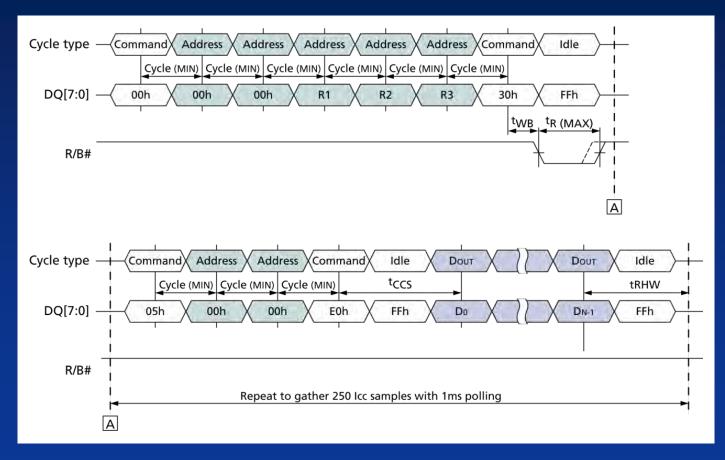

# Test Sequence: Icc4r (I/O Burst Read)

Micron

# Test Sequence: Icc4w (I/O Burst Write)

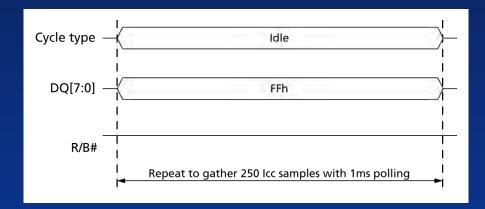

# Test Sequence: Icc5 (Bus Idle)

#### Icc2 (measured) includes Icc4w, Icc2 (active), and Icc5. Icc4w Icc2 (active)

#### Icc2 (measured) can be represented as:

$$Icc2(measured) = \frac{tI0}{tI0 + tPROG(max)}Icc4w + \frac{tPROG(typ)}{tI0 + tPROG(max)}Icc2(active) + \frac{tPROG(max) - tPROG(typ)}{tI0 + tPROG(max)}Icc5$$

$tIO = NAND Page Size(bytes (x8)or words (x16)) \times tWC(min)$

# What is the Active Icc2 Current During tPROG?

#### Solve for Icc2(active)

| Icc2(active) = | $Icc2(measured) \times (tIO + tPROG(max)]$ | $tI0 \times Icc4w$     | $\frac{Icc5 \times tPROG(max)}{PROG(max)} + Icc5$ |

|----------------|--------------------------------------------|------------------------|---------------------------------------------------|

|                | tPROG(typ)                                 | $\frac{1}{tPROG(typ)}$ | tPROG(typ) + $tccs$                               |

It is possible to solve for active currents from the measured values for Icc1, Icc2, and Icc3, which can then be used in power budget modeling.

#### Conclusion

- This presentation shows a better approach to measuring ICC that provides better predictability in the system of how much current devices will draw based on application-specific usage models.

- This test methodology is

- HVM capable

- Reproducible

- Usable for application-specific power budgets

- Adaptable to multiple NAND interfaces

#### Questions and comments?

- This presentation does not include every detail of the new test methodology.

- Micron welcomes feedback and suggestions for improvement; please contact the presentation author.

- The test methodology is subject to further change and improvement.

#### **About Michael Abraham**

- Manager of Micron's NAND Flash Applications Engineering group

- B.S. in Computer Engineering from Brigham Young University

- Technical representative for Micron in ONFI and JEDEC for NAND Flash

- Key role in defining and standardizing the highspeed, synchronous DDR NAND interface within Micron and at ONFI

©2007-2009 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

Santa Clara, CA USA August 2009