## PCIe: do we need anything else?

Dr. Alessandro Fin

- PCle Wiki

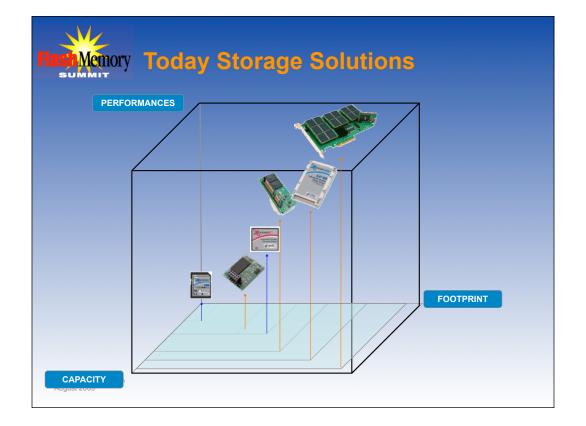

- Today Storage Solutions

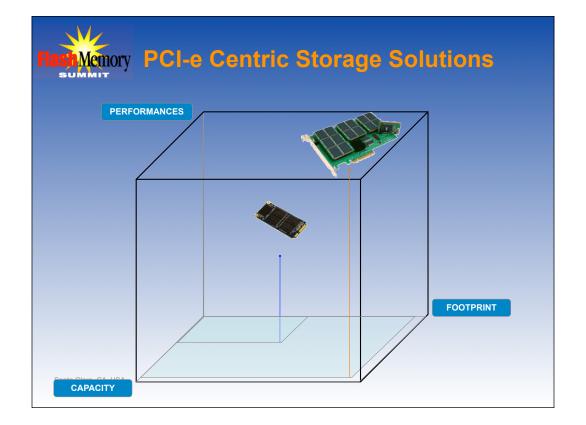

- PCIe Centric Storage Solutions

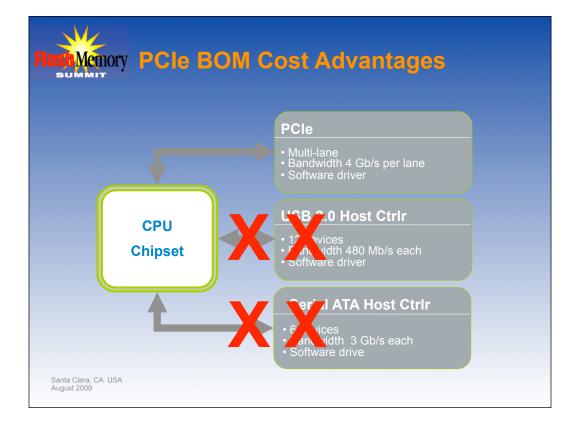

- PCIe Storage Advantages

- PCIe Cost Advantages

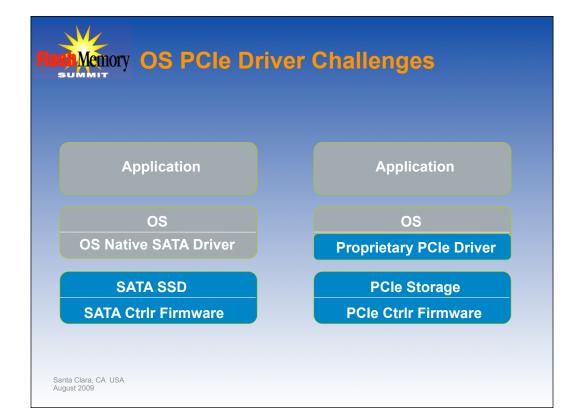

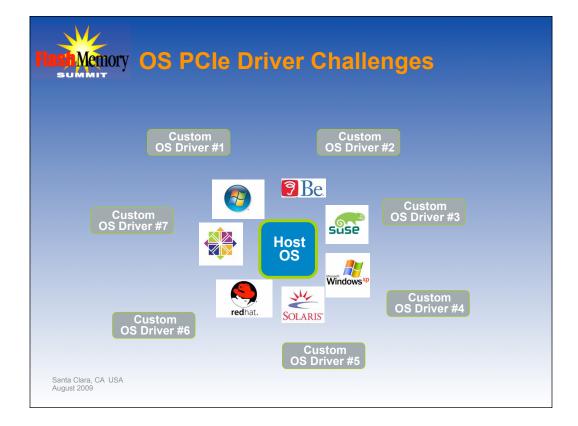

- OS PCIe Driver Challenges & Solution

- Competing Protocols

- Q&A

- Defined in 2004 by IBM, HP, Intel, Dell

- Current generation: 2.0 (2007)

- Communication: serial

- Connection: point to point

- Up to 32 lanes (full duplex TX-RX pair)

- Data rate: 5.0Gb/s x lane

- Options: hot pluggable & external

- Generation 3.0 release: 2010

- Heterogeneous interfaces (6+)

- Heterogeneous OS drivers (6+)

- Heterogeneous form factors (6+)

- Limited performance scalability

- Limited capacity scalability

- Multiple host controllers (6+)

- Bandwidth constrains

Santa Clara, CA USA

- Homogenous interface (1)

- Homogenous OS drivers (1)

- Only 2 form factors

- High performance scalability

- High capacity scalability

- Single host controllers

- Wide bandwidth (multi-lane)

Santa Clara, CA USA

- 1 interface:

- → easier host design

- Homogenous OS drivers:

- → shorter host driver debug cycles

- Only 2 form factors

- → easier host mechanical design

- High performance/bandwidth scalability

- → easier transition to the next gen application requirements

August 2009

- Defines a std programming interface for NVM subsystems

- NVMHCI resisters accessible as PCI devices

- Decoupled NVM management and Storage & Cache algorithms

- Unified OS driver

?!?