# Efficient Coding Schemes for Flash Memories

#### Eitan Yaakobi, Laura Grupp Steven Swanson, Paul H. Siegel, and Jack K. Wolf

Flash Memory Summit, August 2010

- Flash Memory Structure

- Single Bit Representation in MLC Flash

- New ECC Scheme for MLC Flash

- WOM-Codes

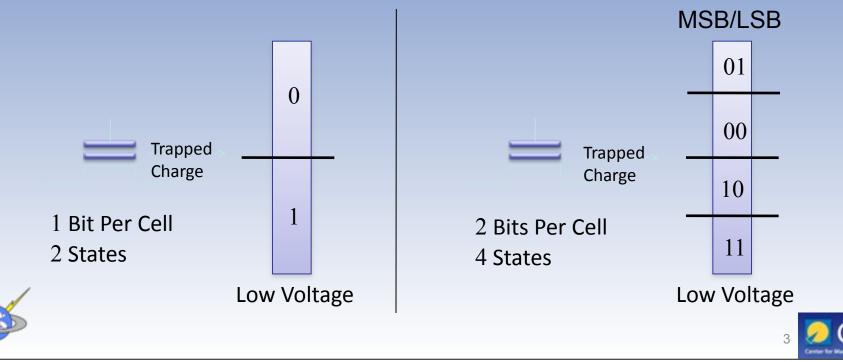

- In SLC flash, each cell stores a single bit

- In MLC, each cell can store multiple bits (typically 2 bits)

#### A group of cells consist of a page

A group of pages consist of a block

- A group of cells consist of a page

- A group of pages consist of a block

- In SLC flash, a typical block layout is as follows

- A group of cells consist of a page

- A group of pages consist of a block

- In SLC flash, a typical block layout is as follows

| page 0  | page 1  |  |  |

|---------|---------|--|--|

| page 2  | page 3  |  |  |

| page 4  | page 5  |  |  |

|         |         |  |  |

|         |         |  |  |

| -       | -       |  |  |

| page 62 | page 63 |  |  |

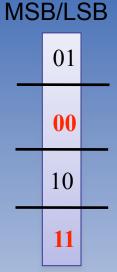

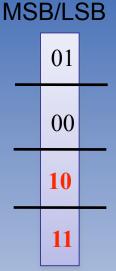

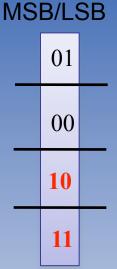

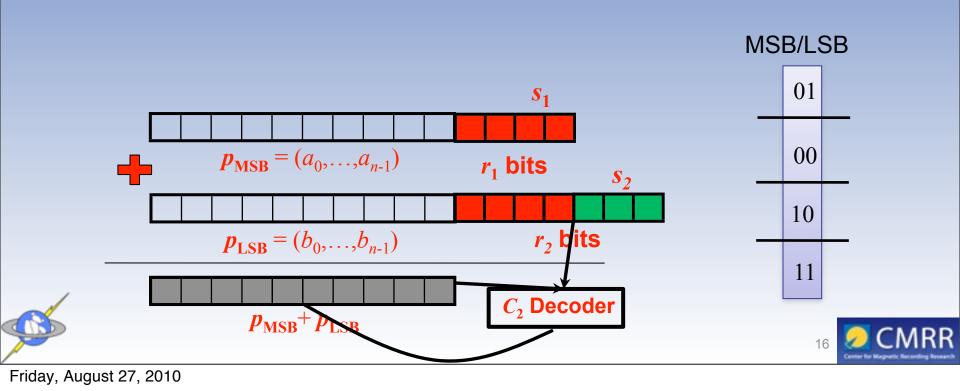

In MLC flash the two bits within a cell DO NOT belong to the same page – MSB page and LSB page

In MLC flash the two bits within a cell DO NOT belong to the same page – MSB page and LSB page

MSB/LSB

- In MLC flash the two bits within a cell DO NOT belong to the same page – MSB page and LSB page

- Given a group of cells, all the MSB's consist of one page and all the LSB's consist of another page

## ashMemory Flash Memory Struct

MSB/LSB

01

00

10

11

- In MLC flash the two bits within a cell DO NOT belong to the same page – MSB page and LSB page

- Given a group of cells, all the MSB's consist of one page and all the LSB's consist of another page

|   | Row<br>index | MSB of first<br>2 <sup>14</sup> cells | LSB of first<br>2 <sup>14</sup> cells | MSB of last<br>2 <sup>14</sup> cells | LSB of last<br>2 <sup>14</sup> cells |

|---|--------------|---------------------------------------|---------------------------------------|--------------------------------------|--------------------------------------|

|   | 1            | page 0                                | page 4                                | page 1                               | page 5                               |

| ĺ | 2            | page 2                                | page 8                                | page 3                               | page 9                               |

|   | 3            | page 6                                | page 12                               | page 7                               | page 13                              |

|   | 4            | page 10                               | page 16                               | page 11                              | page 17                              |

|   | •            | •                                     | •                                     | •                                    | •                                    |

|   | 31           | page 118                              | page 124                              | page 119                             | page 125                             |

|   | 32           | page 122                              | page 126                              | page 123                             | page 127                             |

5

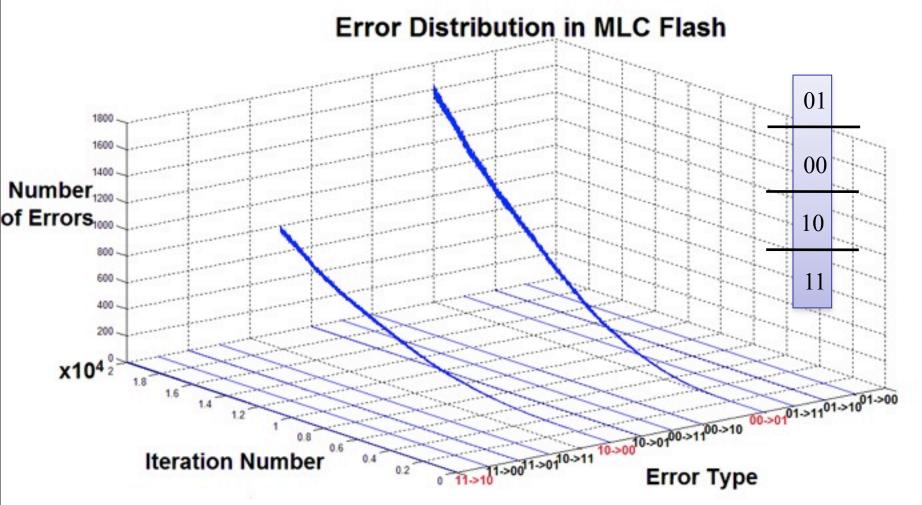

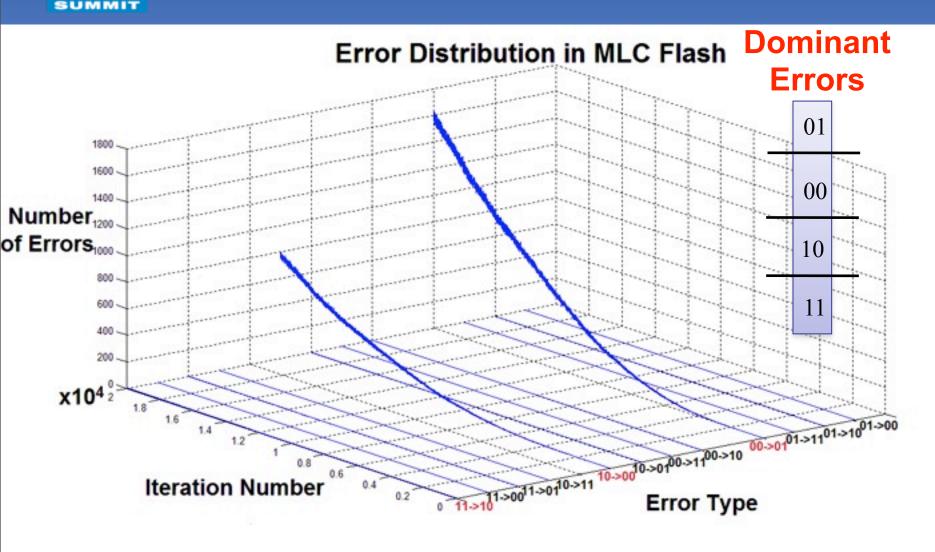

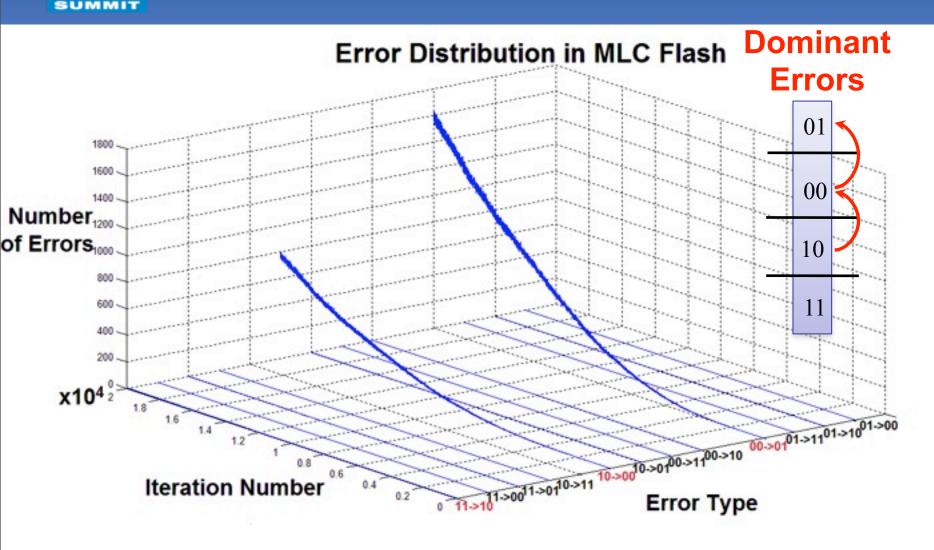

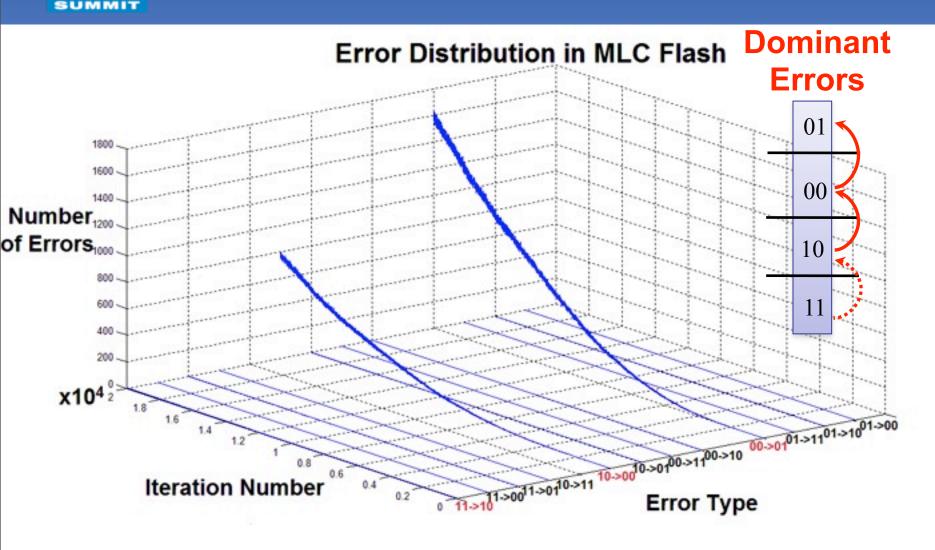

### Flash Memory Experiment Description

We checked several flash memory MLC blocks

- We checked several flash memory MLC blocks

- For each block the following steps are repeated

6 🙋 CMRR

- We checked several flash memory MLC blocks

- For each block the following steps are repeated

- The block is erased

CMRR

- We checked several flash memory MLC blocks

- For each block the following steps are repeated

- The block is erased

- A pseudo-random data is written to the block

### Memory Experiment Description

- We checked several flash memory MLC blocks

- For each block the following steps are repeated

- The block is erased

- A pseudo-random data is written to the block

- The data is read and compared to find errors

#### **Experiment Description**

- We checked several flash memory MLC blocks

- For each block the following steps are repeated

- The block is erased

- A pseudo-random data is written to the block

- The data is read and compared to find errors

- Remarks:

#### **Experiment Description**

- We checked several flash memory MLC blocks

- For each block the following steps are repeated

- The block is erased

- A pseudo-random data is written to the block

- The data is read and compared to find errors

- Remarks:

- We measured many more iterations than the manufacturer's guaranteed number of erasures

### **Experiment Description**

- We checked several flash memory MLC blocks

- For each block the following steps are repeated

- The block is erased

- A pseudo-random data is written to the block

- The data is read and compared to find errors

#### Remarks:

- We measured many more iterations than the manufacturer's guaranteed number of erasures

- The experiment was done in a lab conditions and related factors such as temperature change, intervals between erasures or multiple readings before erasures were not considered

## UCSD

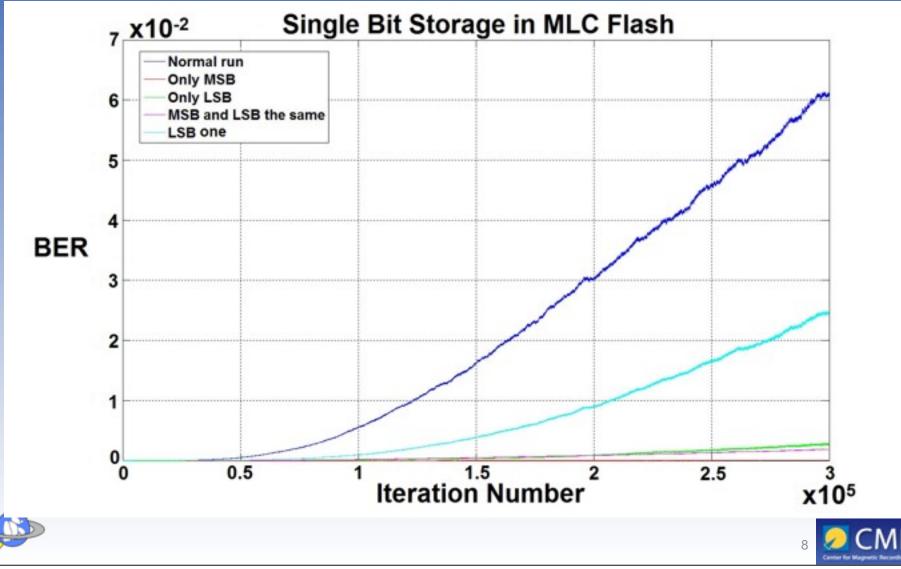

#### Flash Memory Single Bit Representation in MLC Flash

How to store a single bit in MLC flash?

- How to store a single bit in MLC flash?

- There are several ways:

- How to store a single bit in MLC flash?

- There are several ways:

- How to store a single bit in MLC flash?

- There are several ways:

- Program only the MSB pages

- How to store a single bit in MLC flash?

- There are several ways:

- Program only the MSB pages

- How to store a single bit in MLC flash?

- There are several ways:

- Program only the MSB pages

- Program only the LSB pages

- How to store a single bit in MLC flash?

- There are several ways:

- Program only the MSB pages

- Program only the LSB pages

(cells can be in state 11 or 00)

There are several ways: Program only the MSB pages

How to store a single bit in MLC flash?

- Program only the LSB pages

- - Program the LSB and MSB pages with the same values

- How to store a single bit in MLC flash?

- There are several ways:

- Program only the MSB pages

- Program only the LSB pages

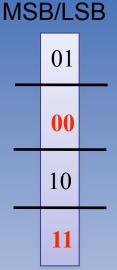

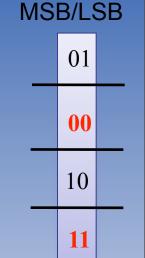

- Program the LSB and MSB pages with the same values (cells can be in state 11 or 00)

- Program the data in the MSB pages, and program all LSB pages to all-1 bit values (cells can be in state 00 or 01)

- How to store a single bit in MLC flash?

- There are several ways:

- Program only the MSB pages

- Program only the LSB pages

- Program the LSB and MSB pages with the same values (cells can be in state 11 or 00)

- Program the data in the MSB pages, and program all LSB pages to all-1 bit values (cells can be in state 00 or 01)

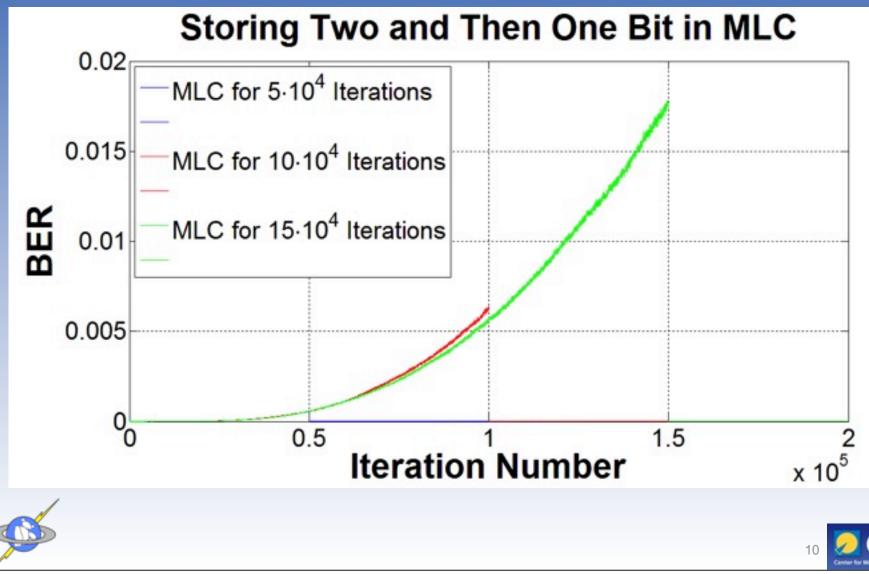

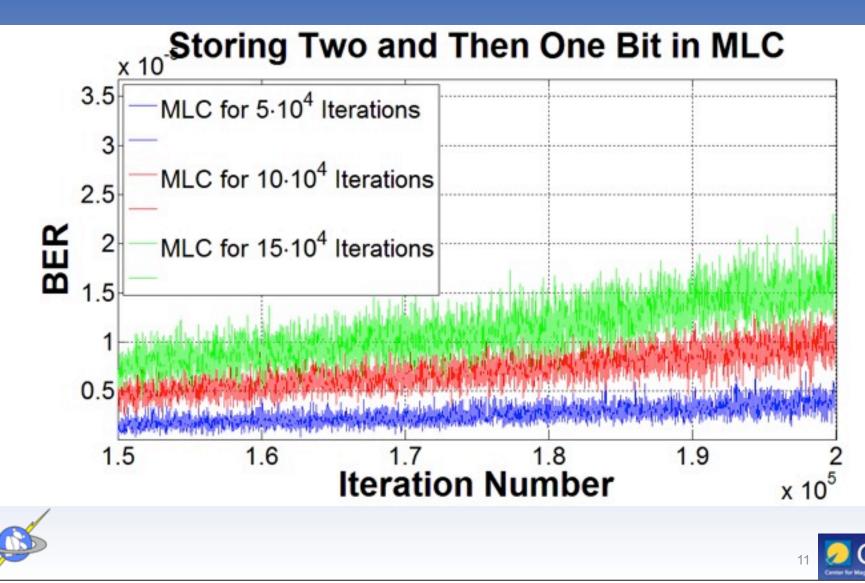

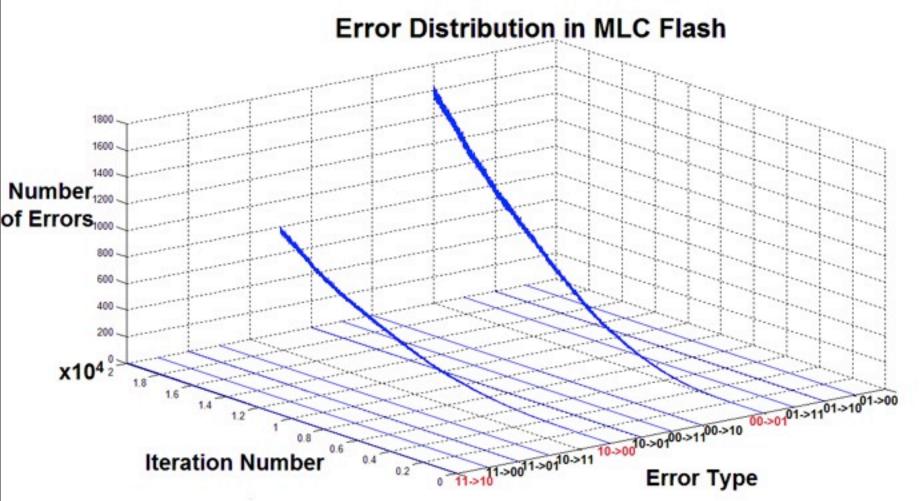

- What happens when the chip is first used as an MLC and then switched to be used as an SLC?

- We ran the following experiments:

- Use the chip for 50,000 iterations as an MLC and 150,000 iterations as an SLC

- Use the chip for 100,000 iterations as an MLC and 100,000 iterations as an SLC

- Use the chip for 150,000 iterations as an MLC and 50,000 iterations as an SLC

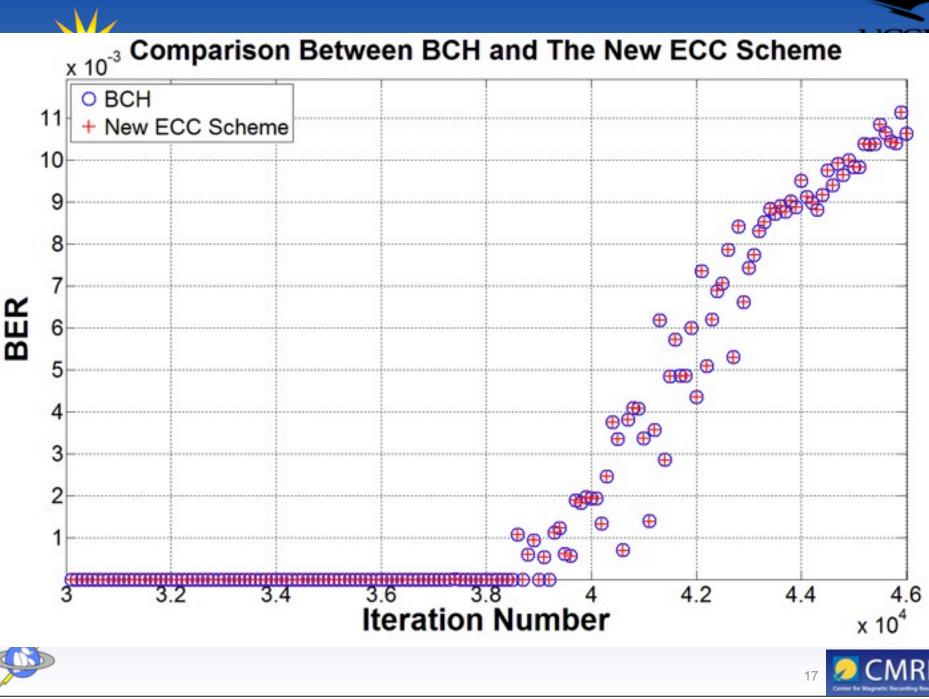

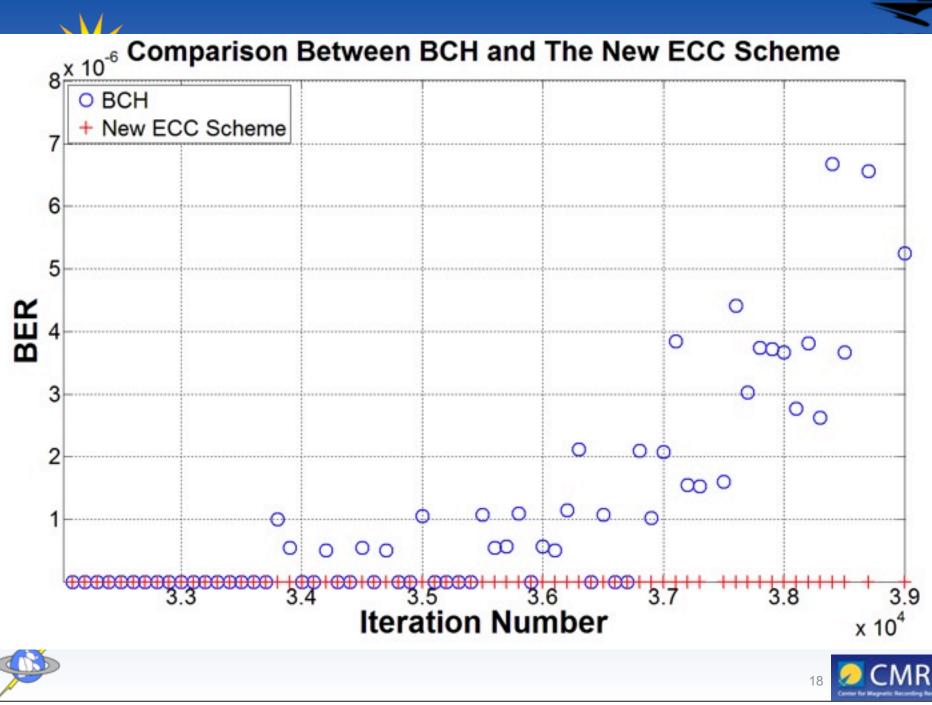

#### A common ECC in flash today is a BCH code

- A common ECC in flash today is a **BCH code**

- Errors are corrected in each page independently

- A common ECC in flash today is a BCH code

- Errors are corrected in each page independently

- In particular, in a pair of SLC and MLC pages sharing the same group of cells, errors are still corrected independently

- A common ECC in flash today is a BCH code

- Errors are corrected in each page independently

- In particular, in a pair of SLC and MLC pages sharing the same group of cells, errors are still corrected independently

- Our goal: to correct errors in a pair of pages together

- A common ECC in flash today is a BCH code

- Errors are corrected in each page independently

- In particular, in a pair of SLC and MLC pages sharing the same group of cells, errors are still corrected independently

- Our goal: to correct errors in a pair of pages together

- If a cell is in error, its level will typically increase by one level

13 ZCMRR

13 ZCMRR

13 ZCMRR

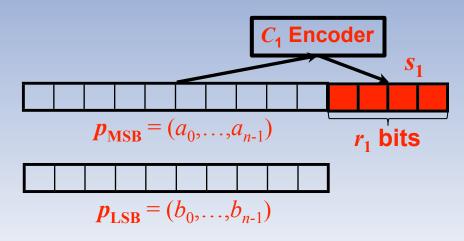

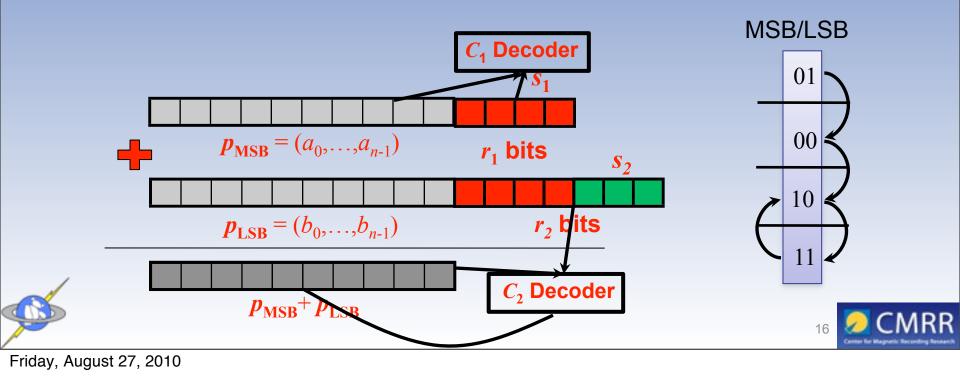

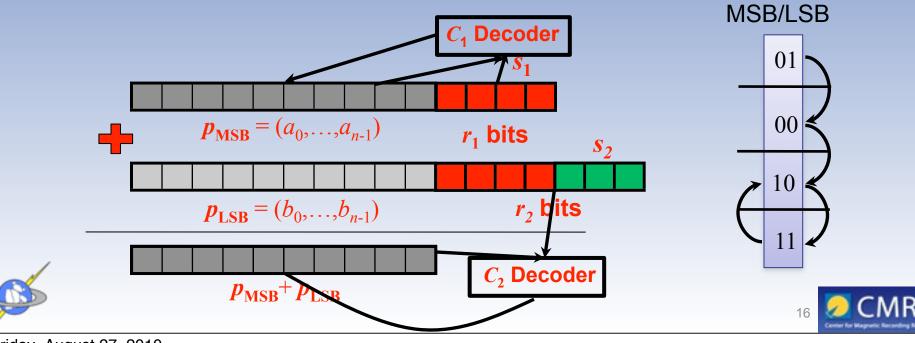

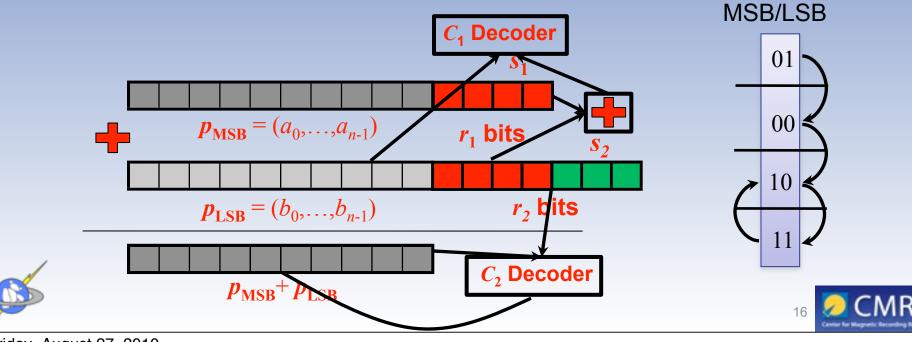

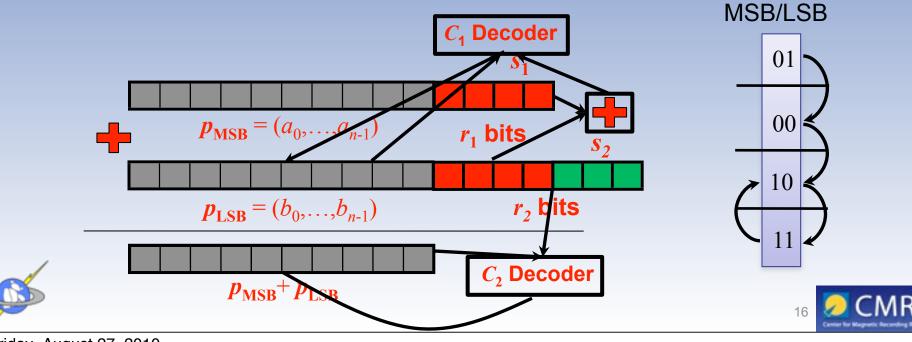

#### How to correct errors in a pair of pages together?

- How to correct errors in a pair of pages together?

- First, one level errors are corrected and then the other errors

- How to correct errors in a pair of pages together?

- First, one level errors are corrected and then the other errors

- Code construction:

- How to correct errors in a pair of pages together?

- First, one level errors are corrected and then the other errors

- Code construction:

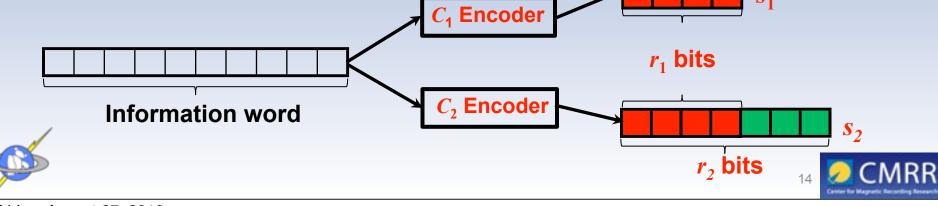

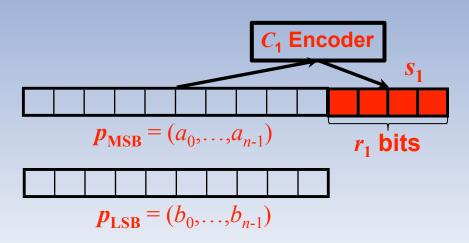

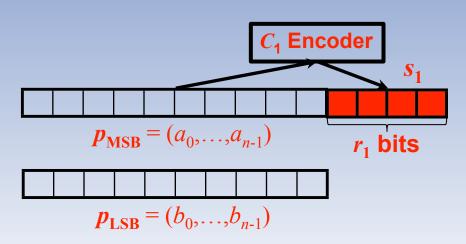

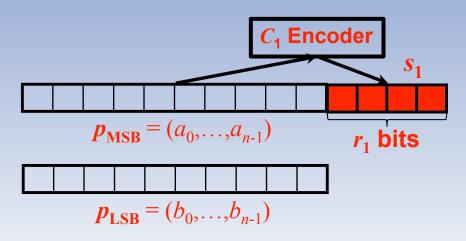

- $C_1$  is a  $t_1$ -error-correcting BCH code

- $C_2$  is a  $t_2$ -error-correcting BCH code, where  $t_2 > t_1$

- How to correct errors in a pair of pages together?

- First, one level errors are corrected and then the other errors

- Code construction:

- $C_1$  is a  $t_1$ -error-correcting BCH code  $C_2$  is a  $t_2$ -error-correcting BCH code, where  $t_2 > t_1$

- The codes are "compatible" For the same information word, the r<sub>1</sub> redundancy bits generated by the encoder of C<sub>1</sub> are identical to the first r<sub>1</sub> redundancy bits generated by the encoder of C<sub>2</sub>

- How to correct errors in a pair of pages together?

- First, one level errors are corrected and then the other errors

- Code construction:

- $C_1$  is a  $t_1$ -error-correcting BCH code  $C_2$  is a  $t_2$ -error-correcting BCH code, where  $t_2 > t_1$

- The codes are "compatible" For the same information word, the r<sub>1</sub> redundancy bits generated by the encoder of C<sub>1</sub> are identical to the first r<sub>1</sub> redundancy bits generated by the encoder of C<sub>2</sub>

- How to correct errors in a pair of pages together?

- First, one level errors are corrected and then the other errors

- Code construction:

Information word

- $C_1$  is a  $t_1$ -error-correcting BCH code  $C_2$  is a  $t_2$ -error-correcting BCH code, where  $t_2 > t_1$

- The codes are "compatible" For the same information word, the  $r_1$  redundancy bits generated by the encoder of  $C_1$  are identical to the first  $r_1$ redundancy bits generated by the encoder of  $C_2$

C<sub>1</sub> Encoder

$r_1$  bits

- How to correct errors in a pair of pages together?

- First, one level errors are corrected and then the other errors

- Code construction:

- $C_1$  is a  $t_1$ -error-correcting BCH code  $C_2$  is a  $t_2$ -error-correcting BCH code, where  $t_2 > t_1$

- The codes are "compatible" For the same information word, the  $r_1$  redundancy bits generated by the encoder of  $C_1$  are identical to the first  $r_1$ redundancy bits generated by the encoder of  $C_2$

#### Code construction:

#### Code construction:

- Code construction:

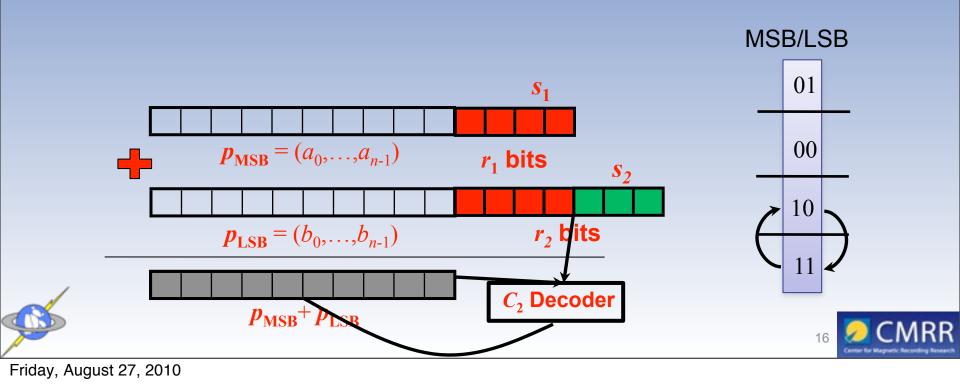

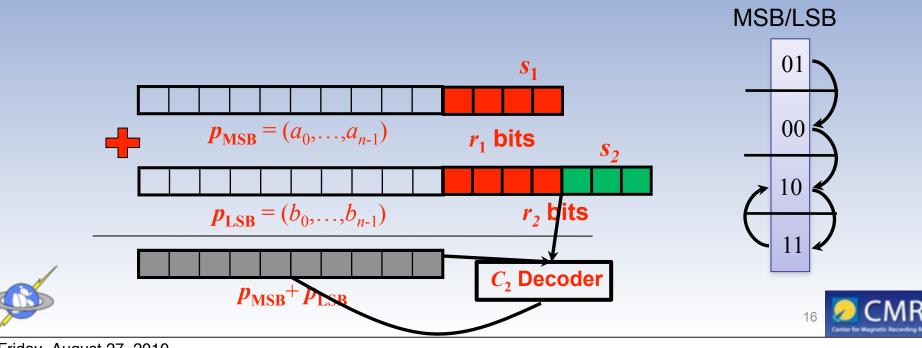

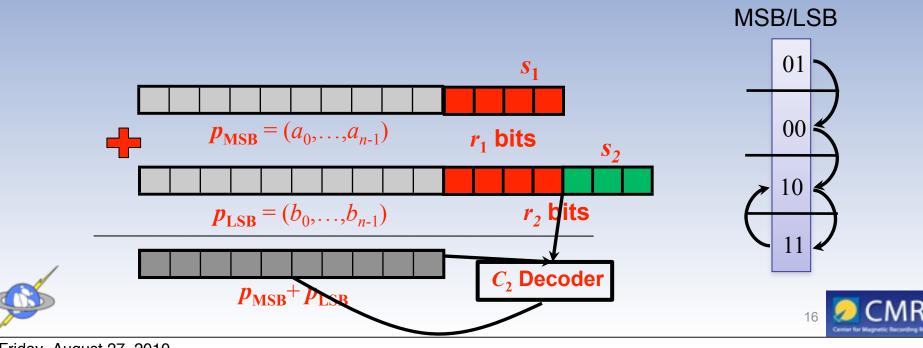

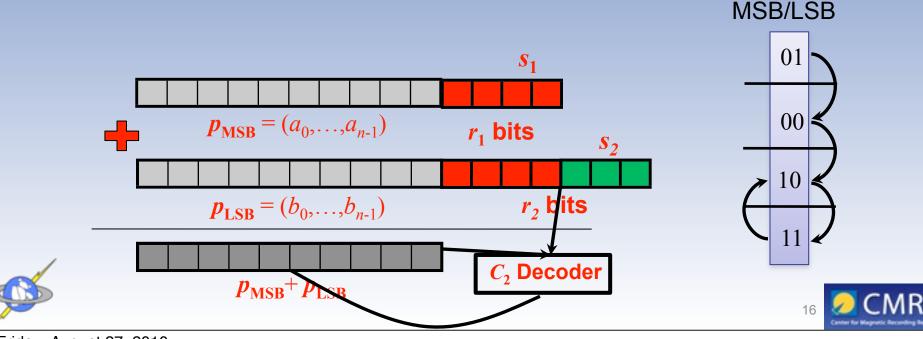

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

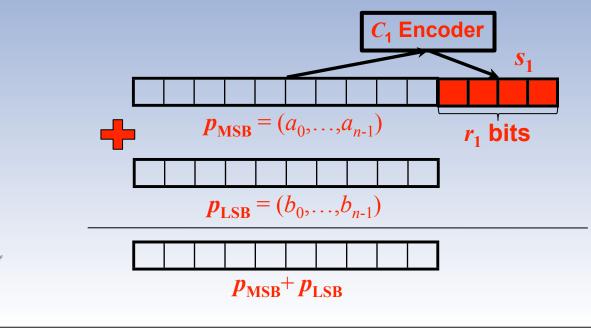

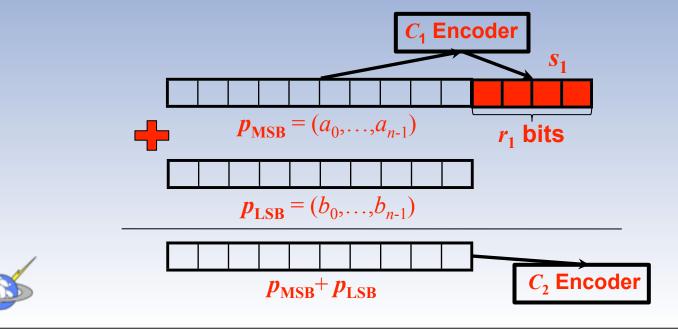

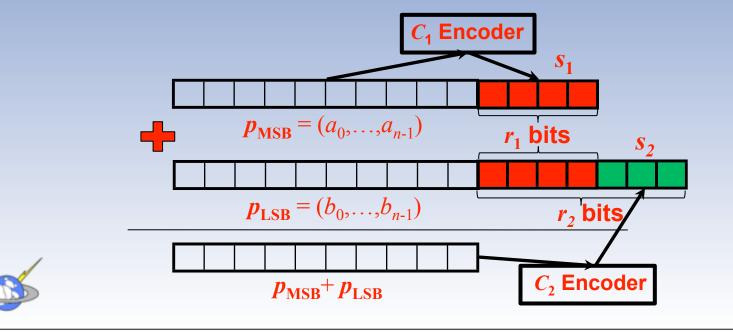

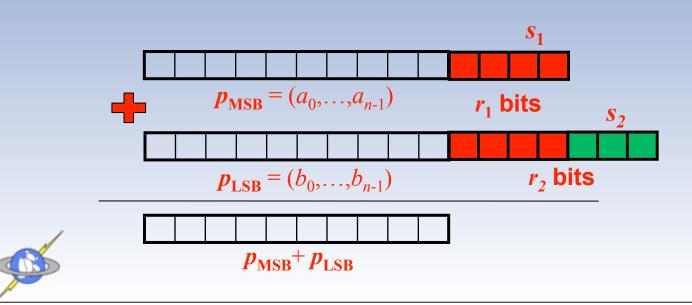

- Encoding:

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Encoding:

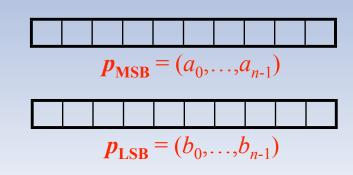

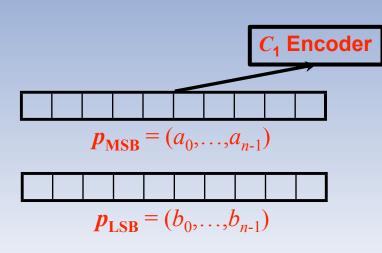

- $p_{\text{MSB}} = (a_0, \dots, a_{n-1})$  and  $p_{\text{LSB}} = (b_0, \dots, b_{n-1})$  share the same group of cells.

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Encoding:

- $p_{\text{MSB}} = (a_0, \dots, a_{n-1})$  and  $p_{\text{LSB}} = (b_0, \dots, b_{n-1})$  share the same group of cells.

- Calculate  $s_1$ , the  $r_1$  redundancy bits of  $C_1$  corresponding to  $p_{MSB}$

# FlashMemory

## Memory ECC scheme for MLC flash

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Encoding:

- $p_{\text{MSB}} = (a_0, \dots, a_{n-1})$  and  $p_{\text{LSB}} = (b_0, \dots, b_{n-1})$  share the same group of cells.

- Calculate  $s_1$ , the  $r_1$  redundancy bits of  $C_1$  corresponding to  $p_{MSB}$

# Flash Memory

## Memory ECC scheme for MLC flash

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Encoding:

- $p_{\text{MSB}} = (a_0, \dots, a_{n-1})$  and  $p_{\text{LSB}} = (b_0, \dots, b_{n-1})$  share the same group of cells.

- Calculate  $s_1$ , the  $r_1$  redundancy bits of  $C_1$  corresponding to  $p_{MSB}$

- Code construction:

- C<sub>1</sub> is a t<sub>1</sub>-error-correcting BCH code, C<sub>2</sub> is a t<sub>2</sub>-error-correcting BCH code, where t<sub>2</sub> > t<sub>1</sub>, and the codes are compatible

- Encoding:

- $p_{\text{MSB}} = (a_0, \dots, a_{n-1})$  and  $p_{\text{LSB}} = (b_0, \dots, b_{n-1})$  share the same group of cells.

- Calculate  $s_1$ , the  $r_1$  redundancy bits of  $C_1$  corresponding to  $p_{MSB}$

16

16

16 **CMRR**

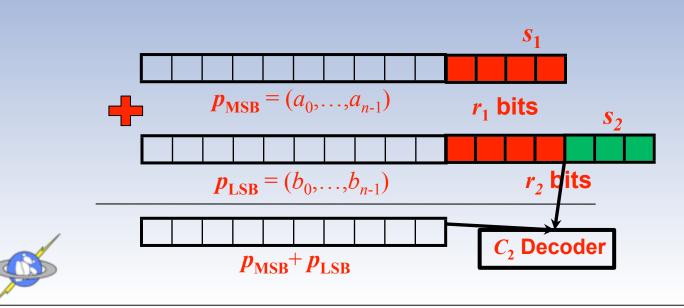

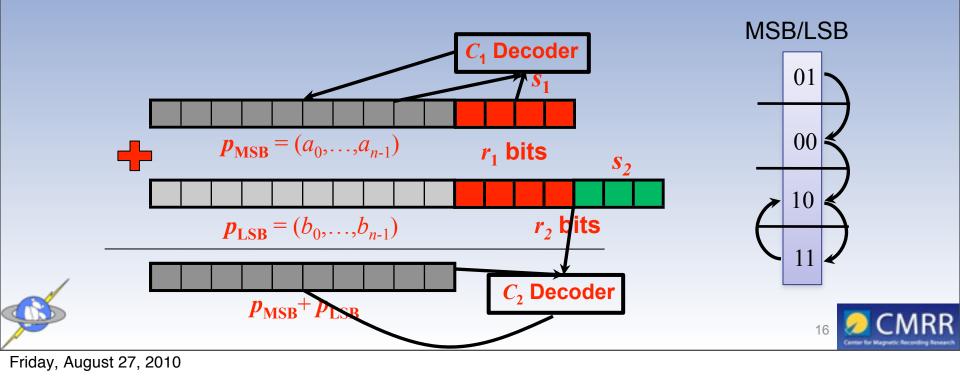

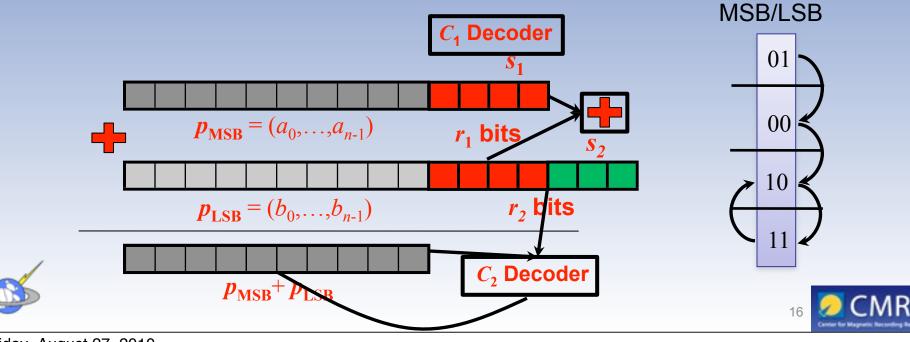

## FlashMemory ECC scheme for MLC flash Decoding:

• Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

#### **Sh**Memory ECC scheme for MLC flash Decoding:

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

Friday, August 27, 2010

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Level 00 is changed to level 10 and level 01 is changed to level 00

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Level 00 is changed to level 10 and level 01 is changed to level 00

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Level 00 is changed to level 10 and level 01 is changed to level 00

## **Sh**Memory ECC scheme for MLC flash Decoding:

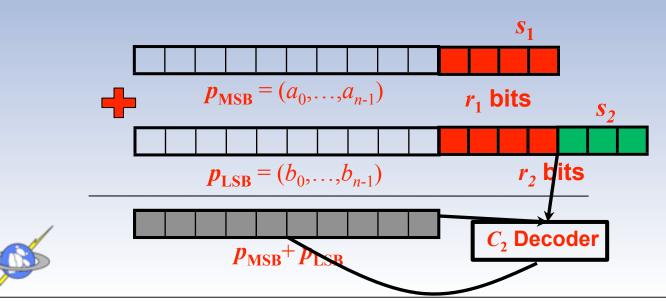

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Level 00 is changed to level 10 and level 01 is changed to level 00

- Using the  $r_1$  bits of  $s_1$ , find up to  $t_1$  errors in  $p_{\text{MSB}}$

## **Sh**Memory ECC scheme for MLC flash Decoding:

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Level 00 is changed to level 10 and level 01 is changed to level 00

- Using the  $r_1$  bits of  $s_1$ , find up to  $t_1$  errors in  $p_{\text{MSB}}$

## **Sh**Memory ECC scheme for MLC flash Decoding:

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Level 00 is changed to level 10 and level 01 is changed to level 00

- Using the  $r_1$  bits of  $s_1$ , find up to  $t_1$  errors in  $p_{\text{MSB}}$

Friday, August 27, 2010

- Using the  $r_2$  bits of  $s_2$  find up to  $t_2$  errors in  $p_{MSB} + p_{LSB}$

- Change the state of erroneous cells as follows:

- Level 11 is changed to level 10 and vice versa

- Level 00 is changed to level 10 and level 01 is changed to level 00

- Using the  $r_1$  bits of  $s_1$ , find up to  $t_1$  errors in  $p_{\text{MSB}}$

Friday, August 27, 2010

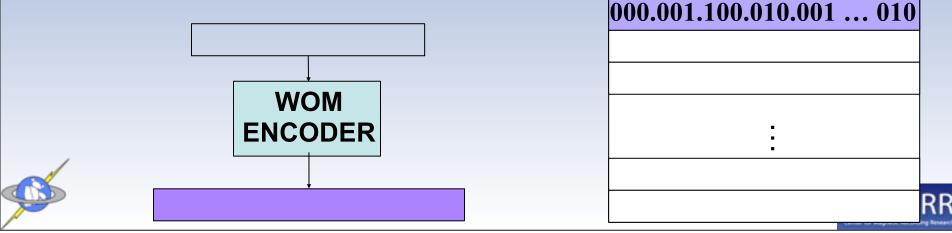

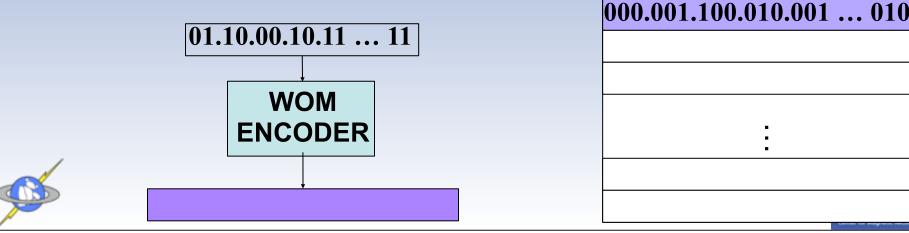

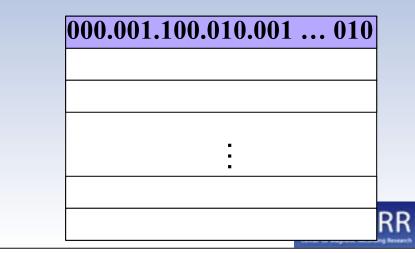

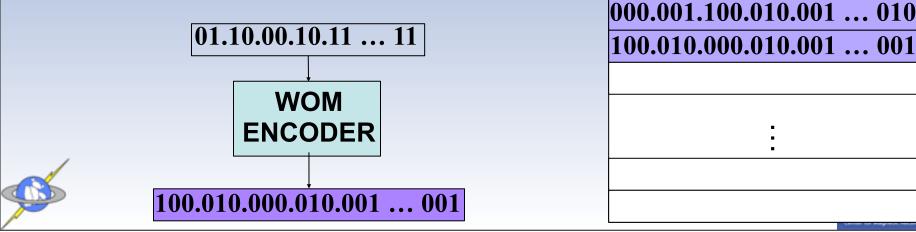

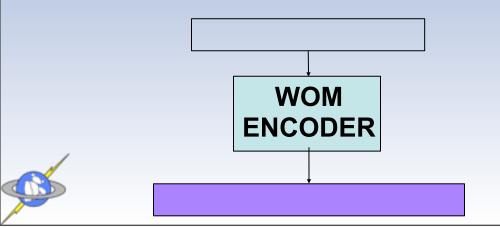

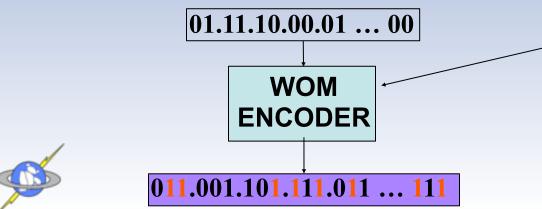

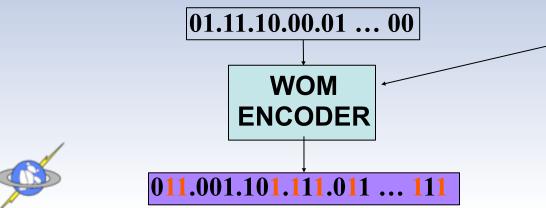

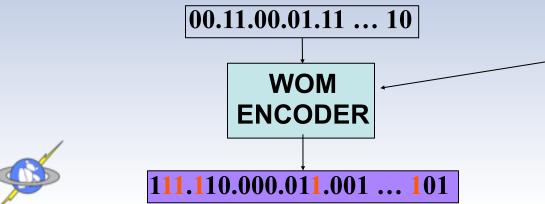

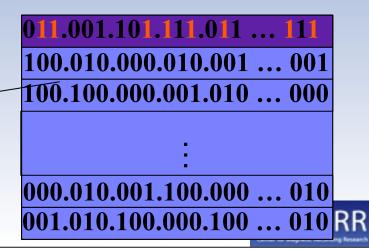

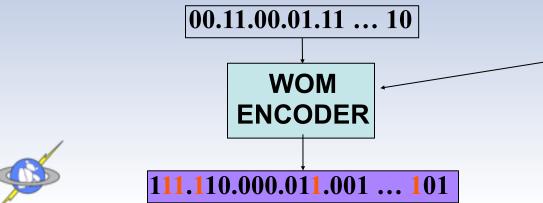

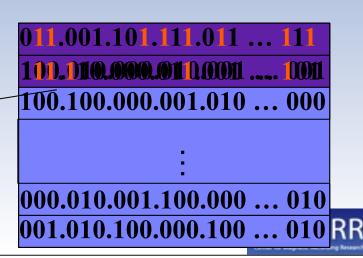

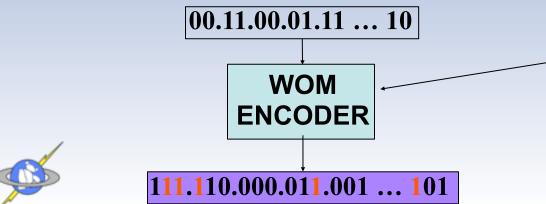

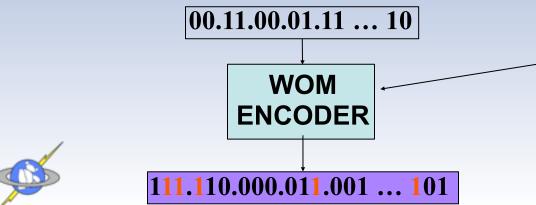

# FlashMemory Write Once Memory (WOM) UCSD Codes for SLC

## FlashMemory Write Once Memory (WOM) UCSD Codes for SLC

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

A scheme for storing two bits twice using only three cells before erasing the cells

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

A scheme for storing two bits twice using only three cells before erasing the cells

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

## Write Once Memory (WOM) UCSD

A scheme for storing two bits twice using only three cells before erasing the cells

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

|       | 1 <sup>st</sup><br>write | 2 <sup>nd</sup><br>write |

|-------|--------------------------|--------------------------|

| data  |                          |                          |

| cells |                          |                          |

A scheme for storing two bits twice using only three cells before erasing the cells

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

|       | 1 <sup>st</sup><br>write | 2 <sup>nd</sup><br>write |

|-------|--------------------------|--------------------------|

| data  | 01                       |                          |

| cells | 100                      |                          |

A scheme for storing two bits twice using only three cells before erasing the cells

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

|       | 1 <sup>st</sup><br>write | 2 <sup>nd</sup><br>write |

|-------|--------------------------|--------------------------|

| data  | 01                       | 11                       |

| cells | 100                      | 110                      |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

|       | 1 <sup>st</sup><br>write | 2 <sup>nd</sup><br>write |

|-------|--------------------------|--------------------------|

| data  | 01                       | 11                       |

| cells | 100                      | 110                      |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

|       | 1 <sup>st</sup><br>write | 2 <sup>nd</sup><br>write |

|-------|--------------------------|--------------------------|

| data  | 01                       | 11                       |

| cells | 100                      | 110                      |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

Friday, August 27, 2010

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

RR

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

RR

Friday, August 27, 2010

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

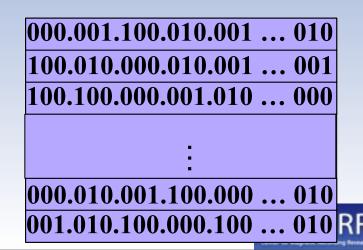

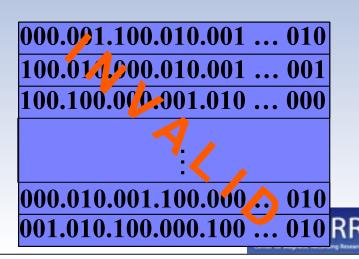

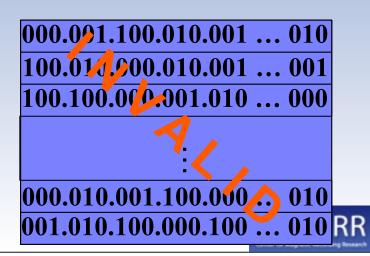

| 000.001.100.010.001 010 |

|-------------------------|

| 100.010.000.010.001 001 |

| 100.100.000.001.010 000 |

|                         |

|                         |

|                         |

RR

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

| 000.001.100.01 | 10.001 010 |

|----------------|------------|

| 100.010.000.0  | 10.001 001 |

| 100.100.000.00 | 01.010 000 |

|                |            |

|                | :          |

|                | •          |

|                |            |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

|      | 001.10<br>010.00 |        |       |         |

|------|------------------|--------|-------|---------|

|      |                  |        |       |         |

| 1000 |                  |        |       | <br>    |

|      |                  | •      |       |         |

|      |                  | •      |       |         |

| 000. | 010.00           | )1.10( | 0.000 | <br>010 |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

Friday, August 27, 2010

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

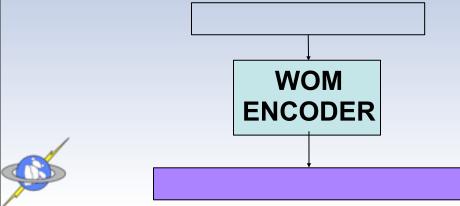

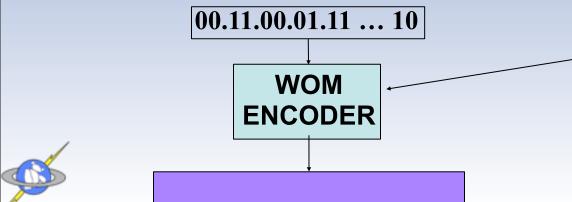

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

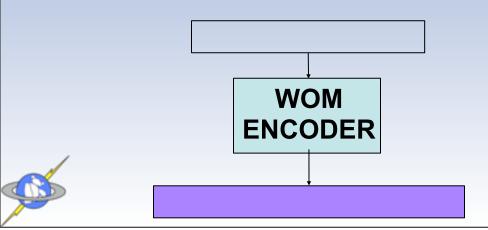

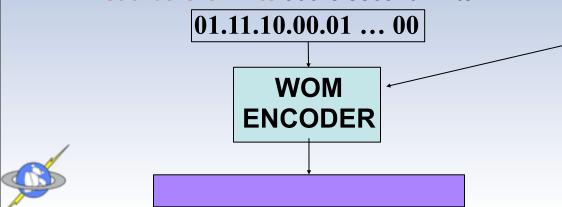

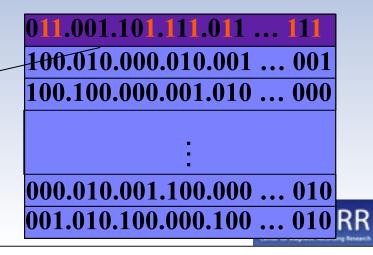

- Pages are encoded using the WOM code

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

Friday, August 27, 2010

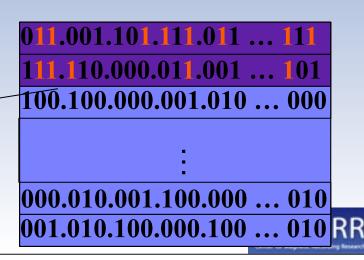

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores 2KB/1.5 = 4/3KB per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

Friday, August 27, 2010

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

Friday, August 27, 2010

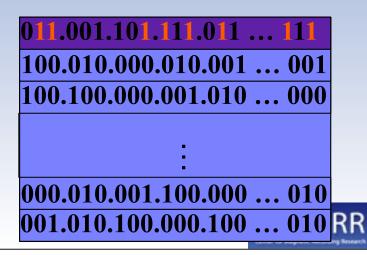

# Write Once Memory (WOM) UCSD Codes for SLC

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

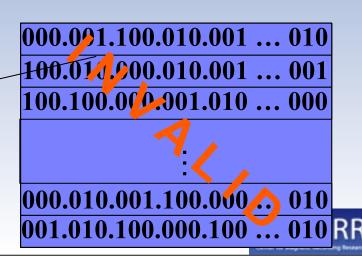

000.091.100.010.001 ... 010

1<del>00.011.0</del>00.010.001 ... 001

100.100.000.001.010 ... 000

000.010.001.100.000 010

001.010.100.000.100 ... 010

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

|      |                       |                       |

Cells state

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores 2KB/1.5 = 4/3KB per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

|      |                       |                       |

Cells state

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

Friday, August 27, 2010

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

|      |                       |                       |

Cells state

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores 2KB/1.5 = 4/3KB per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores 2KB/1.5 = 4/3KB per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

Friday, August 27, 2010

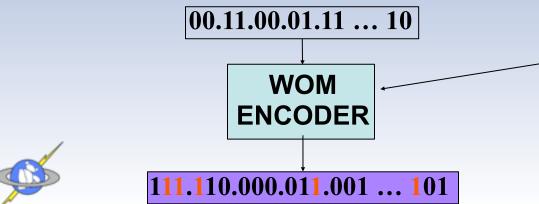

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

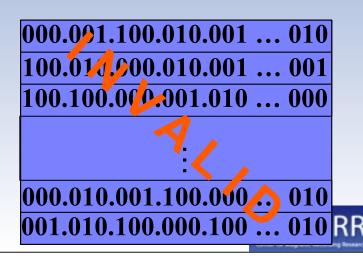

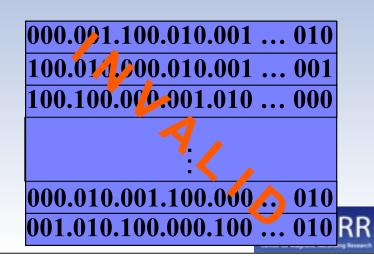

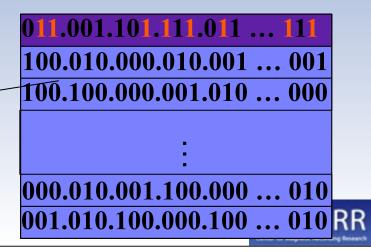

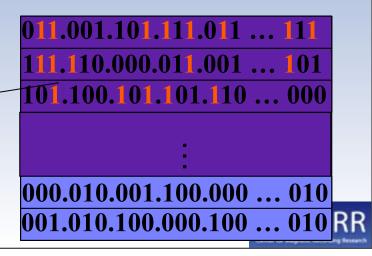

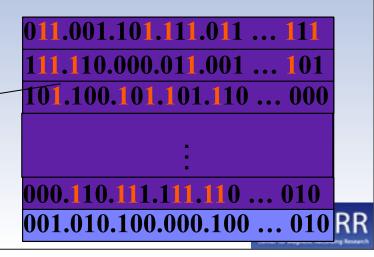

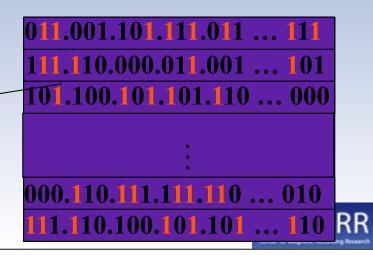

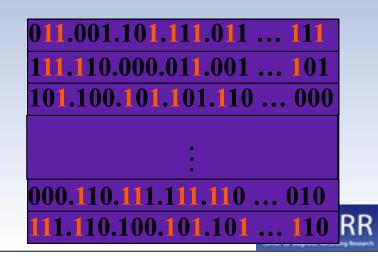

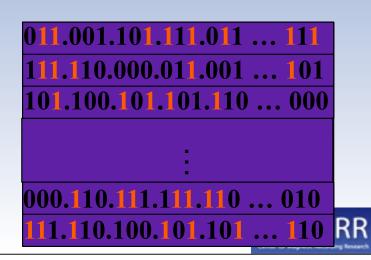

011.001.101.111.011 ... 111 111.110.000.011.001 ... 101 101.100.101.101.110 ... 000 ... 010 000.010.001.100.000 ... 010 001.010.100.000.100 ... 010 RR

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores 2KB/1.5 = 4/3KB per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

|      |                       |                       |

Cells state

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores 2KB/1.5 = 4/3KB per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

|      |                       |                       |

Cells state

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|------|-----------------------|-----------------------|

| 00   | 000                   | 111                   |

| 01   | 100                   | 011                   |

| 10   | 010                   | 101                   |

| 11   | 001                   | 110                   |

|      |                       |                       |

Cells state

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

- A scheme for storing two bits twice using only three cells before erasing the cells

- The cells only increase their level

- How to implement? (in SLC block)

- Each page stores **2KB/1.5** = **4/3KB** per write

- A page can be written twice before erasing

- Pages are encoded using the WOM code

- When the block has to be rewritten, mark its pages as **invalid**

- Again write pages using the WOM code without erasing

- Read before write at the second write

#### Advantages:

- The number of bits written per cell is 4/3

- Possible to write twice before a physical erasure

| data        | 1 <sup>st</sup> write | 2 <sup>nd</sup> write |

|-------------|-----------------------|-----------------------|

| 00          | 000                   | 111                   |

| 01          | 100                   | 011                   |

| 10          | 010                   | 101                   |

| 11          | 001                   | 110                   |

| Cells state |                       |                       |

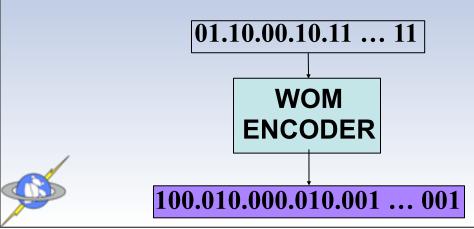

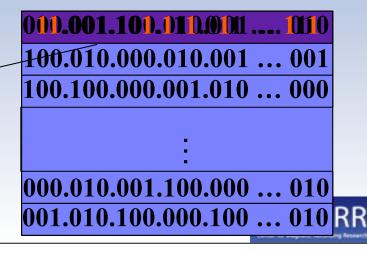

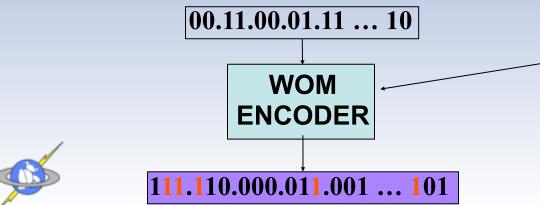

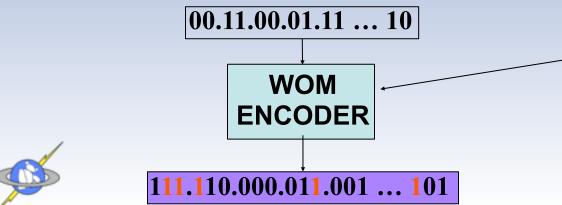

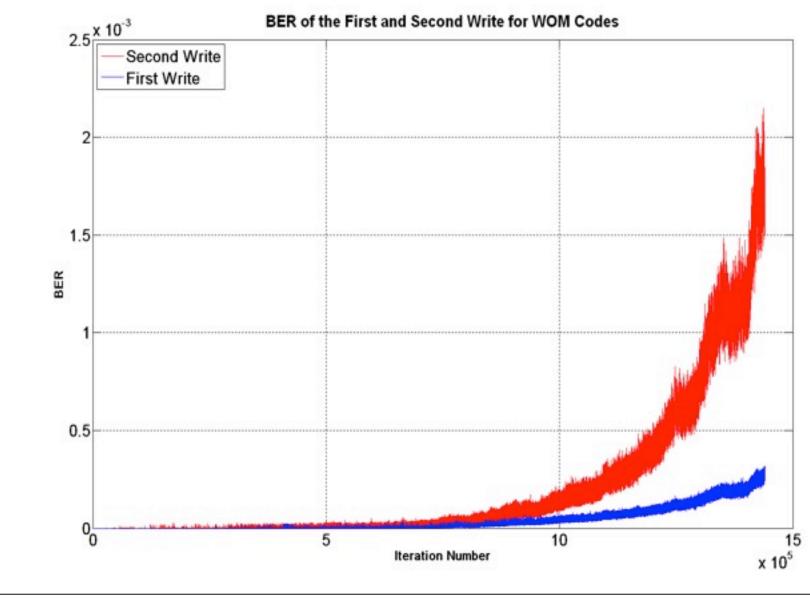

#### Flash Memory WOM-Codes with two writes

• First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

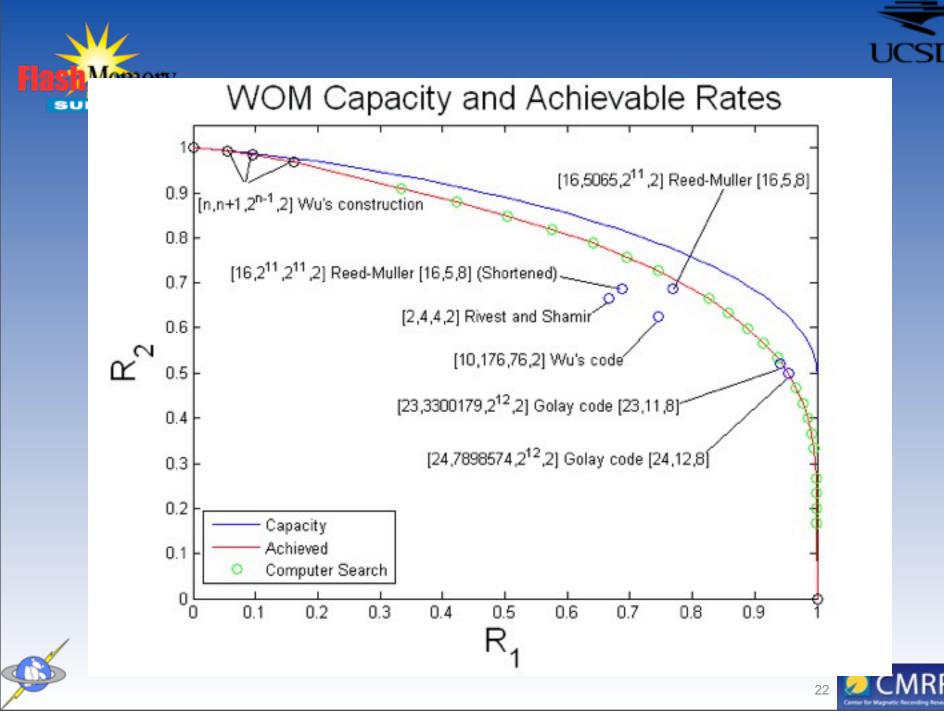

- Assume there are *n* cells and two writes, *t* = 2

- First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)

$C = \{ (R_1, R_2) \mid \$p \in [0, 0.5], R_1 \le h(p), R_2 \le 1 - p \}$

#### emory WOM-Codes with two writes

- Assume there are *n* cells and two writes, *t* = 2

- First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)

$C = \{ (R_1, R_2) \mid \$p \in [0, 0.5], R_1 \le h(p), R_2 \le 1 - p \}$

The WOM-rate  $R = R_1 + R_2 \le \log_2(3) \gg 1.58$ , achieved for p = 1/3

#### mory WOM-Codes with two writes

- Assume there are *n* cells and two writes, *t* = 2

- First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)

$C = \{ (R_1, R_2) \mid \$p \in [0, 0.5], R_1 \le h(p), R_2 \le 1 - p \}$

The WOM-rate  $R = R_1 + R_2 \le \log_2(3) \gg 1.58$ , achieved for p = 1/3

Rivest and Shamir constructed WOM-codes of rates (2/3, 2/3) and (0.67, 0.67), R =1.34

#### mory WOM-Codes with two writes

- Assume there are *n* cells and two writes, *t* = 2

- First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)

$C = \{ (R_1, R_2) \mid \$p \in [0, 0.5], R_1 \le h(p), R_2 \le 1 - p \}$

The WOM-rate  $R = R_1 + R_2 \le \log_2(3) \gg 1.58$ , achieved for p = 1/3

- Rivest and Shamir constructed WOM-codes of rates (2/3, 2/3) and (0.67, 0.67), R =1.34

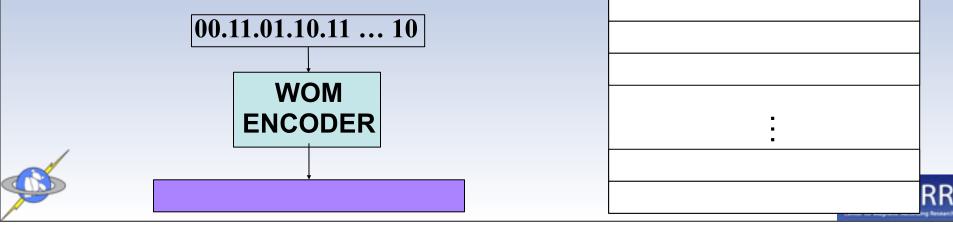

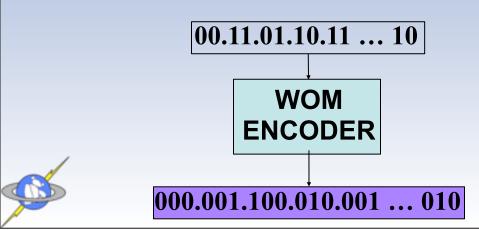

- We construct WOM-codes from any linear code:

21 2 CMRR

#### nory WOM-Codes with two writes

- Assume there are *n* cells and two writes, *t* = 2

- First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)

$C = \{ (R_1, R_2) \mid \$p \in [0, 0.5], R_1 \le h(p), R_2 \le 1 - p \}$

The WOM-rate  $R = R_1 + R_2 \le \log_2(3) \gg 1.58$ , achieved for p = 1/3

- Rivest and Shamir constructed WOM-codes of rates (2/3, 2/3) and (0.67, 0.67), *R* =1.34

- We construct WOM-codes from any linear code:

- The [23,12,7] Golay code: (0.9458, 0.5217) *R* = 1.4632

#### WOM-Codes with two writes

- Assume there are *n* cells and two writes, *t* = 2

- First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)

$C = \{ (R_1, R_2) \mid \$p \in [0, 0.5], R_1 \le h(p), R_2 \le 1 - p \}$

The WOM-rate  $R = R_1 + R_2 \le \log_2(3) \gg 1.58$ , achieved for p = 1/3

- Rivest and Shamir constructed WOM-codes of rates (2/3, 2/3) and (0.67, 0.67), R =1.34

- We construct WOM-codes from any linear code:

- The [23,12,7] Golay code: (0.9458, 0.5217) *R* = 1.4632

- The [16,11,4] extended Hamming code (0.769, 0.6875), *R* = 1.456 and for the same rate we get (0.6875, 0.6875), *R* = 1.375

#### WOM-Codes with two writes

- Assume there are *n* cells and two writes, *t* = 2

- First write:  $k_1$  bits,  $R_1 = k_1/n$ , second write:  $k_2$  bits,  $R_2 = k_2/n$

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)

$C = \{ (R_1, R_2) \mid \$p \in [0, 0.5], R_1 \leq h(p), R_2 \leq 1 - p \}$

The WOM-rate  $R = R_1 + R_2 \le \log_2(3) \gg 1.58$ , achieved for p = 1/3

- Rivest and Shamir constructed WOM-codes of rates (2/3, 2/3) and (0.67, 0.67), R =1.34

- We construct WOM-codes from any linear code:

- The [23,12,7] Golay code: (0.9458, 0.5217) *R* = 1.4632

- The [16,11,4] extended Hamming code (0.769, 0.6875), *R* = 1.456 and for the same rate we get (0.6875, 0.6875), *R* = 1.375

- By computer search we found rate (0.7273, 0.7273), *R* = 1.4546

#### Single Bit Representation in MLC Flash

#### Single Bit Representation in MLC Flash

#### New ECC Scheme for MLC Flash

- Single Bit Representation in MLC Flash

- New ECC Scheme for MLC Flash

- WOM-Codes

- Single Bit Representation in MLC Flash

- New ECC Scheme for MLC Flash

- WOM-Codes

- More analysis of codes and error behavior -COME TO BOOTH #510!