### New Strategies to Overcome 3bpc Challenges

#### **Controller's Perspective**

#### Hanan Weingarten, DensBits Technologies

- Smaller feature sizes and more bits/cell raise new Problems:

- Far worse statistics

- Variations over space and time

- At target cycle counts we obtain BERs of 10<sup>-1</sup>

- Consumer products require power efficient and low gate-count controllers

- Larger Blocks

- Slower programming times

- Solution requires a new approach:

- DSP is required to track device statistics and adapt read/write operation

- Near optimal power\footprint efficient and adaptive ECC

- New memory management algorithms

# ory Executive Summary (3)

- Value:

- 3bpc with 2bpc reliability:

- few hundreds -> 10K cycles

- 2bpc with 1bpc reliability:

- few thousands -> 100K cycles

- Recover what was previously unrecoverable (BER  $= 10^{-1}$ )

- Meet stringent Power/Performance requirements

- Brief overview of 3bpc devices

- Reliability challenges of 3bpc devices

- Memory Management

- Controller example

- Summary

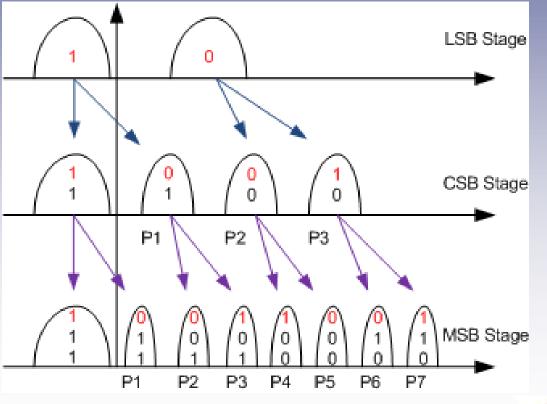

- 8 Levels per cell

- Each cell contains 3 bits from 3 different pages

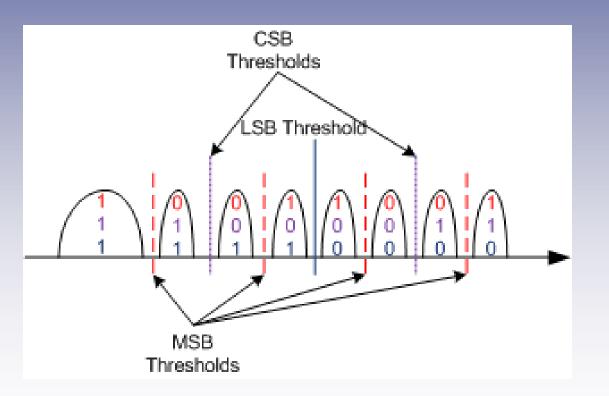

Read threshold combinations

## nory Overview of 3bpc Devices (3)

- Advance interface with Flash device allows controller to modify:

- Program lobe positions

- Read threshold positions

- Other parameters

. . .

- Allowing controller to control programming speed/accuracy

- Even/Odd pages parameters

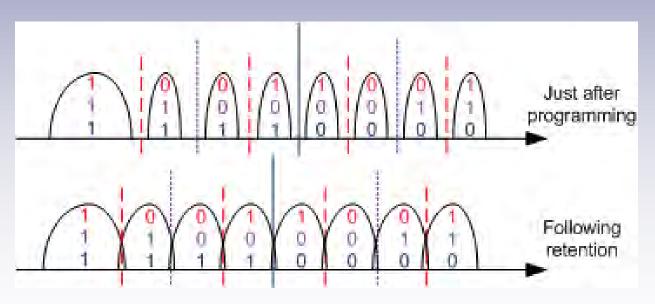

- Following Retention

- Lobes shift

- Lobes become wider

- Dependence on cycle count

- Implications:

- Using the same set of thresholds before and after retention is a bad idea

- The expected error count after retention is expected to be much worse than in 2bpc and SLC devices

# Reliability Challenges - Retention (3)

#### Solution: DSP+ECC

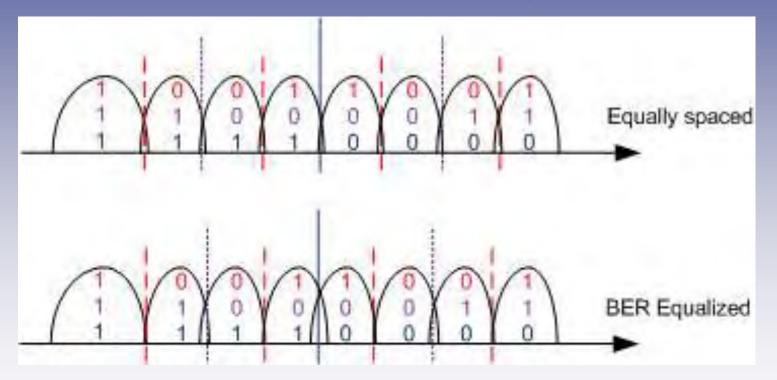

- Adaptive read threshold positioning

- Adaptive programming

- Blind read threshold positioning

- Efficient threshold tracking

- Manage history of thresholds

- Obtaining soft information

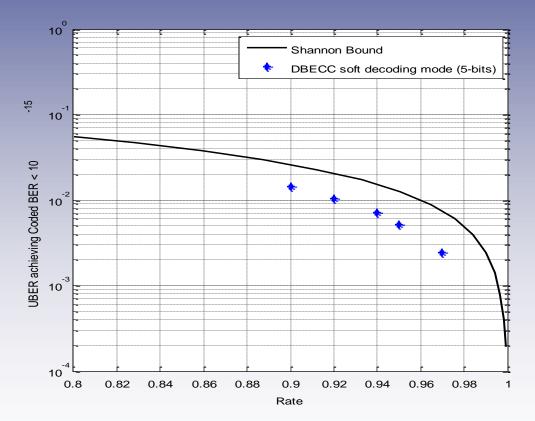

- Powerful ECC capable of performing both hard and soft decoding

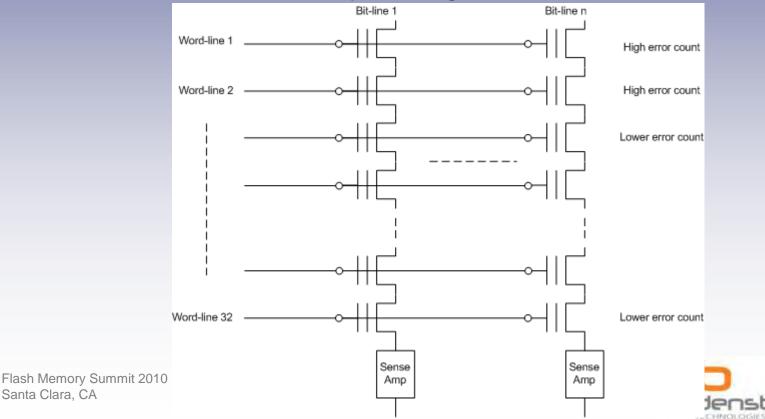

- Different regions within a Flash device exhibit different reliability

- Error counts may change across word-lines

• Number of errors depends on page type

Flash Memory Summit 2010 Santa Clara, CA

- Solutions for handling variations:

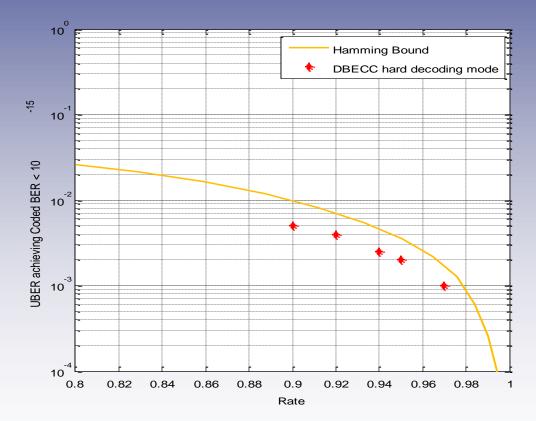

- Powerful and lean Encoder / Decoder capable of variable coding rates

- Encoding such as to average errors across different areas

- Equalize BER

- Optimize robustness variable code

- Advanced memory management

Hard Decoding

## emory Example: DensBits' Coding System

Soft Decoding

# Memory Management Challenges (1)

- Large blocks and longer programming times

- Long block copy times

- Standard consumer products use management techniques which fail time-out limitations

- Low IOP rates

- Solution

- Advance, yet efficient memory management, on a par with that seen in SSDs

- Accelerated and adaptive programming relying on advanced reliability solution

## 3bpc Controller: DensBits' DB3609

#### DB3609

- Supports 2 / 3bpc devices

- SD / eMMC interface

- Endurance + Retention with 3bpc devices: 10K cycles

- Class 4 / 6

www.densbits.com

- Cell Coupling

- Adaptive Programming

- Effective ware-leveling

- Managing variable rates

- Managing thresholds

- Power cycling in 3bpc

• ...

- Handling 3bpc devices with high reliability requires a fresh approach: Management + DSP + ECC

- Unique and advanced design is required to meet power and cost requirements

- Obtaining 2bpc reliability and performance is possible

# Thank You

Flash Memory Summit 2010 Santa Clara, CA