### Will Phase Change Memory (PCM) Replace DRAM or NAND Flash?

Dr. Mostafa Abdulla High-Speed Engineering Sr. Manager, Micron

Marc Greenberg Product Marketing Director, Cadence

August 19, 2010 Flash Memory Summit

- "New memory" motivation (recognized ~1999)

- Current NVM (and DRAM) are becoming electrostatics limited

- MOS transistor-based cell

- Charge storage memory effect

- Starting to encounter physical scaling limitations

- Limitations manifesting first as degradation in reliability (endurance/retention)

### Realization

- Next-generation NVM will exploit new storage physics

- Significant innovation will take time (history says ~10-year "gestation")

#### Response

- PCM identified as the best candidate

- Research efforts validated the assumptions and initiated development

- PCM moving into production today

- We believe features of PCM will enable new usage models

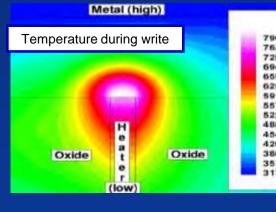

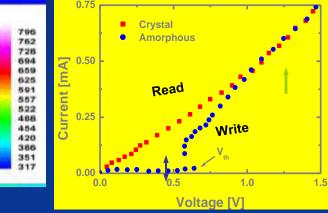

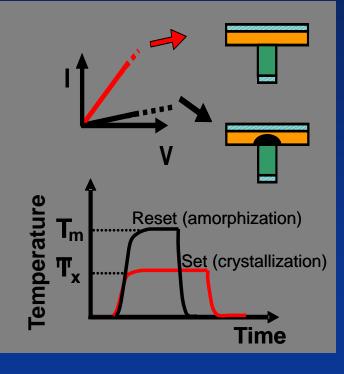

## **PCM Mechanisms**

- Storage

- GST: germanium-antimony-tellurium chalcogenide glass

- Cell states varying from amorphous (high resistance) to crystalline (low resistance) states

- Read operation

- Measure resistance of the GST

- Write operation

- Heat GST via current flow (Joule effect)

- Time at critical temperature determines cell state

#### Crystalline

#### Amorphous

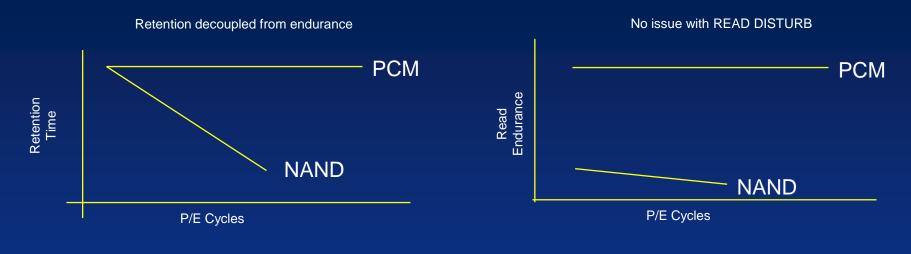

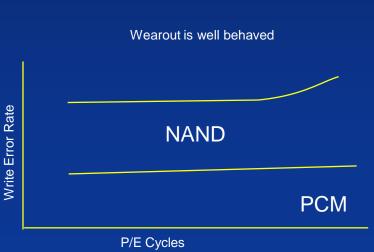

### Summary of Key PCM Reliability Metrics

#### Result:

- Management greatly simplified; no software overhead for some apps

- Post-stress shelf life problem solved

- Endurance can be increased significantly through management of bit errors; data is stable when successfully written

# **PCM Key Attributes**

| Attribute          | РСМ              | EEPROM                           | NOR             | NAND                     | DRAM         |

|--------------------|------------------|----------------------------------|-----------------|--------------------------|--------------|

| Nonvolatile        | Yes              | Yes                              | Yes             | Yes                      | No           |

| Granularity        | Small/Byte       | Small/Byte                       | Large           | Large                    | Small/Byte   |

| Erase              | No               | No                               | Yes             | Yes                      | No           |

| Software           | Easy             | Easy                             | Moderate        | Hard                     | Easy         |

| Power              | ~Flash           | ~Flash                           | ~Flash          | ~Flash                   | High         |

| Write<br>Bandwidth | 1–15+<br>MB/s    | 13–30<br>KB/s                    | 0.5–2<br>MB/s   | 10+<br>MB/s              | 100+<br>MB/s |

| Read Latency       | 50–100ns         | 200–200ns                        | 70–100ns        | 15–50µs                  | 20–80ns      |

| Endurance          | 10 <sup>6+</sup> | 10 <sup>5</sup> –10 <sup>6</sup> | 10 <sup>5</sup> | <b>10</b> <sup>4-5</sup> | Unlimited    |

PCM provides an new set of features combining components of NVM with DRAM

# **PCM Application Opportunities**

#### Wireless systems

- Direct code execution, semi-static data and file storage

- > Bit alterability allows direct-write memory

### Solid state storage subsystems

- Frequently accessed pages and elements easily managed when manipulated in place

- > Caching with PCM will improve performance and reliability

### Computing platforms

- Taking advantage of nonvolatility to reduce the power

- PCM offers endurance and write latency that are compelling for a number of novel solutions

## Wireless Systems: LPDDR2-PCM Architecture Evolution

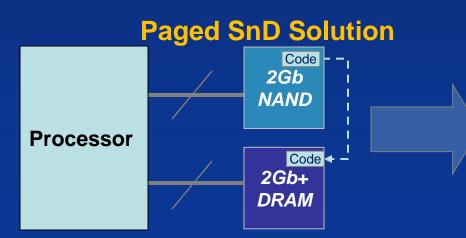

#### **Paged SnD Solution**

- Code stored in NVM

- Code shadowed or paged to DRAM to execute

- Reliability is a significant concern

- Significant performance variability

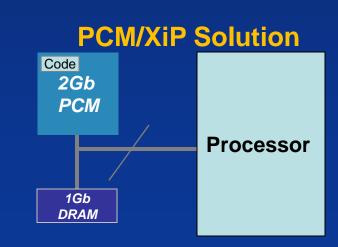

#### **PCM/XiP Solution**

- Code stored in PCM

- Code executed from PCM

- No reliability concerns for code

- Limited or no performance variability

## System Benefits of LPDDR2-PCM

- LPDDR2-PCM system architecture saves DRAM and power

- Performance mostly equivalent to DRAM

- PCM system architecture simplifies software

- Endurance and data retention are fundamentally decoupled, improving TTM

- PCM opens new usage models

- Persistent-RAM model (NV + bit alterability) changes application operation

PCM file system performance close to spec (NAND/NOR lose performance due to erase)

#### PCM user improvements

- Instant on

- Boot time

- Application launch

- Application concurrency

- Power

- PCM reliability improvements

- PCM overcomes DRAM scaling and NAND reliability concerns

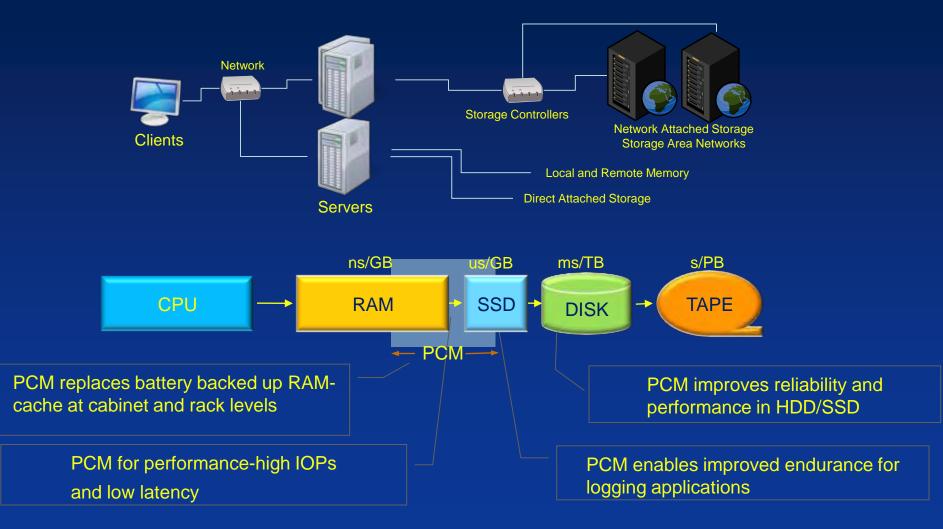

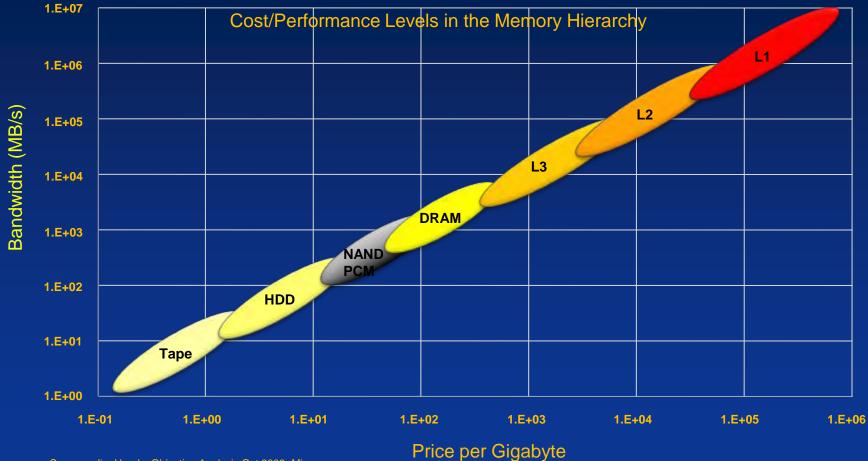

### Memory Hierarchy in Servers and Storage Where PCM Can Fit

### **Memory Hierarchy**

Sources: Jim Handy, Objective Analysis Oct 2009, Micron

- Phase change memory (PCM) technology is demonstrating the capability to enter the broad memory market and to become a mainstream memory

- PCM provides a new set of features for novel applications, combining components of NVM and DRAM, while at the same time being a sustaining and a disruptive technology

- Our prediction is that with PCM achieving technology maturity, having a scaling perspective, and having a broad application range, it will play a key role in the memory market for the next decade