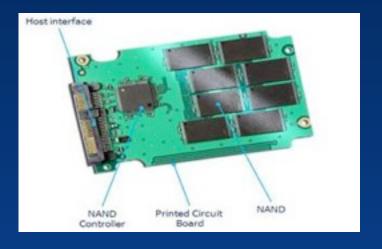

#### 400 MT/s NAND Interface Solutions

Terry Grunzke

Micron Technology

# Why 400 MT/s interface speeds?

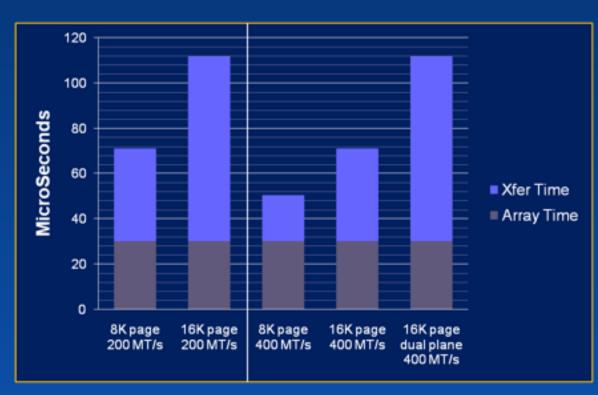

- NAND architectures are moving towards larger data transfer sizes

- Increased Bandwidth

- High performance computing applications

- High density SSDs

- USB 3.0

- Reduced latency

### 400 MT/s NAND interface solutions

- ONFI 3.0 NV-DDR2

- Released March 2011

- ONFI 3.0 Webinar: <a href="https://www.micron.com/ONFI-3">www.micron.com/ONFI-3</a>

- Toggle Mode 2.0

- Announced July 2010

- Work occurring in JEDEC on 400 MT/s

- Reduced CIO

- Removes features to reduce loading

- 400 MT/s DDR interface

- Compatible with ONFI 3.0 NV-DDR2

- Differential signaling (RE and DQS)

- On Die Termination

- External VrefQ

- Reduced signaling (SSTL\_18)

- Warm up cycles

- 400 MT/s DDR interface

- Superset of Toggle Mode 2.0

- Differential signaling (RE and DQS)

- On Die Termination

- External VrefQ

- Reduced signaling (SSTL\_18)

- Warm up cycles

- Matrix On Die Termination

- Volume Addressing

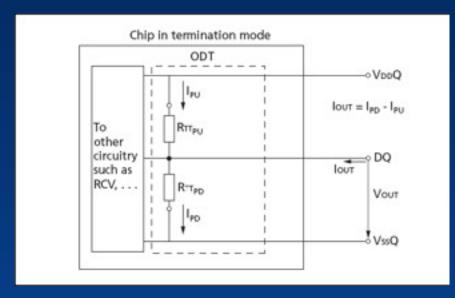

### Benefits of termination

#### Power costs of termination

To achieve Rtt of 50 ohms:

RttPU = 100 ohms RttPD = 100 ohms

With 1.8V VccQ each DQ draws ~9mA

For all terminated signals this amounts to ~160mW per channel to achieve 50ohm termination with linear termination

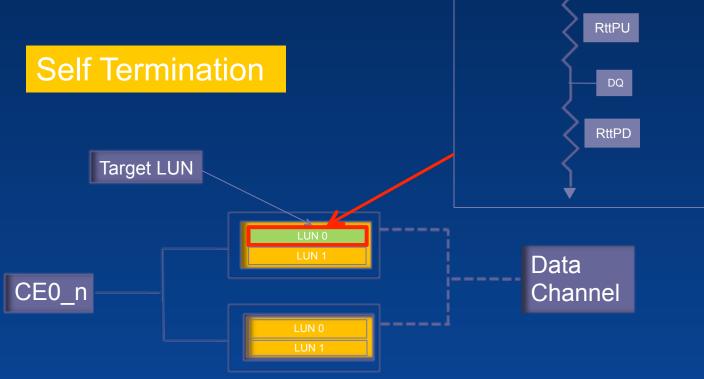

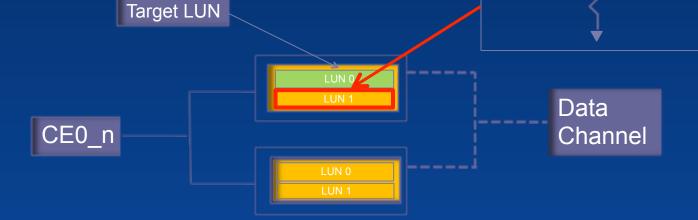

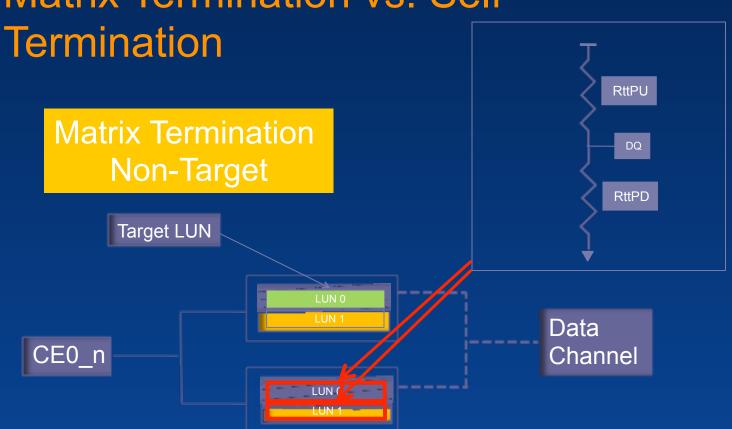

Matrix Termination vs. Self

Termination

- Target only termination available

- If supported for Reads cannot use output drivers for termination

Matrix Termination vs. Self

Termination

Matrix Termination Target

- Target or Non-target termination capable

- Supported for Reads and Writes

Santa Clara, CA August 2011 **RttPU**

**RttPD**

Matrix Termination vs. Self

Multiple LUNs can be terminators providing a flexible array of termination values and locations

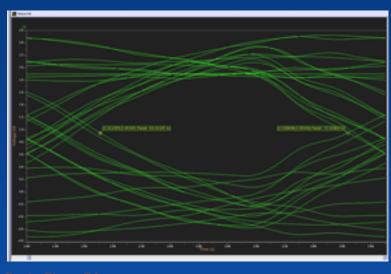

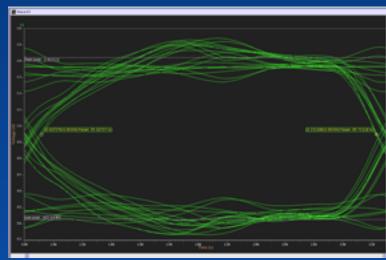

# ory Timing Budget considerations

With heavy loading and long trace lengths slew rates can become very slow.

.0 400 MT/s timing budget 1V/nS input **QN**ম Pale400 MT/s timing budget 0.3V/nS input slew rate

Controller

Channel

NAND

Controller

Channel

NAND

TM 2.0 400 MT/s timing budget 0.3V/nS input slew rate

Controller

Channel

NAND

# Topology considerations