### High Density, High Reliability Carbon Nanotube NRAM

Thomas Rueckes

CTO

Nantero

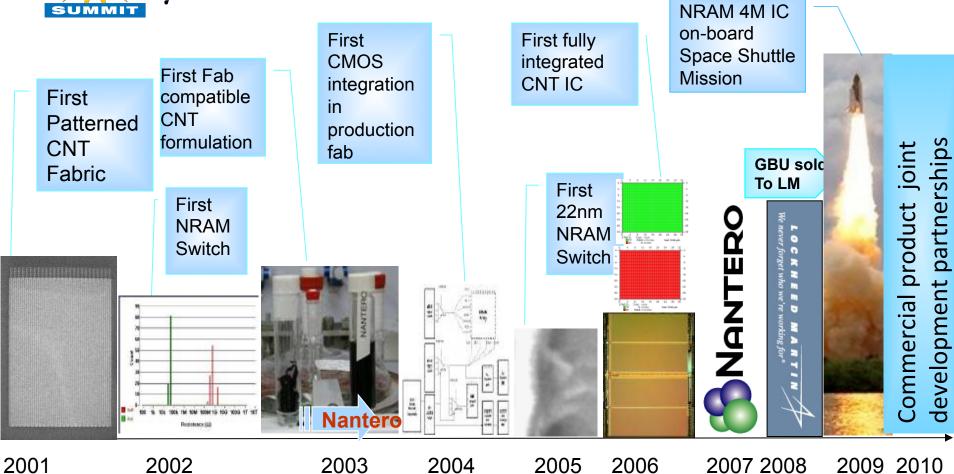

#### **Nantero Overview**

- Founded in 2001 to develop nonvolatile memory using carbon nanotubes (CNT) for high density standalone and embedded applications

- CNT engineering in Boston

- Circuit design, product, test, device & integration engineering in Sunnyvale

- Government Business sold to Lockheed Martin in 2008 & successful NRAM test on space shuttle mission

- Commercial development partnerships with IDMs & fabless companies for embedded and standalone memory applications in progress

- Technology development & IP licensing business model

- >133 US patents awarded, >205 US applications pending, plus more worldwide

- WSJ patent score card:

- The only semiconductor start-up ranked (2009)

- #2 ranked for scientific strength of IP (2010)

- IEEE Spectrum; Semiconductor Manufacturing Category

- #5 worldwide (2009)

- #2 worldwide and #1 in US (2010)

### **Nantero Timeline**

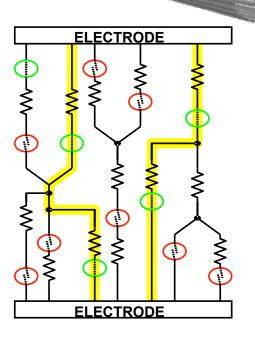

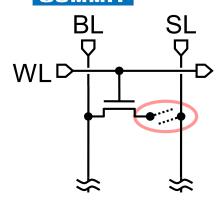

### NRAM: RRAM with CNT Resistance Change Material

ON ('1')

-RESET (ON → OFF): CNT-to-CNT are not in physical contact = high resistance

-SET (OFF → ON): CNT are in physical contact = low resistance

SET is an electrostatic operation while RESET is phonon driven operation (phonon heating of CNT contacts)

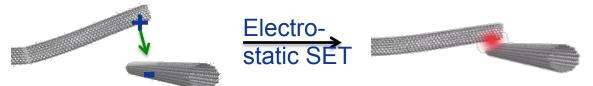

#### NRAM Mechanism

- SET: electrostatic operation

- Write voltage → electrostatic CNT-CNT attraction → CNT junction closure (ON)

CNTs remain in ON state due to physical adhesion (Eact ~ 5eV)

- RESET: phonon driven operation

- Voltage applied → CNT phonon excitation → CNT separation (OFF)

CNTs remain in OFF state due to high mechanical (1TPa) stiffness (Eact>>5eV)

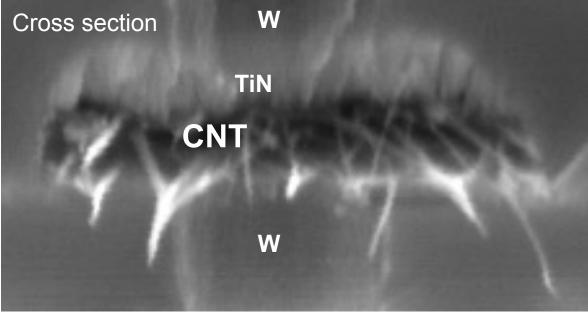

### **CNT Process Integration**

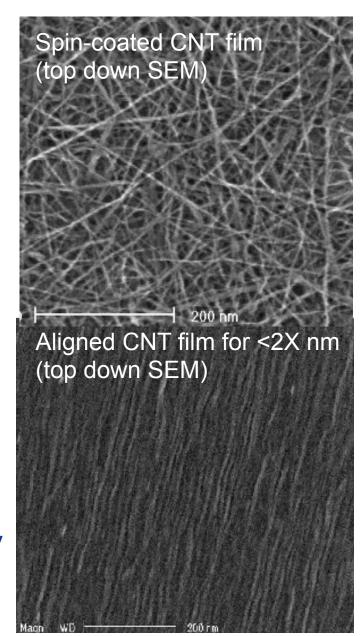

- -CNT Spin-on foundry capability at SVTC on 300mm & 200mm coat tracks

- -Tracemetals meets typical BEOL contamination specs (TXRF: <1E11/cm2)

- -CNT wafers being processed using 248nm, 193nm dry & *immersion* lithography

- -CNT Integration temperatures at standard 425C BEOL and higher if W interconnect only

- Conventional tooling for CNT RIE dry etch and post etch cleaning

- -CNT density controllable for different technology nodes

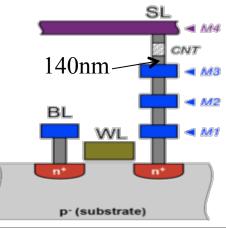

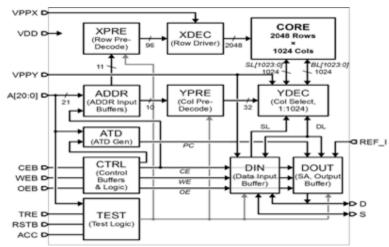

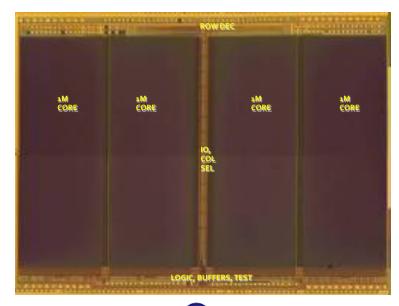

#### 4Mb 140nm Carbon Nanotube NRAM

| 140nm 4Mb sample          | Write: SET & RESET<br>(-65C to +165C operation)                |

|---------------------------|----------------------------------------------------------------|

| Voltage (CNT)             | ~ 3.5 V (scales to 1V with window, CD & pulse speed)           |

| Write & read time         | < 20 ns<br>(CMOS limited)                                      |

| Current                   | I (power supply)=1uA/bit                                       |

| Energy                    | 0.01 fJ / nm2                                                  |

| Window (adjustable)       | 100 kohm(ON)/100 Mohm(OFF)                                     |

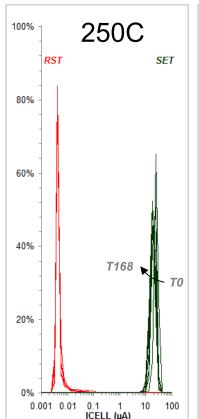

| Endurance<br>Read disturb | >1E9 cycles (unlimited expected) >1e15 reads (non-destructive) |

| Retention                 | >10 years at 300C (Eact~5eV)                                   |

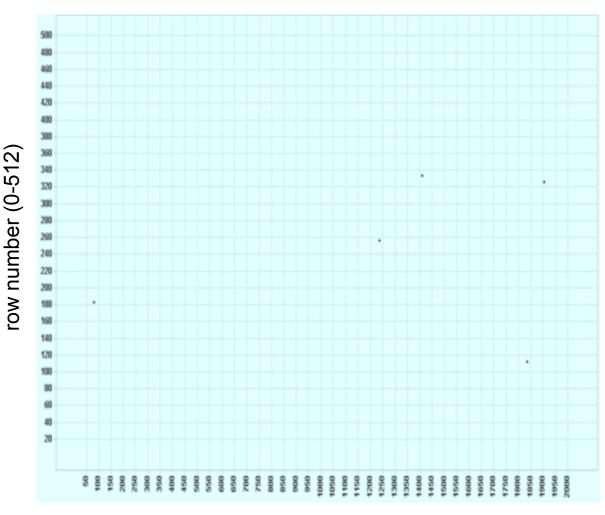

#### NRAM Devices at 99.997% Yield

- -93% of the word lines at 100% bit yield (complete 1Mb bank; 512WLs, 2kb each)

- only ~30 bits in 1Mb bank failing (all in 1st cycle)

- No bit fallouts during cycling

- Total bit yield is 99.997%

- Redundancy adequate to repair the device

Column number (0-2048)

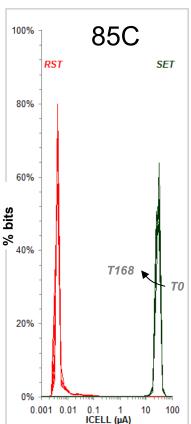

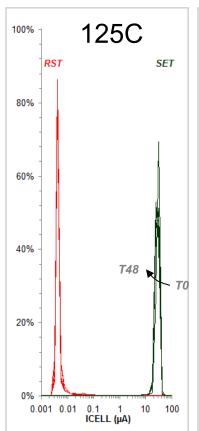

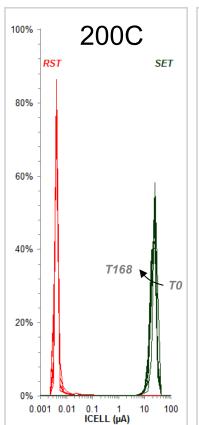

#### NRAM Data Retention: >10 Years @ 300C

T0= before bake T

T4= after 4 hour bake T

T48= after 48 hour bake T

T168=after 168 hour bake \*

T1= after 1 hour bake T24= after 24 hour bake T96= after 96 hour bake Data retention: >10years at 300C (3σ) Activation energy: 5.4eV(median), 4.5eV(3σ)

32kbit / die for each temp

Icell (in  $\mu$ A) at 1volt

### NRAM Endurance: >1E9 Cycles

### **NRAM Technology Summary**

- 140nm 4Mb CNT NRAM samples available

- RAM-like <20ns write & read (non-destructive)</li>

- Unlimited endurance expected (1E9 cycles demonstrated)

- Highest reliability of any NVM: >10 years @ 300C (Eact ~5 eV)

- Minimum size select device for 1T1R cell (scalable to 1V/<10uA)</li>

- Low process cost: no HV transistors; 1 BEOL mask for NRAM

- Scalable technology: <5nm CNT-CNT switch; MLC possible</li>

- 300mm and 200mm CNT spin-on foundry capability available

- Transferrable NRAM POR process using only standard BEOL materials (no exotic metals) worked out

### **NRAM Memory Applications**

- NRAM for post-NAND

- Scalability to <5nm</li>

- Low write current

- Dense 1T1R& 1D1Rcells

- MLC capable

- NRAM for post-DRAM

- Scalability to

<5nm</li>

- High endurance

- Fast write time

- Low write current

- NRAM for embedded

NVM

- Low cost

- Highest reliability

- Competitive macro size

- Scalability