### REVELUTION The Impact of Emerging Memory

Thursday, August 23, 12

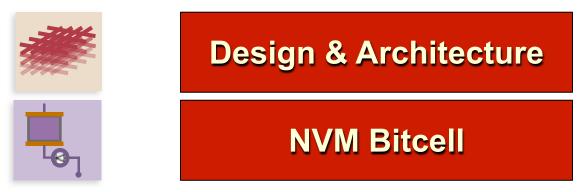

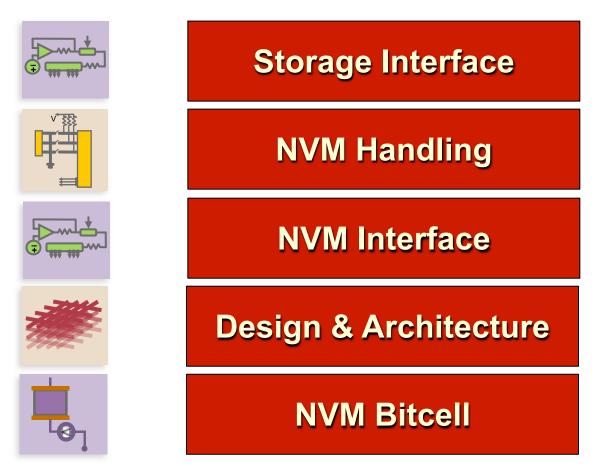

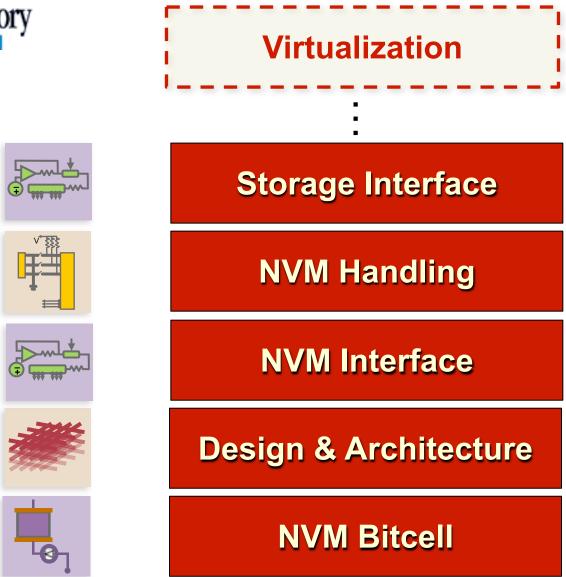

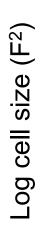

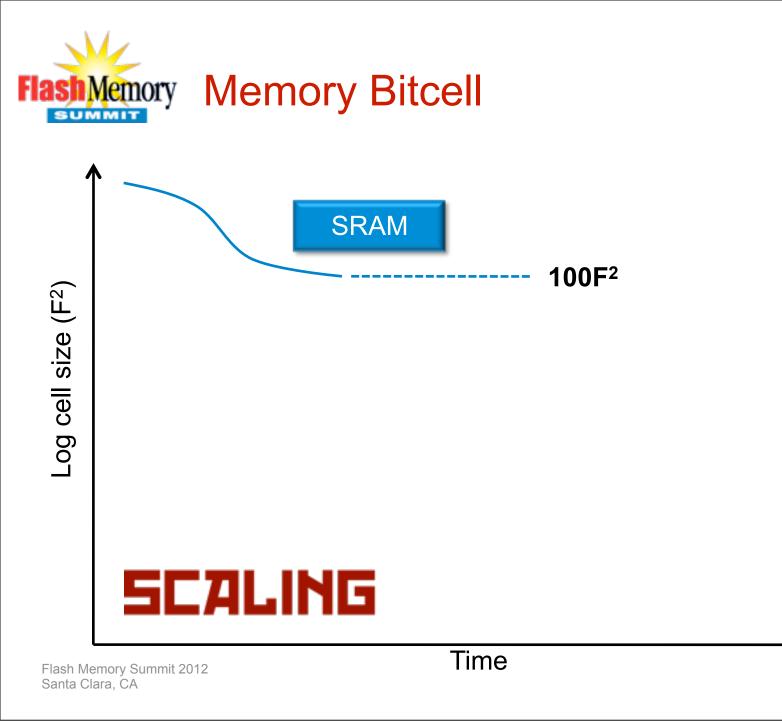

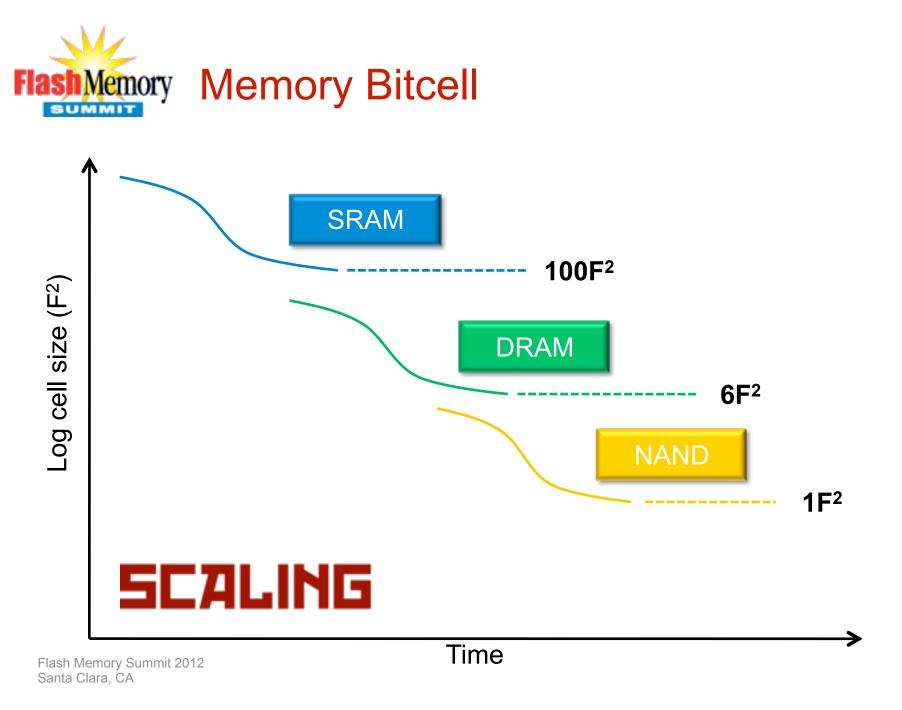

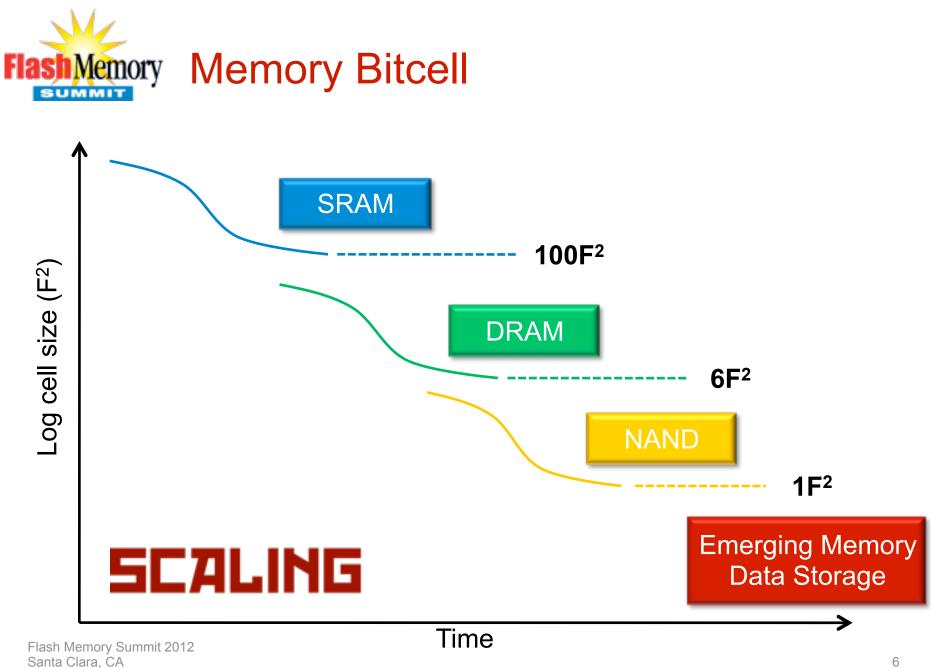

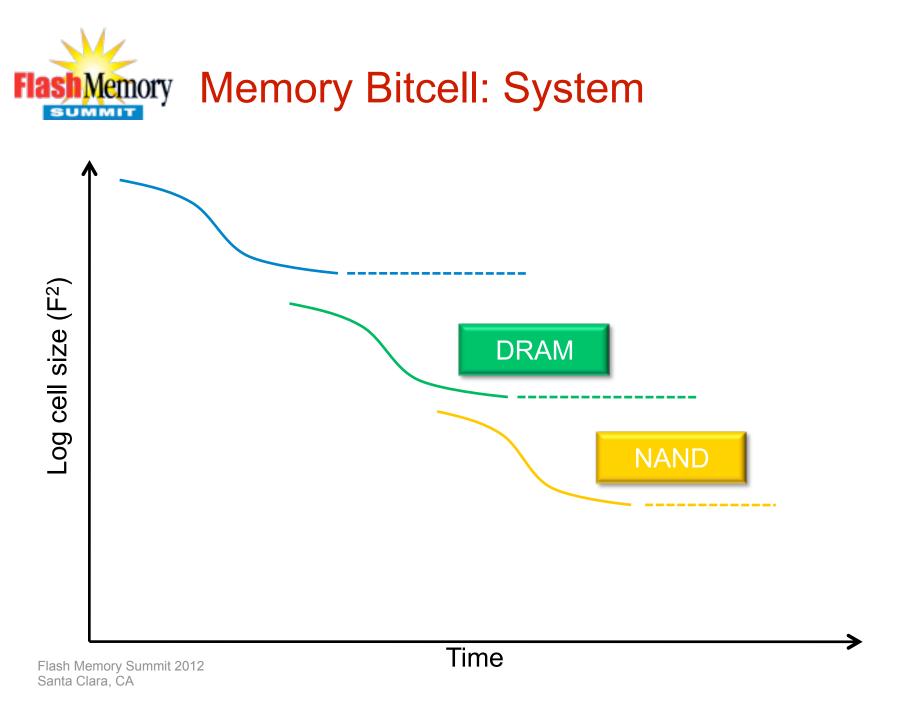

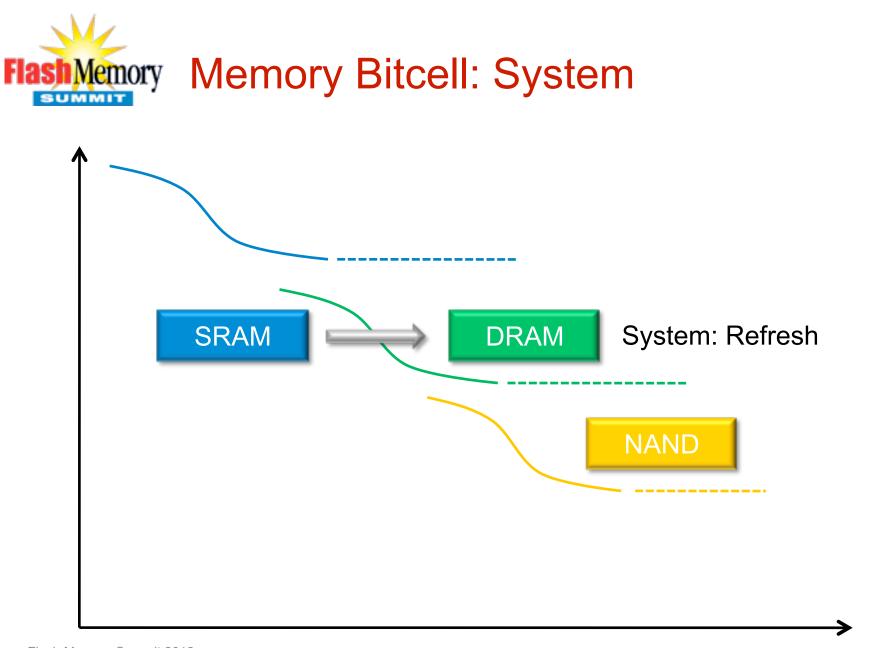

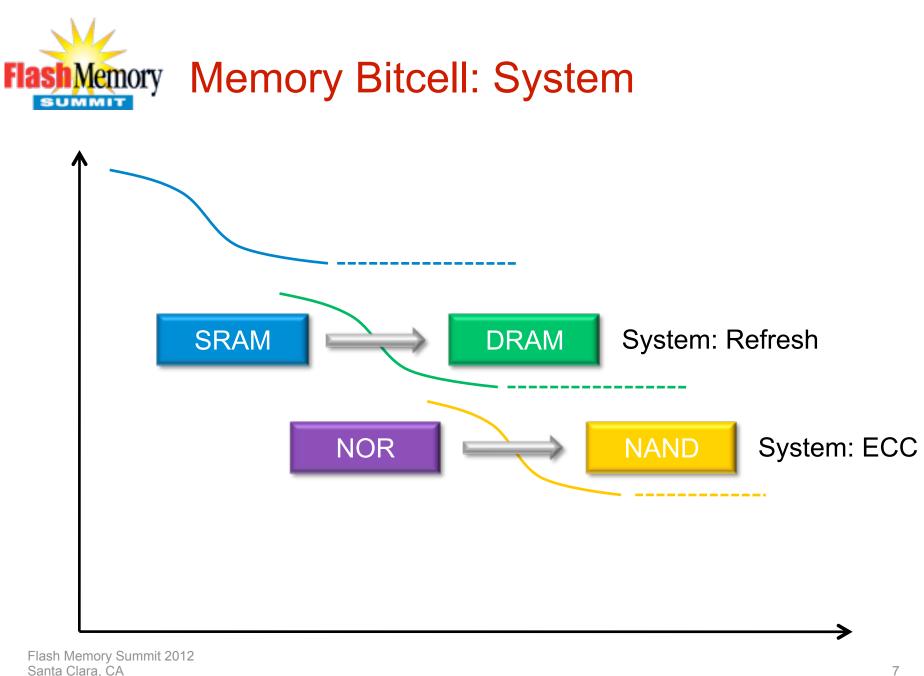

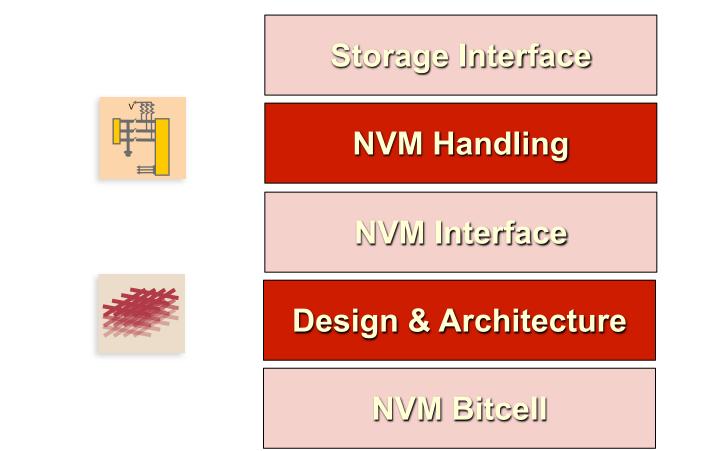

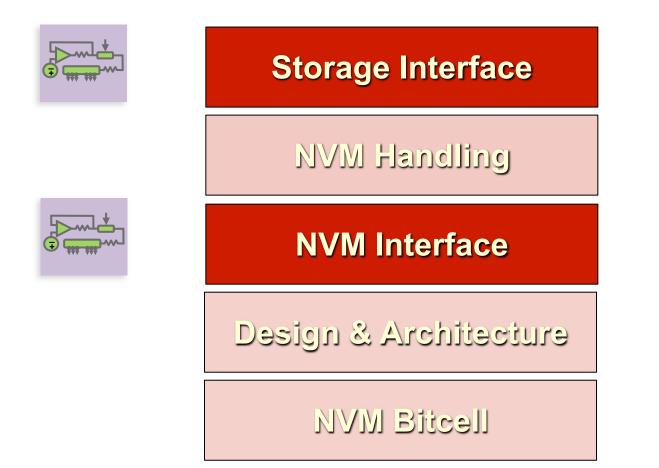

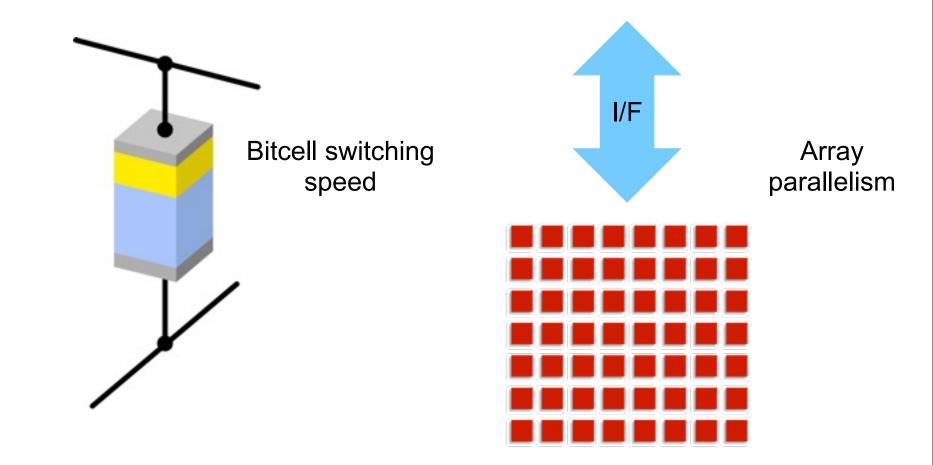

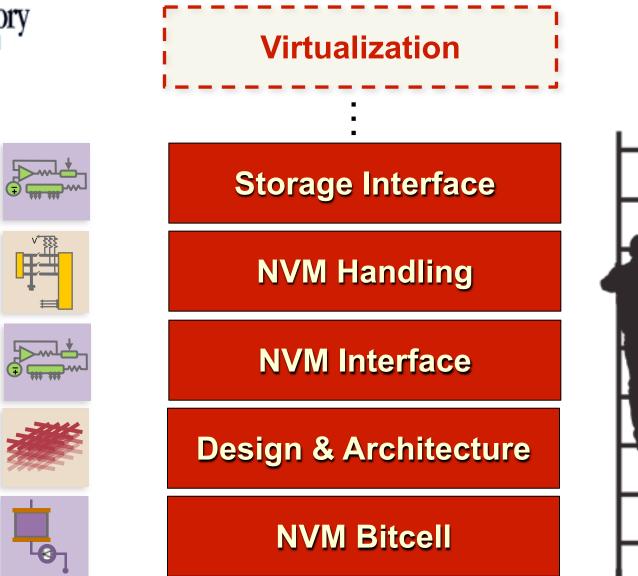

**NVM Bitcell**

Storage Interface

NVM Handling

**NVM Interface**

Design & Architecture

**NVM Bitcell**

Time

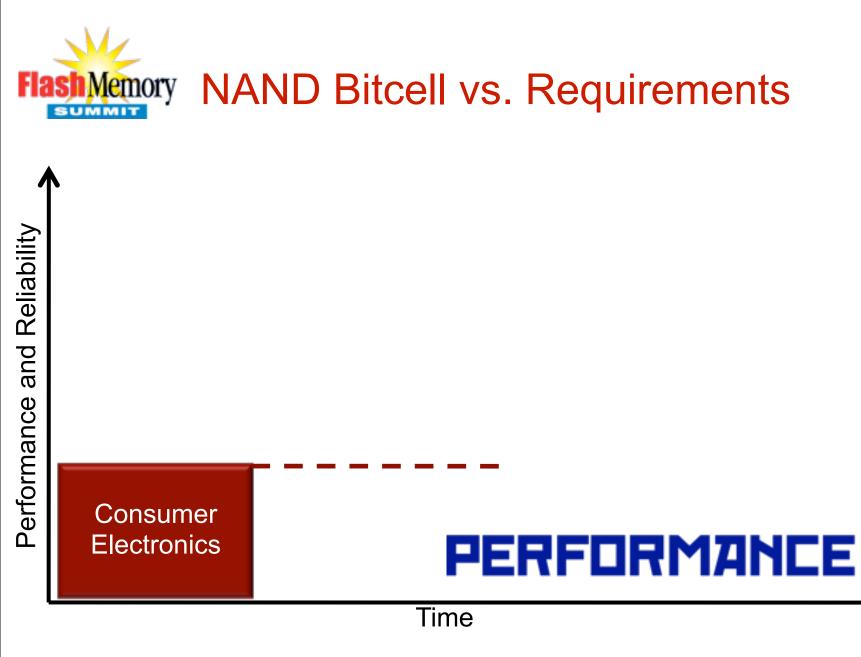

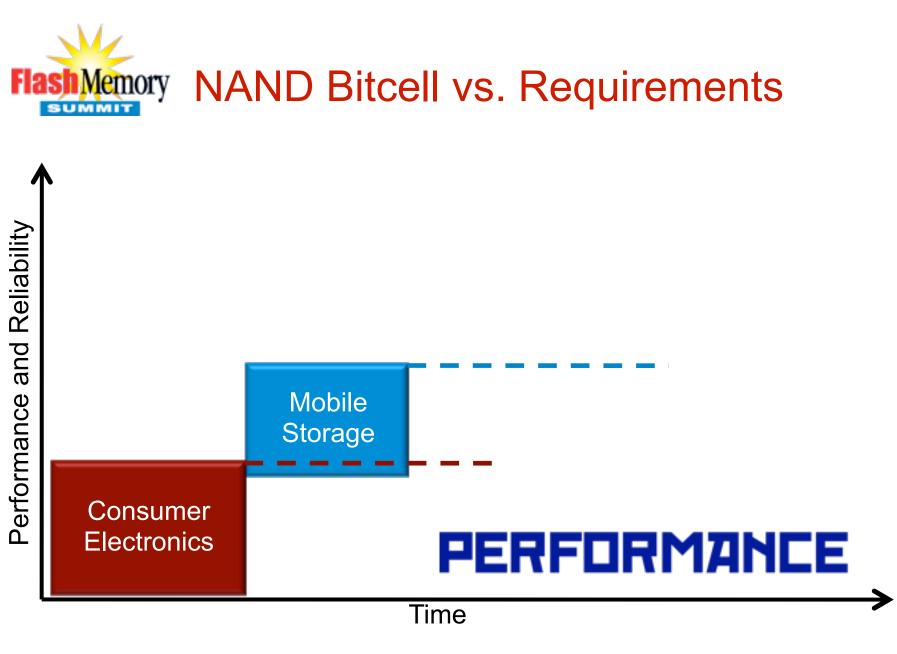

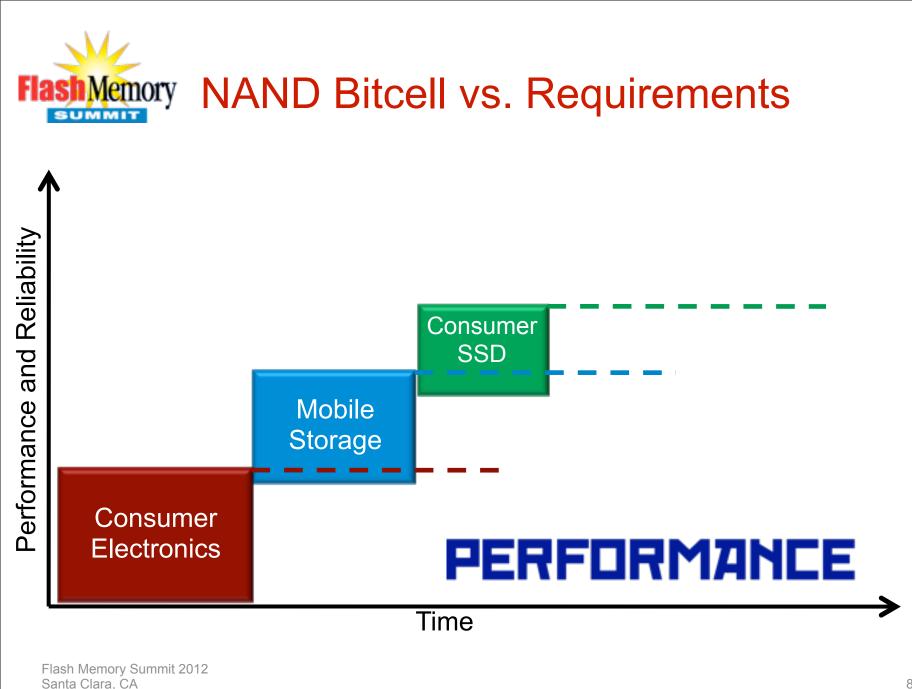

### PERFORMANCE

Time

Flash Memory Summit 2012 Santa Clara, CA

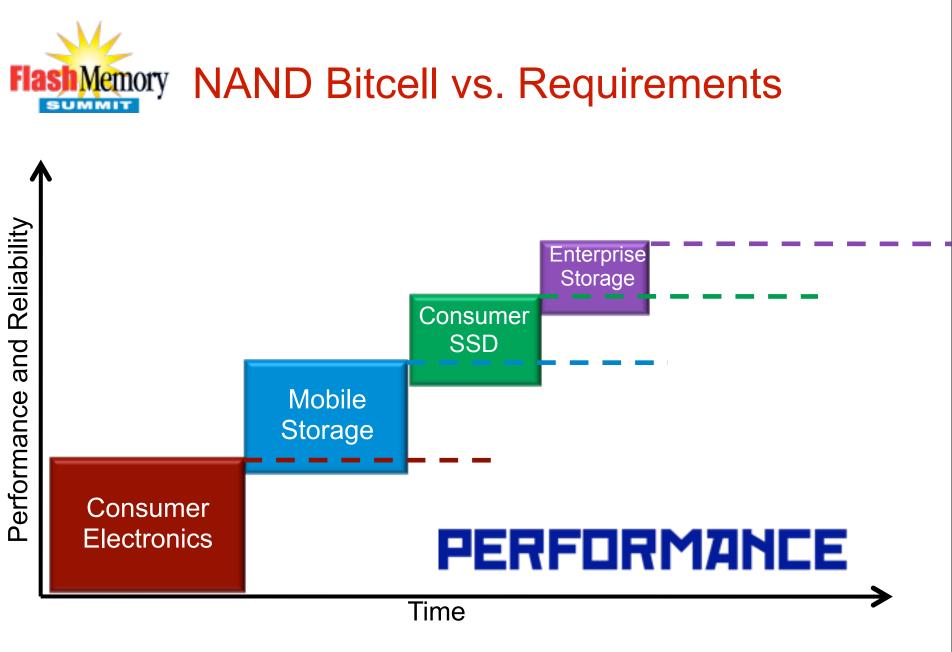

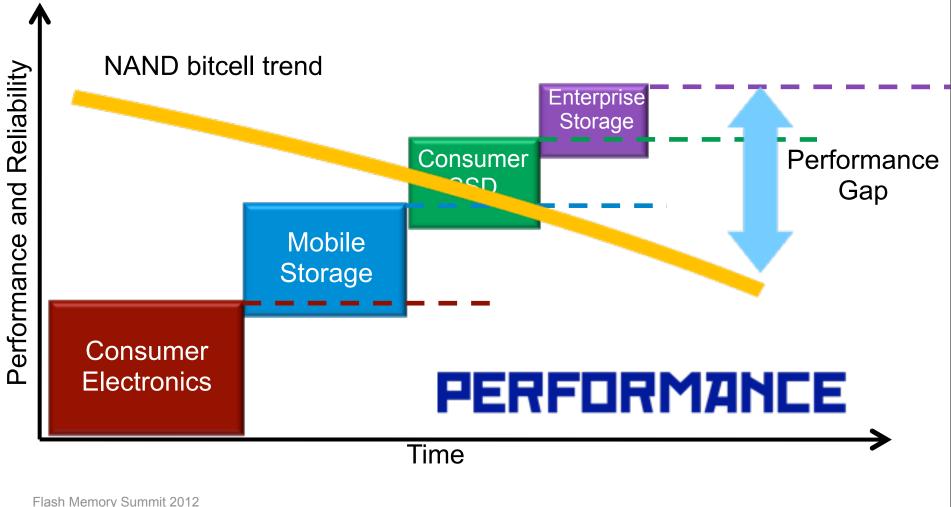

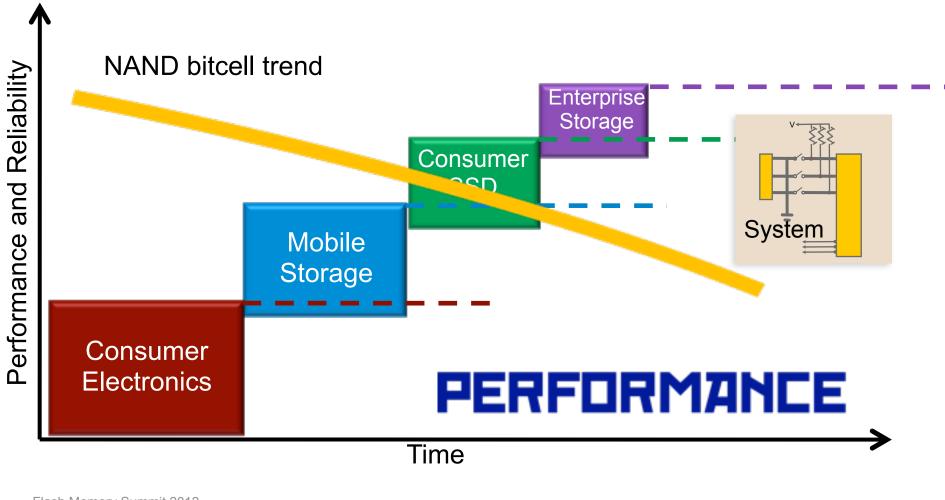

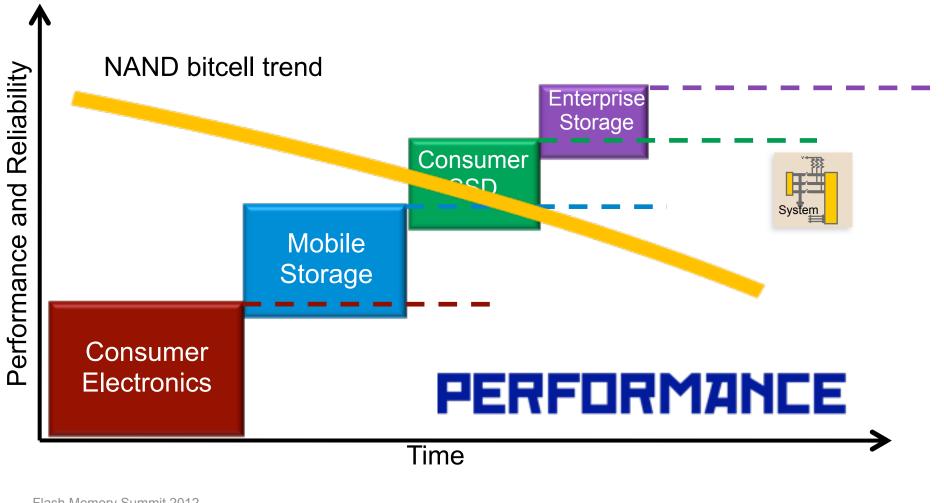

#### Flash Memory NAND Bitcell vs. Requirements

8

Santa Clara, CA

#### Flash Memory NAND Bitcell vs. Requirements

8

#### Flash Memory NAND Bitcell vs. Requirements

8

#### Flash Memory Key Criteria for Emerging Memory

#### Flash Memory Key Criteria for Emerging Memory

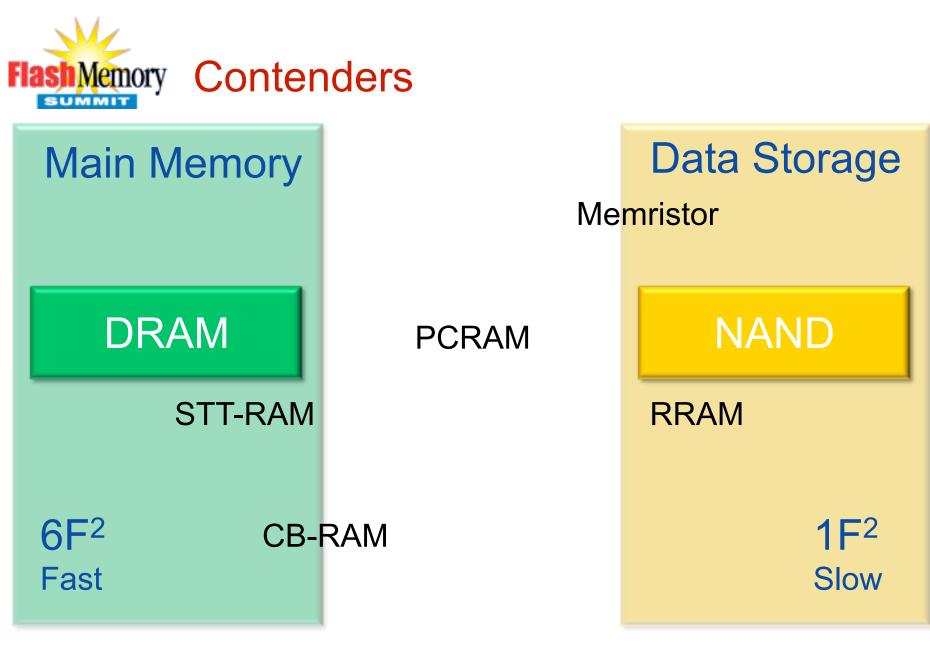

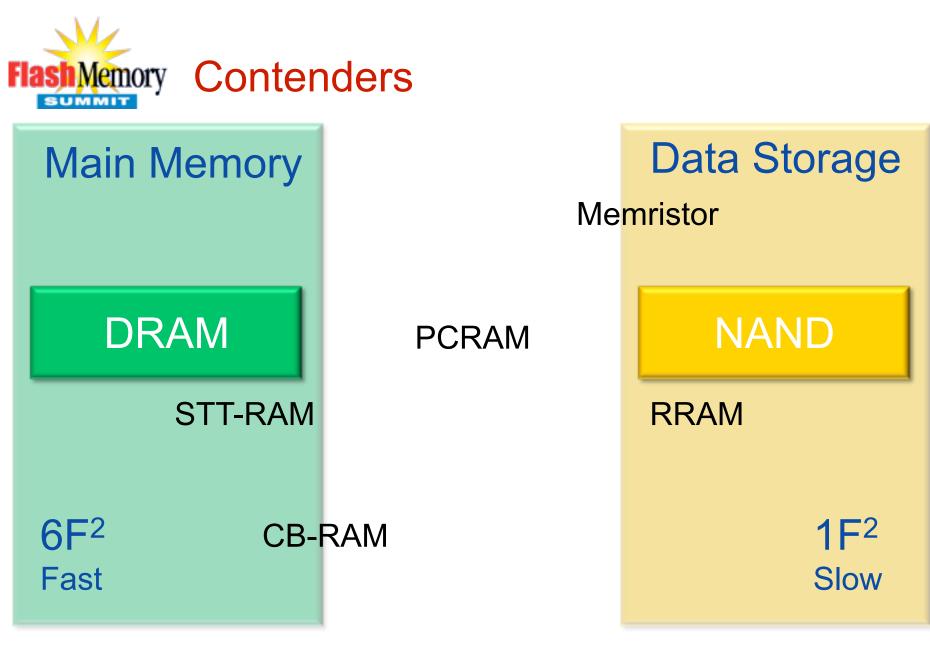

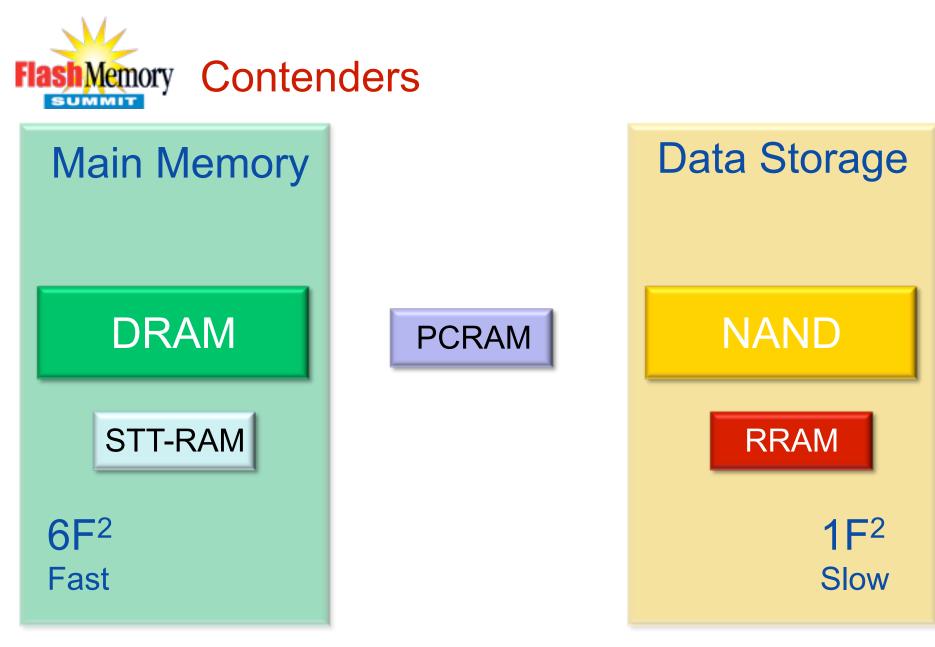

# SCALING

Flash Memory Summit 2012 Santa Clara, CA

#### Memory Key Criteria for Emerging Memory

# SCALING

## PERFORMANCE

|                                  | STT-RAM                  | PCRAM                    | RRAM                                 | NAND                      |

|----------------------------------|--------------------------|--------------------------|--------------------------------------|---------------------------|

| Memory Cell<br>(F <sup>2</sup> ) | $30F^2 \rightarrow 6F^2$ | $10F^2 \rightarrow 5F^2$ | $20F^2 \rightarrow 0.25F^2$          | $4.5F^2 \rightarrow 1F^2$ |

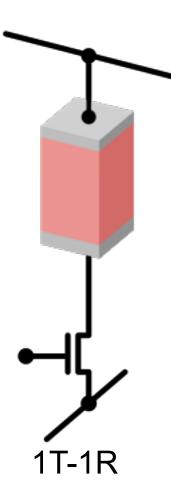

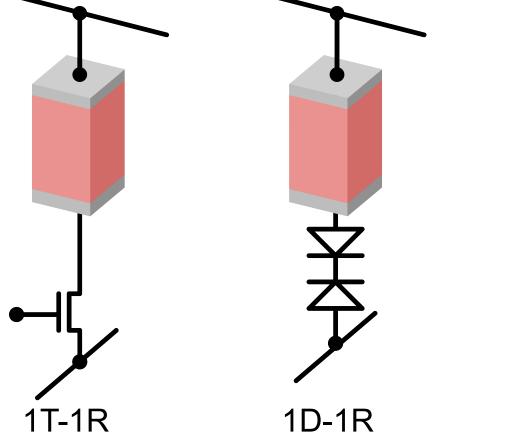

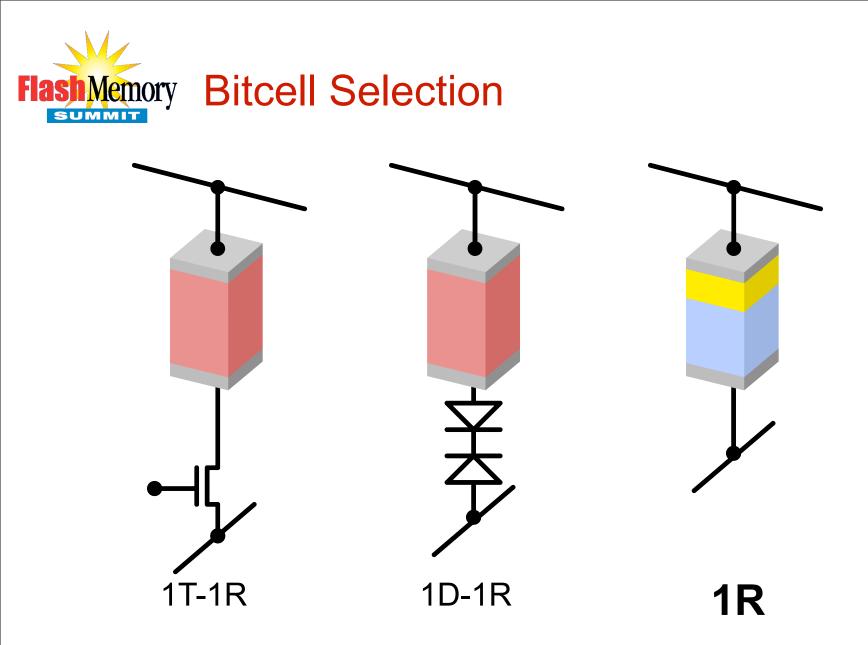

| Cell type                        | 1T-1R                    | 1T-1R<br>1D-1R           | 1T-1R<br>1D-1R<br><b>1R</b>          | 1T-FG                     |

| Write Speed<br>(Bit level)       | 1's ns                   | 10's ns                  | 10's ns<br>~ 100's ns                | 10,000 ns                 |

| Application                      | Embedded<br>Main memory  | Code storage<br>NV cache | Data storage<br>NV cache<br>Embedded | Data storage              |

|                                  | STT-RAM                  | PCRAM                    | RRAM                                 | NAND                      |

|----------------------------------|--------------------------|--------------------------|--------------------------------------|---------------------------|

| Memory Cell<br>(F <sup>2</sup> ) | $30F^2 \rightarrow 6F^2$ | $10F^2 \rightarrow 5F^2$ | $20F^2 \rightarrow 0.25F^2$          | $4.5F^2 \rightarrow 1F^2$ |

| Cell type                        | 1T-1R                    | 1T-1R<br>1D-1R           | 1T-1R<br>1D-1R<br><b>1R</b>          | 1T-FG                     |

| Write Speed<br>(Bit level)       | 1's ns                   | 10's ns                  | 10's ns<br>~ 100's ns                | 10,000 ns                 |

| Application                      | Embedded<br>Main memory  | Code storage<br>NV cache | Data storage<br>NV cache<br>Embedded | Data storage              |

|                                  | STT-RAM                  | PCRAM                    | RRAM                                 | NAND                      |

|----------------------------------|--------------------------|--------------------------|--------------------------------------|---------------------------|

| Memory Cell<br>(F <sup>2</sup> ) | $30F^2 \rightarrow 6F^2$ | $10F^2 \rightarrow 5F^2$ | $20F^2 \rightarrow 0.25F^2$          | $4.5F^2 \rightarrow 1F^2$ |

| Cell type                        | 1T-1R                    | 1T-1R<br>1D-1R           | 1T-1R<br>1D-1R<br><b>1R</b>          | 1T-FG                     |

| Write Speed<br>(Bit level)       | 1's ns                   | 10's ns                  | 10's ns<br>~ 100's ns                | 10,000 ns                 |

| Application                      | Embedded<br>Main memory  | Code storage<br>NV cache | Data storage<br>NV cache<br>Embedded | Data storage              |

1D-1R

**1R**

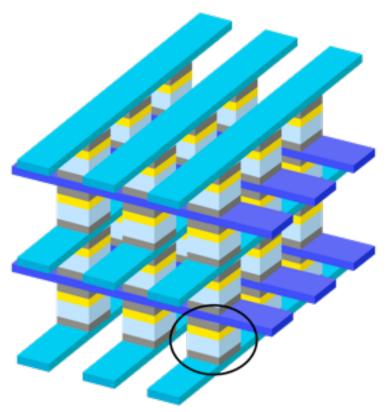

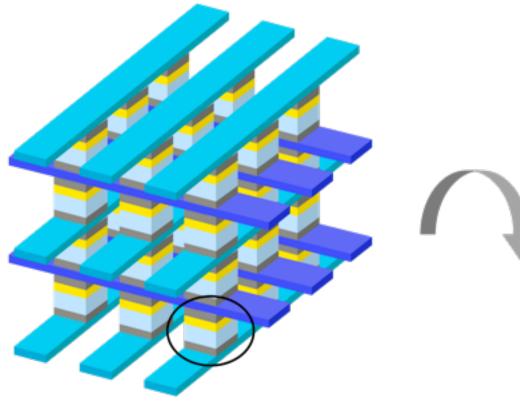

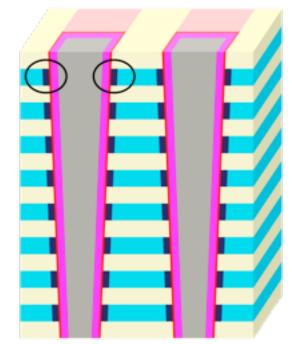

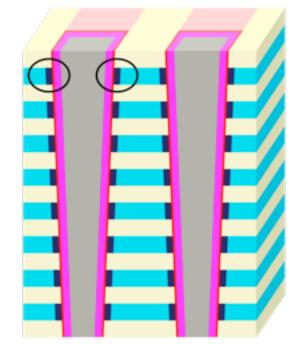

Stacked Planar

4F²/N 2 Masks per Layer

Stacked Vertical

4F²/N 2 Masks per Layer

2F²/N 2 Masks per 8 Layers

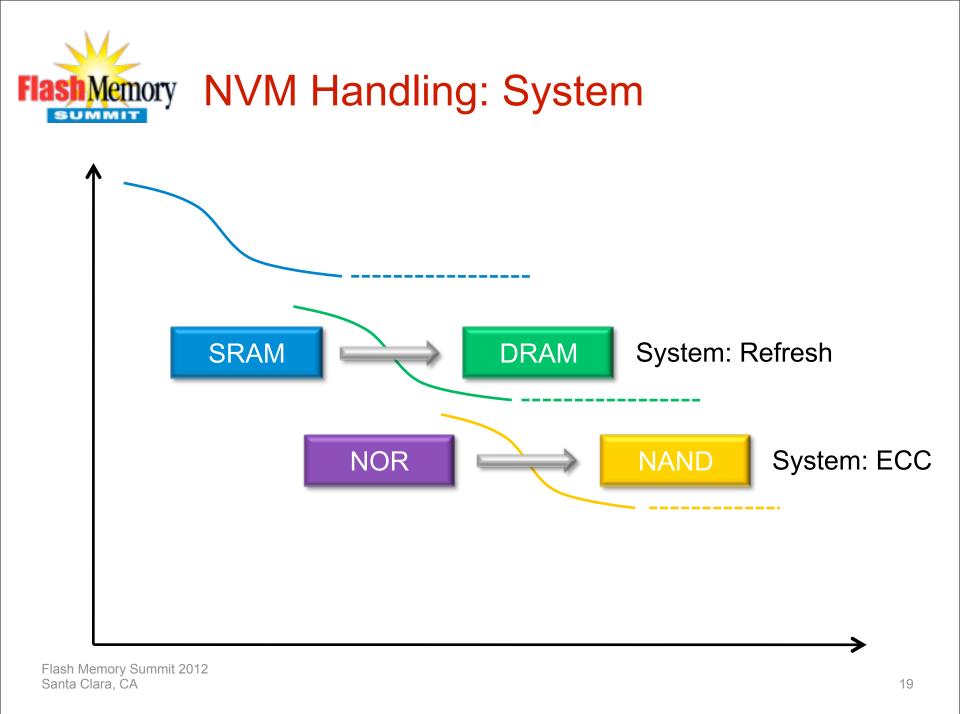

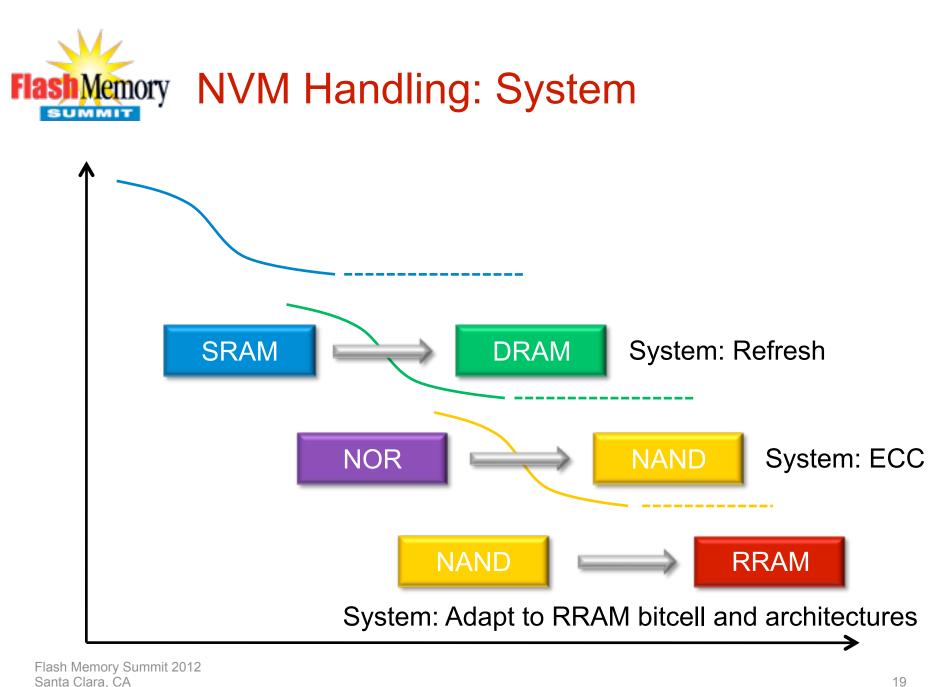

### Flash Memory NVM Handling: \$1B+

Flash Memory Summit 2012 Santa Clara, CA

Trademarks are the property of their respective companies or owners.

15

#### Memory NVM Handling: \$1B+

Flash Memory Summit 2012 Santa Clara, CA

Trademarks are the property of their respective companies or owners.

### Memory NVM Handling: \$1B+

NVM handling makes failing NAND bitcells usable

Requires deep knowledge of bitcell & architecture

Flash Memory Summit 2012 Santa Clara, CA

Trademarks are the property of their respective companies or owners.

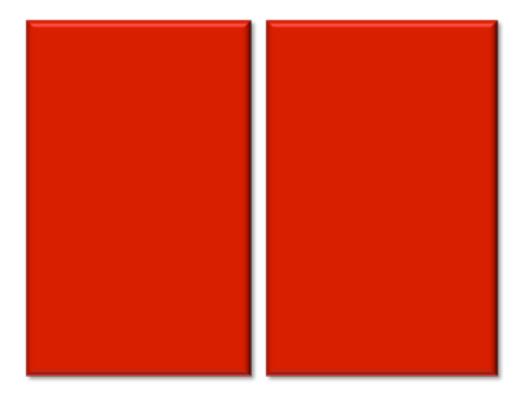

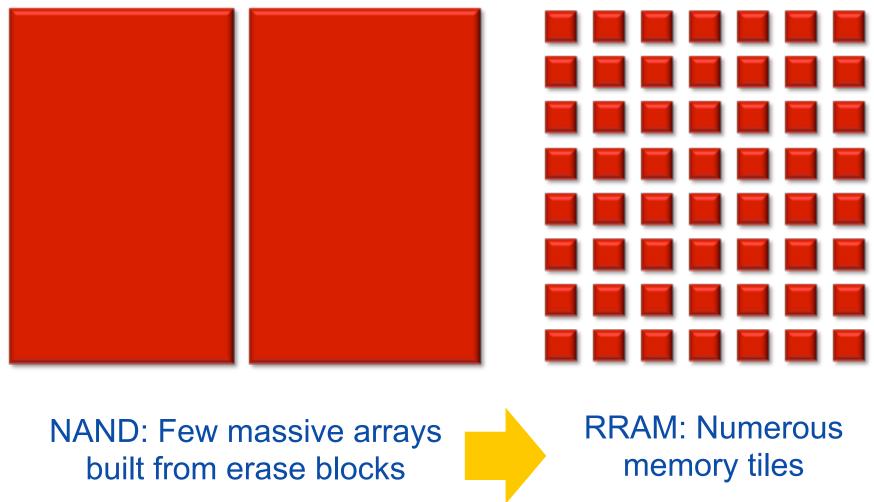

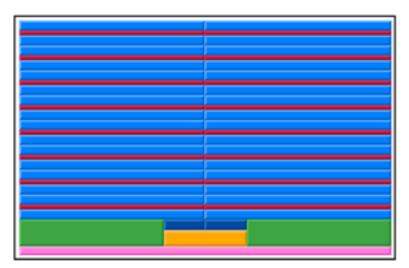

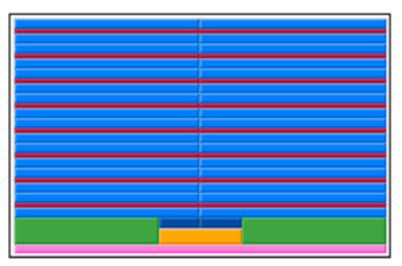

# NAND: Few massive arrays built from erase blocks

1Tb 1R 3D-RRAM (projected)

#### 256Gb PBiCS 3D-NAND (projected)

1Tb 1R 3D-RRAM (projected)

#### 256Gb PBiCS 3D-NAND (projected)

### Flash Memory NVM Handling: Examples

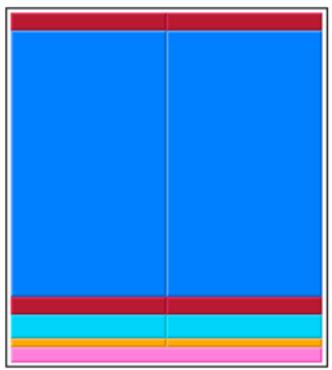

Stacked Vertical

# $\begin{array}{c} {}^{2F^2/N}\\ {}^{2\,Masks\,per\,8\,Layers}\\ 2D \rightarrow 3D \ Bit\\ Interference\end{array}$

# Block $\rightarrow$ Tile Management

### Flash Memory NVM Handling: Examples

Stacked Vertical

| PAGES! |

|--------|

|        |

|        |

# $\begin{array}{c} {}^{2F^2/N}\\ {}^{2\,Masks\,per\,8\,Layers}\\ 2D \rightarrow 3D \ Bit\\ Interference\end{array}$

# Block $\rightarrow$ Tile Management

### Flash Memory NVM Handling: Examples

Stacked Vertical

$\begin{array}{c} {}^{2F^2/N}\\ {}^{2\,Masks\,per\,8\,Layers}\\ 2D \rightarrow 3D \ Bit\\ Interference\end{array}$

# Block $\rightarrow$ Tile Management

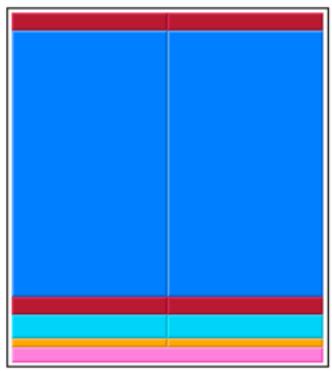

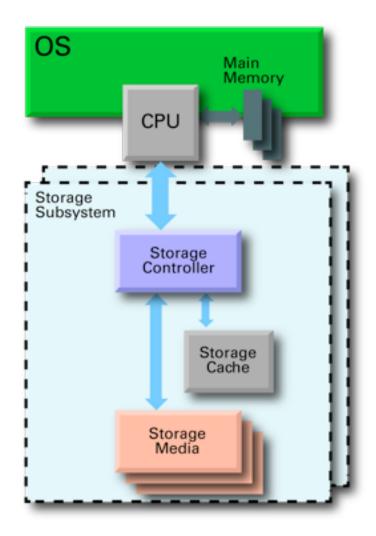

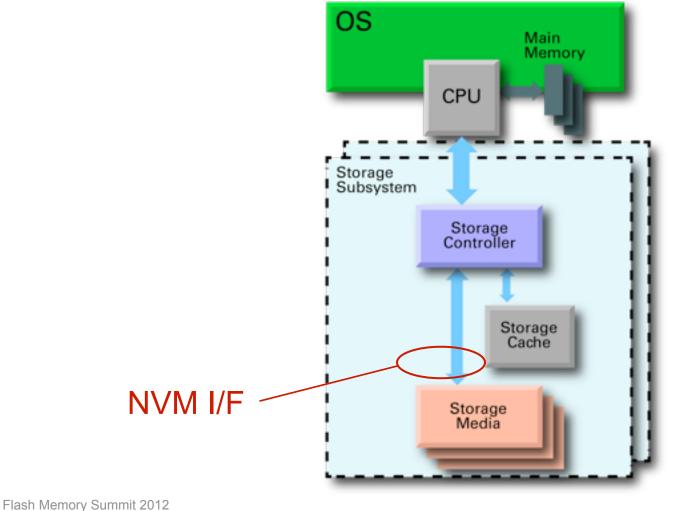

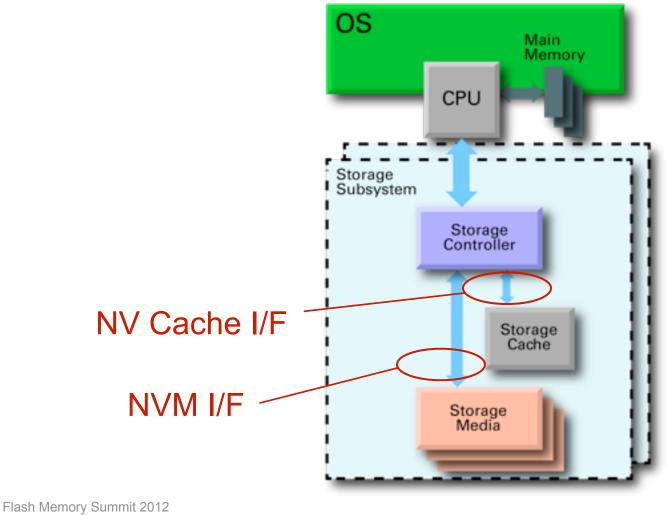

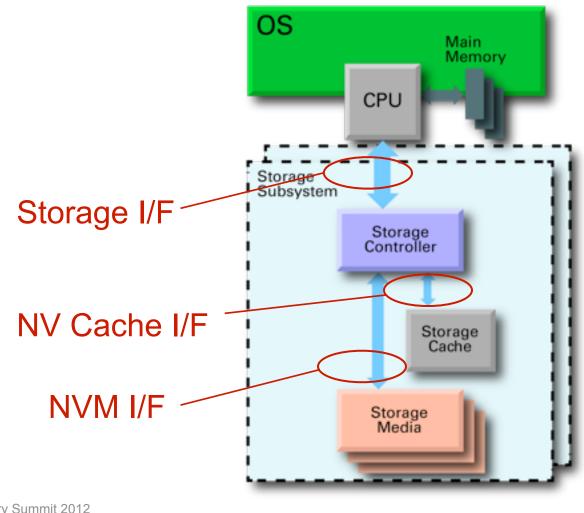

## Flash Memory Interfaces in a Storage System

## Flash Memory Interfaces in a Storage System

Santa Clara, CA

## FlashMemory Interfaces in a Storage System

Santa Clara, CA

### Flash Memory Interfaces in a Storage System

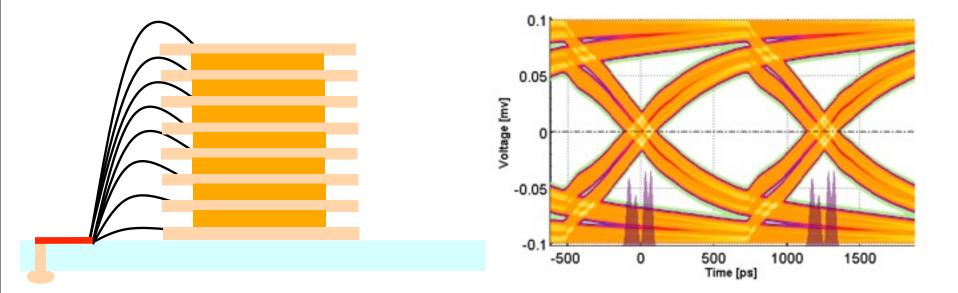

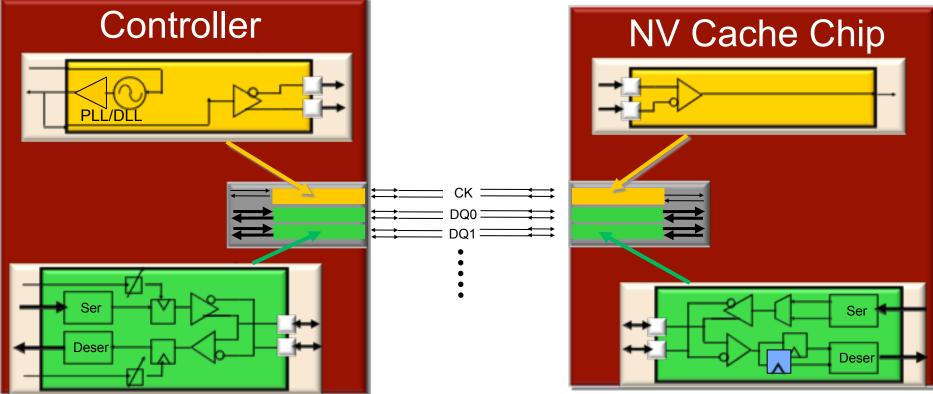

### Flash Memory Driving the NVM Interface speed

| Capacity                 | 8 loads  | 16 loads |

|--------------------------|----------|----------|

| Max Data Rate<br>per pin | 1.2+Gbps | 1Gbps    |

23

| Total Signal<br>Pins (DQ) | Max Data<br>Rate per pin | Read Latency          |

|---------------------------|--------------------------|-----------------------|

| 10 (4 DQ)                 | 4Gbps                    | Low,<br>Deterministic |

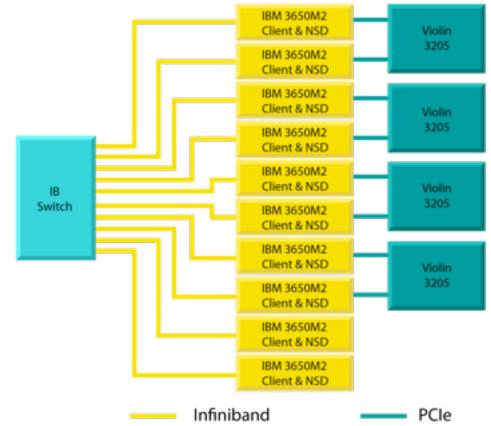

### Storage: Real World Example

#### Project Presto! (2011)

IBM research demonstrated the ability to do policy guided storage management for 10 Billion file environment in 43 minutes. Previous record was 1,591 minutes

- Used cluster of 10 IBM xSeries servers

- IBM's cluster file system (GPFS)

- Placing file system's metadata on new solid-state storage appliance from Violin Memory

#### Cooling is the number one concern.

#### - Server and storage failure due to sustaining high resource utilization.

Flash Memory Summit 2012 Santa Clara, CA Source: Storage Class Memory: Technologies, Systems and Applications – FAST, February 2012

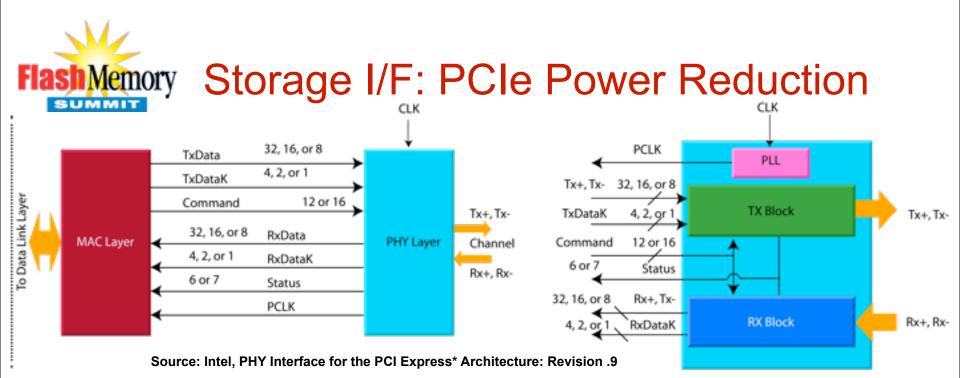

#### Active Power Optimization

- L1 sub-states => finer granularity power management

- Dynamic Bus Sizing Scaling bus width based on changing bandwidth needs

- Resonant techniques to recirculate clock energy

#### Idle Power Optimization

- Fast power On/Off circuits => Deeper power down

- Leakage control

Flash Memory Summit 2012

## INTELLIGENCE -----> MEMORY

## INTELLIGENCE -----> MEMORY

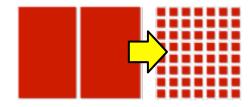

# BEOL MEMORY & LOGIC INTEGRATION

Flash Memory Summit 2012 Santa Clara, CA

28

#### INTELLIGENCE -----> MEMORY

# BEOL MEMORY & LOGIC INTEGRATION

# MESH COMPUTING WITH RRAM STORAGE NODES

Flash Memory Summit 2012 Santa Clara, CA

Thursday, August 23, 12

| 2012 | 2014 | 2016 | 2018 | 2020+ |  |

|------|------|------|------|-------|--|

|      |      |      |      |       |  |

| 2012 | 2014                                                                                                                                                   | 2016                               | 2018 | 2020+ |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|-------|--|

| RRAM | Phase 1:<br>"High Value"<br>Adoption<br>•1T-1R RRAM<br>•Embedded me<br>•NV cache<br>•New character<br>high value<br>•Not as cost se<br>•Establish tech | emory<br>ristics bring<br>ensitive |      |       |  |

| 2012 | 2014                                                                                                                                                 | 2016                                | 2018                                                                                              | 2020+        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------|--------------|

| RRAM | Phase 1:<br>"High Value"<br>Adoption<br>•1T-1R RRAM<br>•Embedded m<br>•NV cache<br>•New characte<br>high value<br>•Not as cost so<br>•Establish tech | emory<br>eristics bring<br>ensitive | Phase 2:<br>NAND Rept<br>•1R RRAM<br>•Data Storag<br>•Tb densities<br>•Lowest cost<br>•Broad adop | le<br>S<br>t |

- Bob Dylan

- Bob Dylan

"Some people feel the rain. Others just get wet."

- Bob Dylan

"Some people feel the rain. Others just get wet."

- Bob Dylan

- Bob Dylan

"Some people feel the rain. Others just get wet."

- Bob Dylan

- Bob Dylan

"Some people feel the rain. Others just get wet."

- Bob Dylan

- Bob Dylan

"Some people feel the rain. Others just get wet."

- Bob Dylan

#### Visit us at Flash Memory Summit Booth #813

E

# REVELUTION The Impact of Emerging Memory

Each major transition in memory technology has been coupled with a revolution in system architectures that exploit the key advantages of the new memory. NAND flash enters its third decade of mass production as strong as ever, but it appears increasingly likely that a new non-volatile memory technology will emerge over the course of this decade to answer the demands of the data center and the mobile consumer.

What are the key advantages of these emerging memories?

What attributes are required to become the successor to NAND flash?

•What sort of revolution will these emerging memories bring to system architectures?

•How (and when) will these new memories bring change to the data center and mobile devices?

32