# Accelerating Data Storage

MRAM as a Fast Storage Tier or Write Cache

Joe O'Hare

Everspin Technologies, Inc.

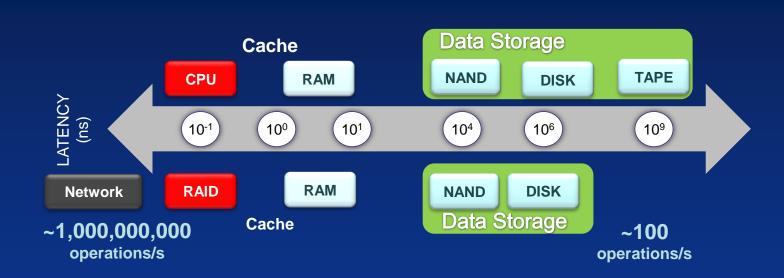

# Storage Performance Gap

### **CPU – Storage gap increasing**

NAND introduces µs latency class for storage Complexity, endurance and power-fail issues

Latency must be predictable & further improved

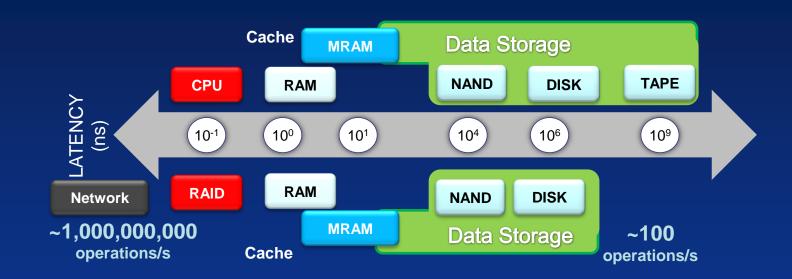

# Storage Performance Gap

## MRAM delivers ns latency class cache & storage

MRAM will complement existing storage technologies by adding a tier of persistent, high performance memory

# Storage Solutions craving ST-MRAM

## MRAM complements solid state & magnetic storage

Improved response time due to low latency & high bandwidth

MRAM as Buffer Memory

MRAM instead of low density DRAM

Better performance & reliability

MRAM as I/O & Network Cache

MRAM instead of NV-DRAM

Better reliability & overall TCO

MRAM as Fast Storage-Tier

MRAM in addition to SSD/HDD

Better IOPS/\$/W & reliability

# nory Features to Support Effective Caching

| Feature                  | Metric                        | Everspin MRAM |

|--------------------------|-------------------------------|---------------|

| Fast random access       | SRAM/DRAM like speed          | ✓             |

| Fast write time          | Symmetric R/W                 | ✓             |

| High bandwidth           | 10.6 GB/s-12.8GB/s            | ✓             |

| High endurance           | 10 <sup>15</sup> Write cycles | ✓             |

| Random Access            | Bit/Byte addressable          | ✓             |

| Power Loss Protection    | Preserve in-flight data       | ✓             |

| Controller Compatibility | Industry support              | ✓             |

| Small Form Factor        | Small BGA or DIMMs            | ✓             |

| Power Fail Circuit       | No SuperCaps/Batteries        | ✓             |

## MRAM Write Cache or Fast Storage Tier

Storage Controller (MRAM Aware)

**NAND ARRAY**

**HOTTEST**

HOT DATA STORAGE

# Building an Ecosystem

### Memory Controller compatibility

- Cadence Denali Databahn memory controller

- FPGA RTL

- Working with many of the leading IP providers and EDA suppliers

### Form Factor

Industry standard component package and DIMMS

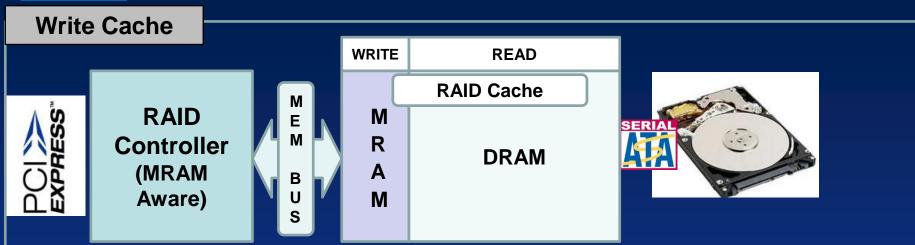

### PCle interface evaluation system

Enabling ease of evaluation and adapted to the latest storage protocols

#### Architecture

- Enable hybrid Cache of MRAM+DRAM

- Use MRAM for Write Cache to protect critical or in-flight data

- MRAM only when Cache size allows (MRAM density increases over time)