### Mechanism of Switching and Related Challenges in Transition Metal Oxide Based RRAM Devices

#### **Rashmi Jha** and Branden Long

Dept. of Electrical Engineering and Computer Science University of Toledo Toledo, Ohio, 43606, USA

e-mail: Rashmi.jha@utoledo.edu, Ph: 419-530-8145

Flash Memory Summit 2012 Santa Clara, CA

2

### **ReRAM** Materials and Switching

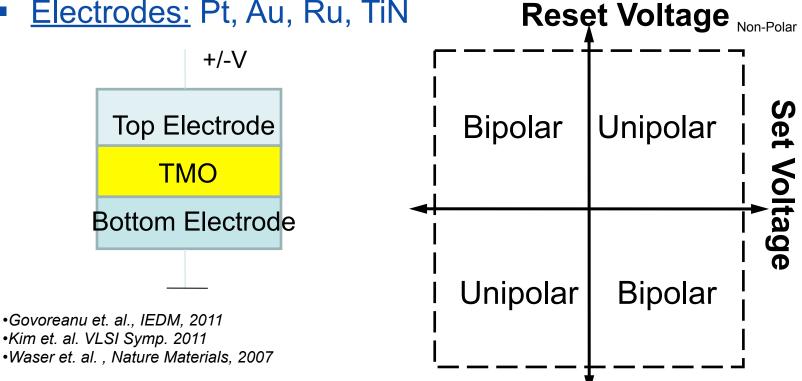

- Switching Transition Metal Oxides (TMO): HfO<sub>2</sub> TaOx, TiOx, NiOx, CuOx, AlOx, AlON

- Electrodes: Pt, Au, Ru, TiN

### ITRS Roadmap for Non-Volatile Memories

|                          | DRAM            | NAND<br>Flash    | РСМ             | FeRAM            | STT-<br>MRAM     | ReRA<br>M                        |

|--------------------------|-----------------|------------------|-----------------|------------------|------------------|----------------------------------|

| Feature Size (nm)        | 36              | 22               | 45              | 180              | 65               | <65                              |

| Cell Area                | 6F <sup>2</sup> | 4 F <sup>2</sup> | 4F <sup>2</sup> | 22F <sup>2</sup> | 20F <sup>2</sup> | 4F <sup>2</sup> ,8F <sup>2</sup> |

| W/E Time                 | <10 ns          | 1/0.1<br>ms      | 100 ns          | 65 ns            | 35 ns            | <10 ns                           |

| Retention                | 64 ms           | 10 y             | >10 y           | 10 y             | >10 y            | >10 y                            |

| Durability               | > 1E16          | 1E4              | 1E9             | 1E14             | >1E12            | <u>1E12</u>                      |

| W/E Voltage (V)          | 2.5             | 15               | 3               | 1.3-3.3          | 1.8              | <1                               |

| Read Voltage (V)         | 1.8             | 1.8              | 1.2             | 1.3-3.3          | 1.8              | <1                               |

| Write Energy (J/<br>bit) | 4E-15           | >2E-16           | 6E-12           | 3E-14            | 2.5E-12          | <u>1E-13</u>                     |

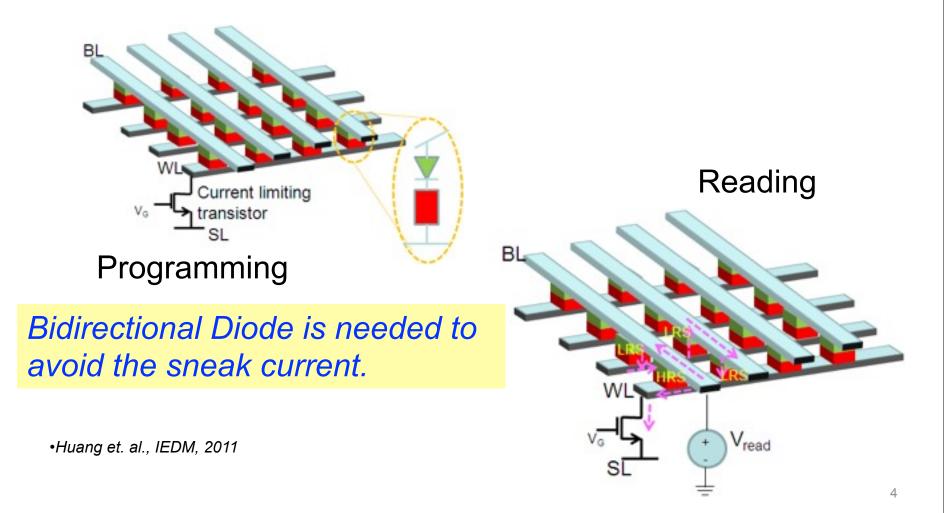

### Flash Memory Crossbar Memories with ReRAM

### Flash Memory Target Device Specifications

| Parameters          | ReRAM                |  |  |

|---------------------|----------------------|--|--|

| V <sub>set</sub>    | ~1V                  |  |  |

| I <sub>set</sub>    | 1µA                  |  |  |

| V <sub>reset</sub>  | -1V                  |  |  |

| I <sub>reset</sub>  | 1µA                  |  |  |

| T <sub>switch</sub> | ~10-100 ns           |  |  |

| ROFF/RON            | 10-1000              |  |  |

| Energy (J/bit)      | ~1x10 <sup>-15</sup> |  |  |

| Endurance           | >1x10 <sup>6</sup>   |  |  |

| Temperatures        | 85°C                 |  |  |

| Parameters                        | Diode              |  |  |

|-----------------------------------|--------------------|--|--|

| V <sub>T+</sub>                   | <1V                |  |  |

| I <sub>ON+</sub>                  | 1µA                |  |  |

| V <sub>T-</sub>                   | <-1V               |  |  |

| I <sub>ON-</sub>                  | 1µA                |  |  |

| I <sub>ON</sub> /I <sub>OFF</sub> | >1x10 <sup>4</sup> |  |  |

| Temperatures                      | 85°C               |  |  |

ITRS, 2011

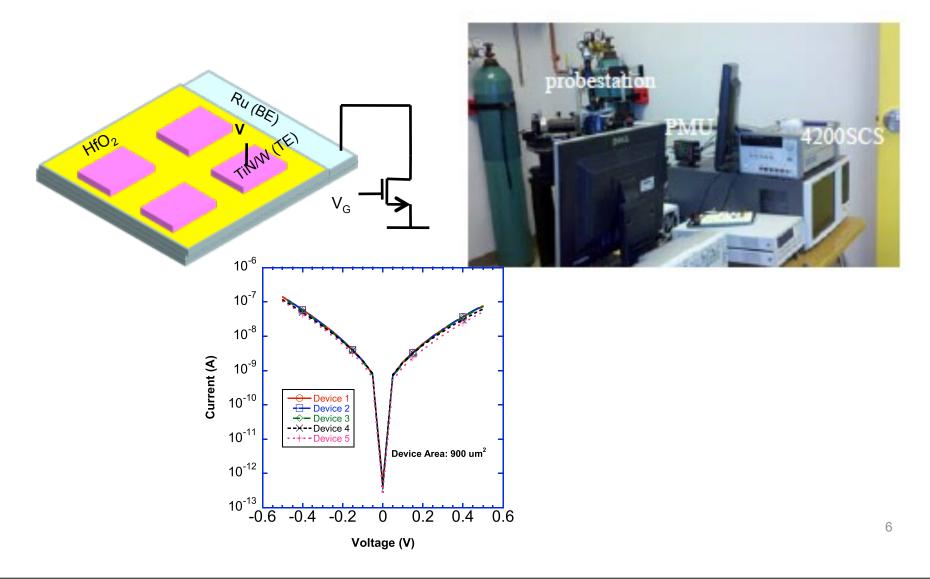

## ReRAM Fabrication & Electrical Characterization

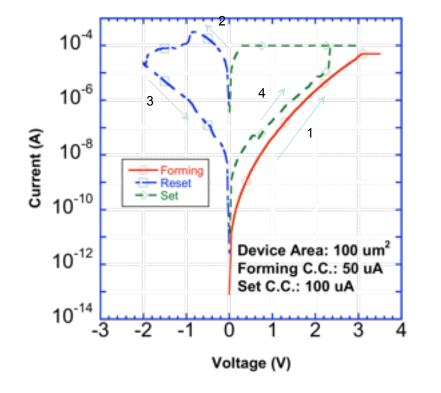

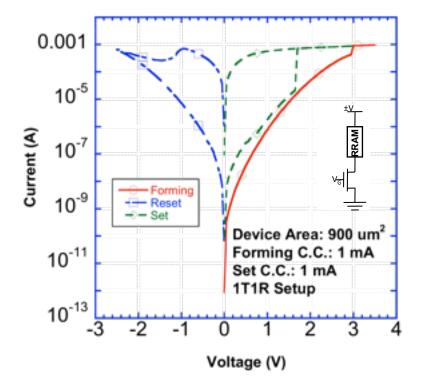

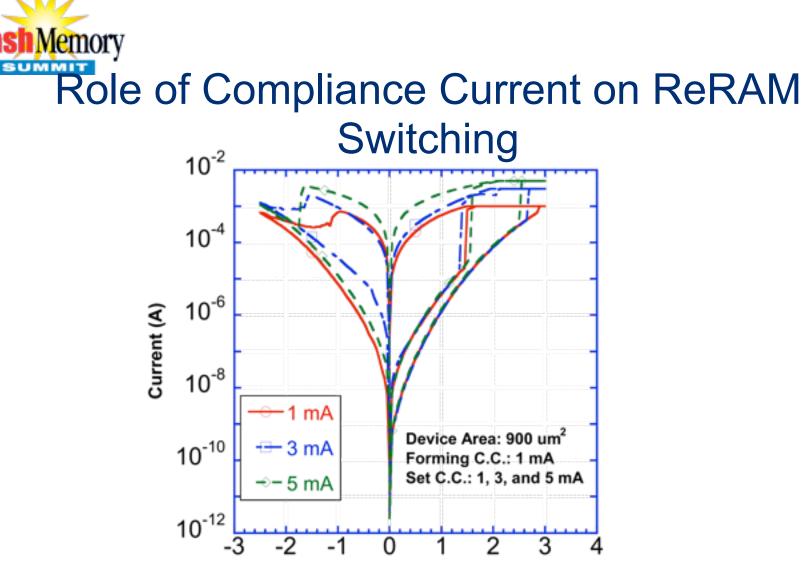

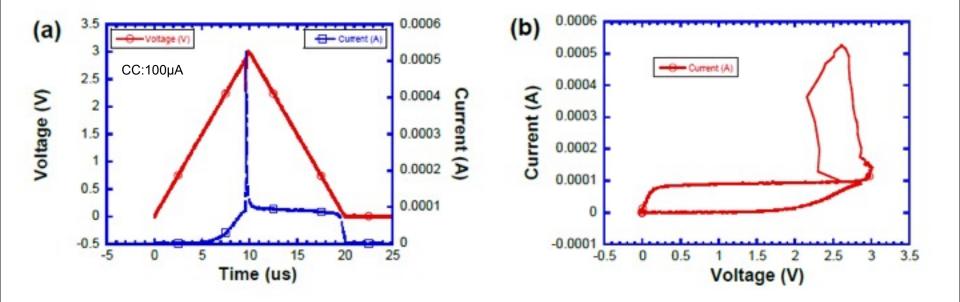

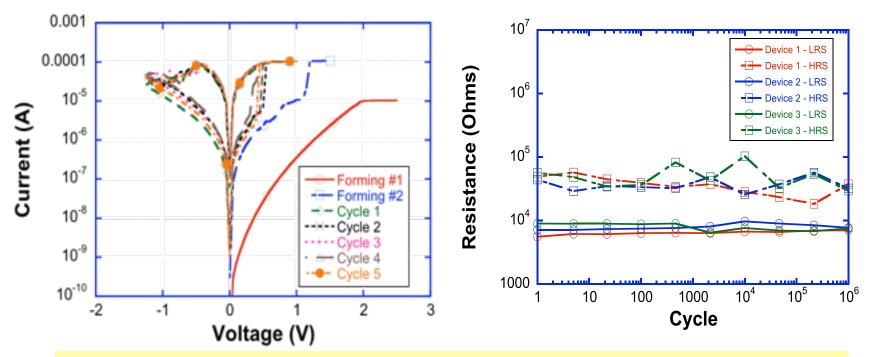

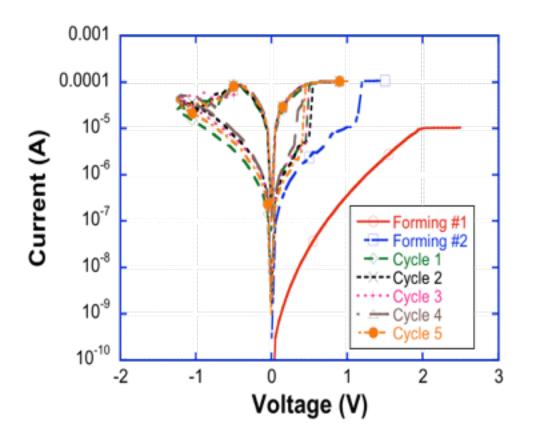

### **DC Switching Characteristics**

8

Compliance current ( $I_{cc}$ ) plays a major role in governing resistance in LRS,  $V_{reset}$ ,  $I_{reset}$ .

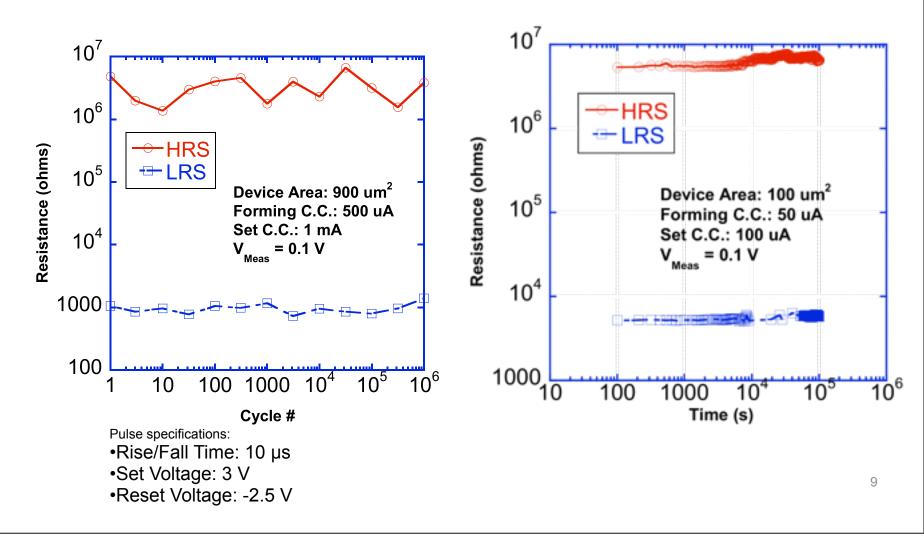

### **Durability and Retention Testing**

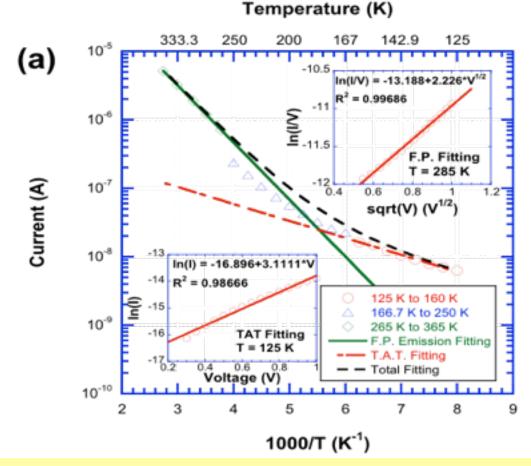

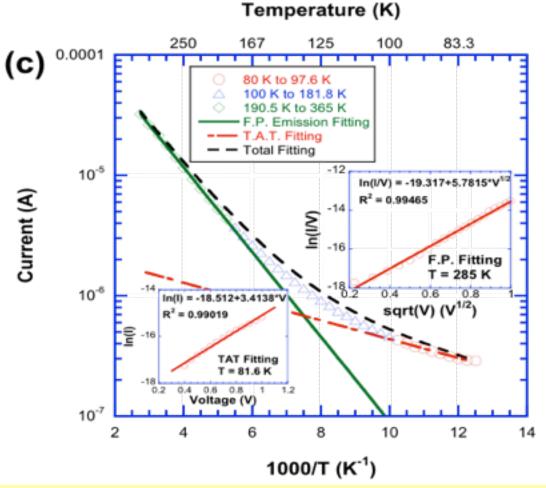

## Charge Transport Mechanism: VRS

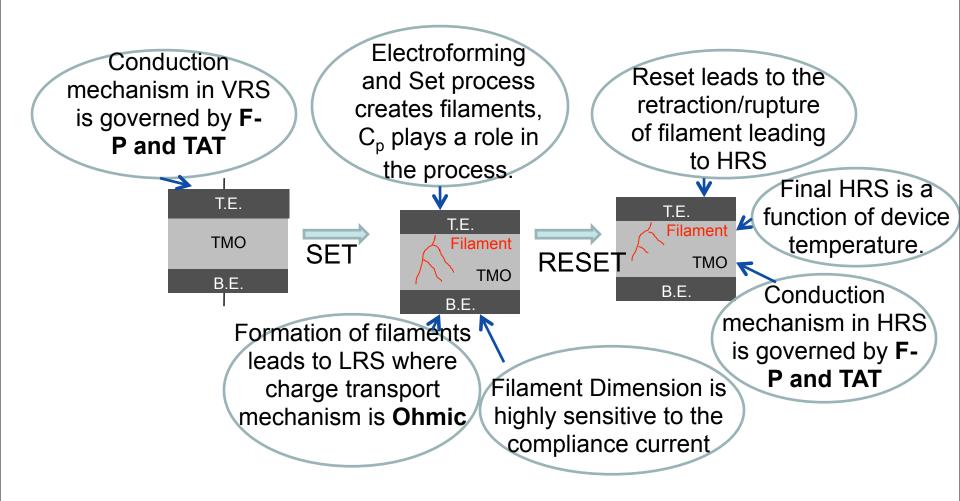

Conduction mechanism in as-fabricated (VRS) samples is governed by a combination of F-P and TAT through dielectric.

Long et. al, accepted for publication, App. Phys. Lett., 2012

## Temperature (K)

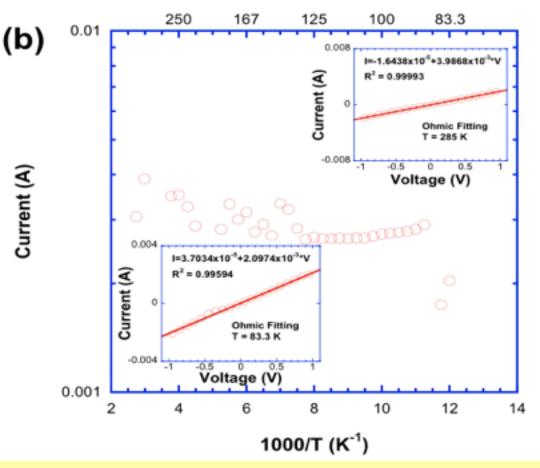

Conduction mechanism in Low Resistance State(LRS) is governed by Ohmic conduction through dielectric.

Long et. al, accepted for publication, App. Phys. Lett., 2012

### Memory Charge Transport Mechanism: HRS

Conduction in High Resistance State(HRS) is governed by a combination of F-P and TAT mechanisms in dielectric.

Long et. al, accepted for publication, App. Phys. Lett., 2012

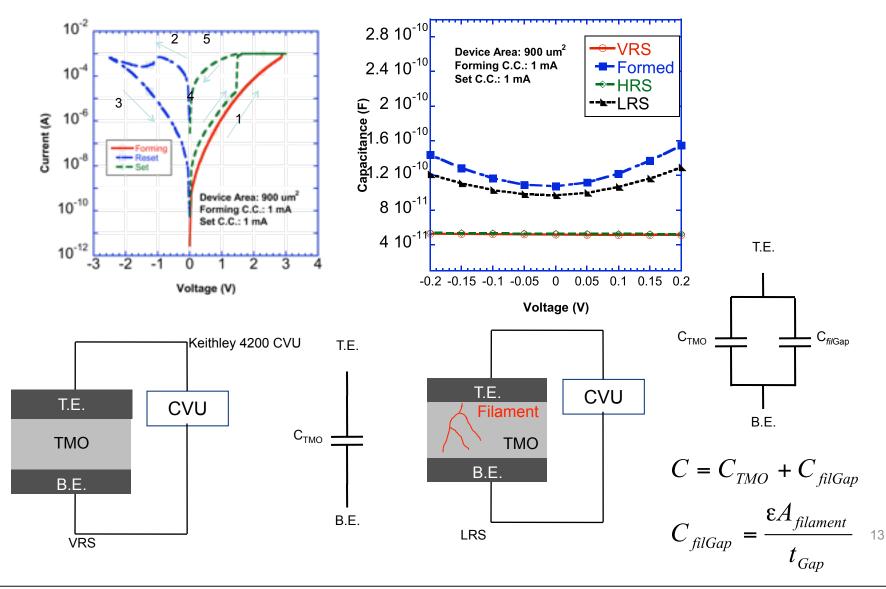

#### **Capacitance in Different Resistive States**

- Necessity for Electroforming

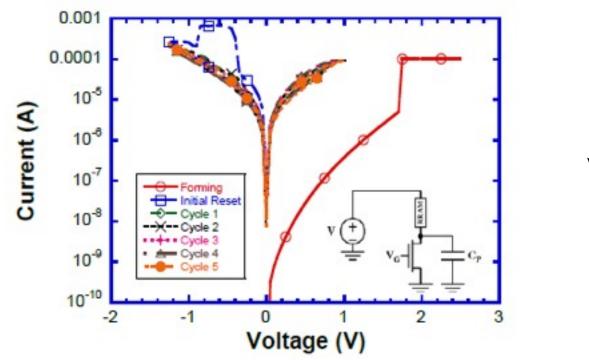

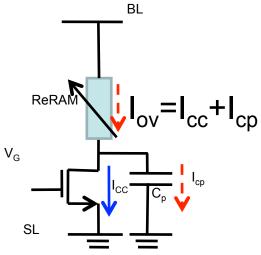

- Parasitic Capacitance (C<sub>p</sub>) and Current Overshoot

- High Reset Currents

- Variability

- Need for a bidirectional selector diode

### Electroforming, Cp, Current Overshoot

Overshoot in current over the compliance current due to  $C_p$  can lead to uncontrolled filament dimensions which can be a primary cause of variability.

Tuesday, August 28, 12

Flash Memory Novel Dual-Step Forming Process

A careful forming can mitigate this issue. However forming-free switching will be an ideal choice. <u>Graduate student Branden Long has a poster in Flash</u> <u>Memory Summit on forming-free options.</u>

Flash Memory Reset Mechanism in ReRAM

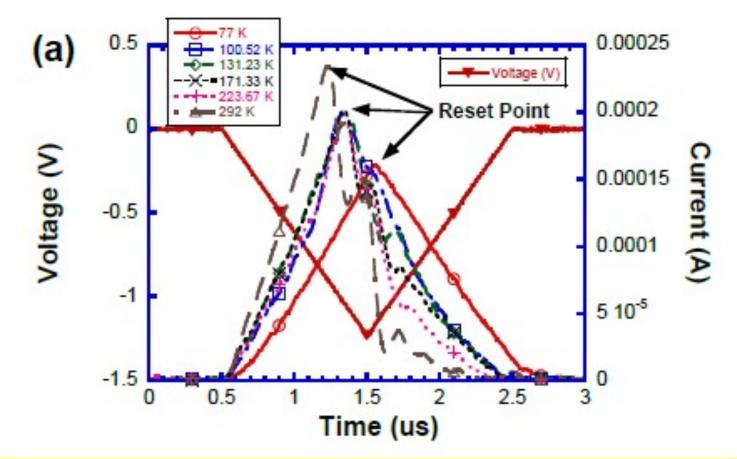

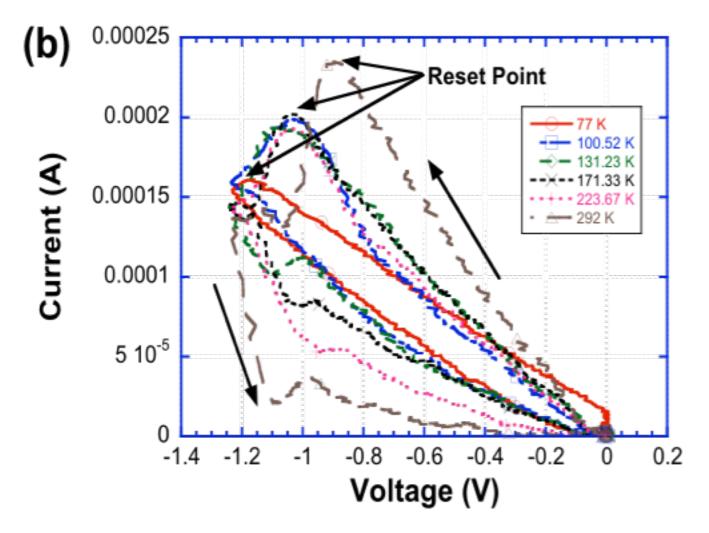

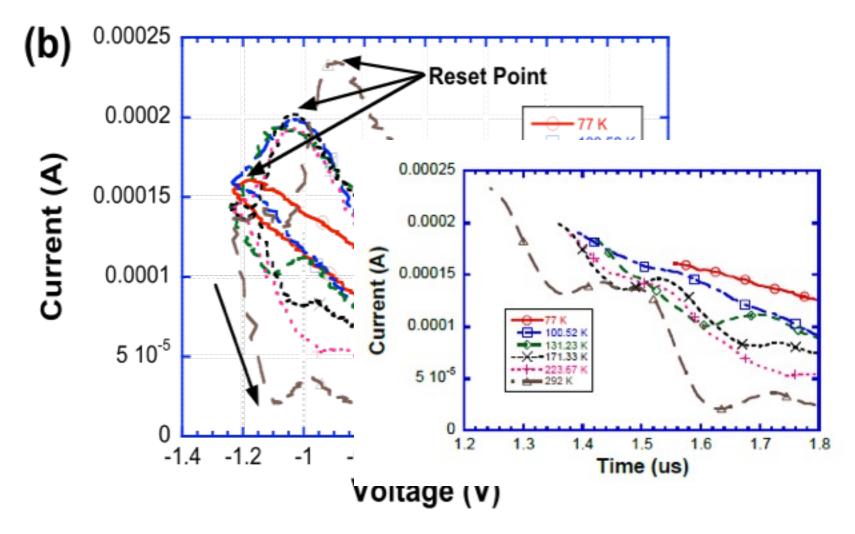

RESET voltage, current, and time is a function of temperature.

Tuesday, August 28, 12

**Flash** Memory **Reset Mechanism in ReRAM**

RESET voltage, current, and time is a function of temperature.

Tuesday, August 28, 12

SUMMIT

### **Temperature Dependent Reset Dynamics**

Tuesday, August 28, 12

19

### **Temperature Dependent Reset Dynamics**

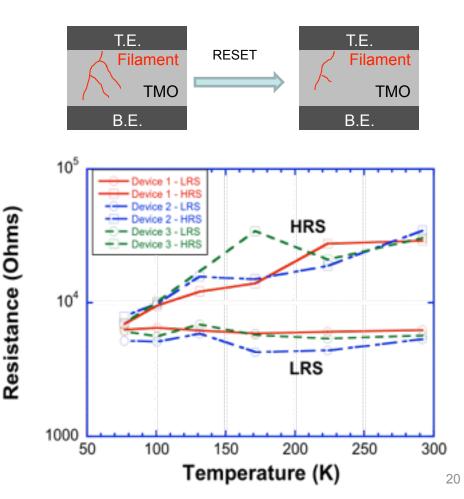

# Final Reset vs. Temperature

- Mechanism of Reset is a multiple step process:

- A critical power is needed to initiate the reset process

- Continued reset results from subsequent reoxidation of filament

- National Science Foundation for funding

- Midwest MicroDevices LLC, Toledo, Ohio, for process metrology

- Sematech Incorporation