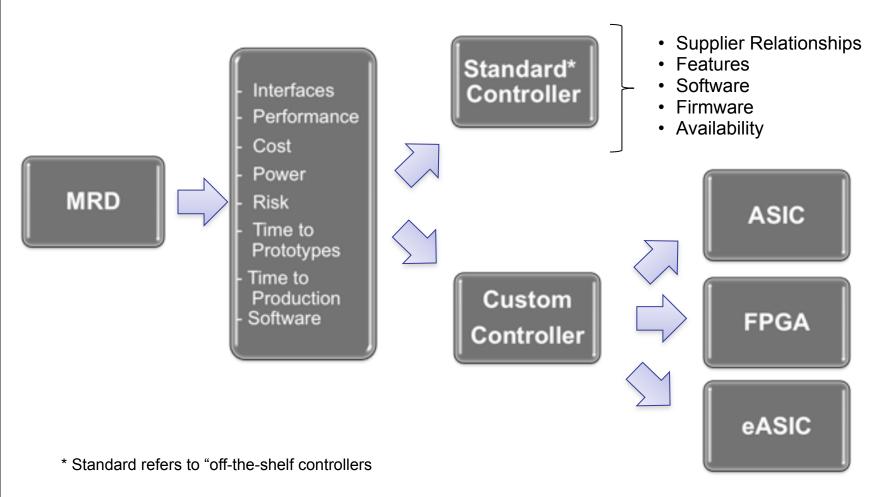

# Navigating The Enterprise Controller Landscape

Narinder Lall - Product Marketing Director eASIC Corporation

narinder@easic.com

#### Flash Memory Controller Decisions

#### Use a Standard Controller?

- 1. Immediate Availability

- 2. Short time to production

- 3. You have no In-house custom FLASH management IP

- 4. You have no custom chip design expertise

- 1. "Me Too" SSD products

- 2. Hard to differentiate & create strategic value

- 3. Not in control of own destiny

- 4. May not be able to use the latest FLASH

- 5. What support will you get?

- 6. Will it be available tomorrow?

#### Flash Memory Which Standard Controller?

**LSI SandForce**

MARVELL

IDT

#### Design Own Custom Controller?

- 1. Use the latest FLASH

- 2. Leverage knowledge of "system" to optimize FLASH management

- 3. Implement the latest/best-in-class IP

- LDPC, PCIe/SATAe, compression

- 4. Differentiate Create strategic value

- 5. Control pace of new SSD introduction

- Need custom chip design expertise

- 2. Longer time to production

- 3. Can be expensive (e.g. ASIC)

- 4. Return-on-Investment?

# Flash Memory Custom Controller Platforms

|                             | FPGA                                                                                                                                                                                                                        | <b>@</b> ASIC <sup>*</sup>                                                                                                                                                                                                                      | Cell-based ASIC                                                                                                                                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Customization               | Many SRAMs used to configure chip                                                                                                                                                                                           | ONE MASK LAYER to configure entire chip                                                                                                                                                                                                         | ALL MASK LAYERS<br>to configure chip                                                                                                                                                                             |

| Design & Test<br>Structures | <ul> <li>ALREADY IN-BUILT e.g</li> <li>User configures/connection verifies design</li> </ul>                                                                                                                                | <b>5</b>                                                                                                                                                                                                                                        | Structures are created, connected & verified for every design                                                                                                                                                    |

| What<br>This<br>Means       | <ul> <li>✓ Low Tens \$K NRE</li> <li>✓ Fast design time</li> <li>✓ Fast time-to-market</li> <li>✓ Low risk</li> <li>&lt;300MHz Performance</li> <li>Highest device cost</li> <li>Highest power</li> <li>CRAM SEU</li> </ul> | <ul> <li>✓ 500MHz Performance</li> <li>✓ Lowest cost of ownership</li> <li>- Low hundreds \$K NRE</li> <li>- Low device cost</li> <li>- Fast design time</li> <li>- Fast time-to-production</li> <li>✓ Low power</li> <li>✓ Low risk</li> </ul> | <ul> <li>✓ &gt;500MHz Performance</li> <li>✓ Lowest device cost</li> <li>✓ Lowest power</li> <li>• \$Millions NRE</li> <li>• Long design time</li> <li>• Long time to production</li> <li>• High risk</li> </ul> |

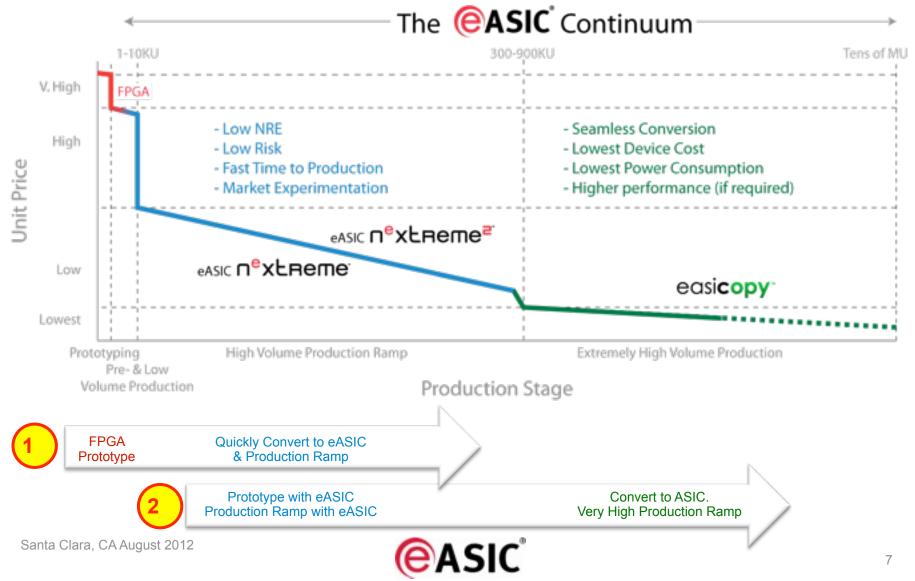

# **Custom Controller Strategies**

## **Custom Controller Strategies**

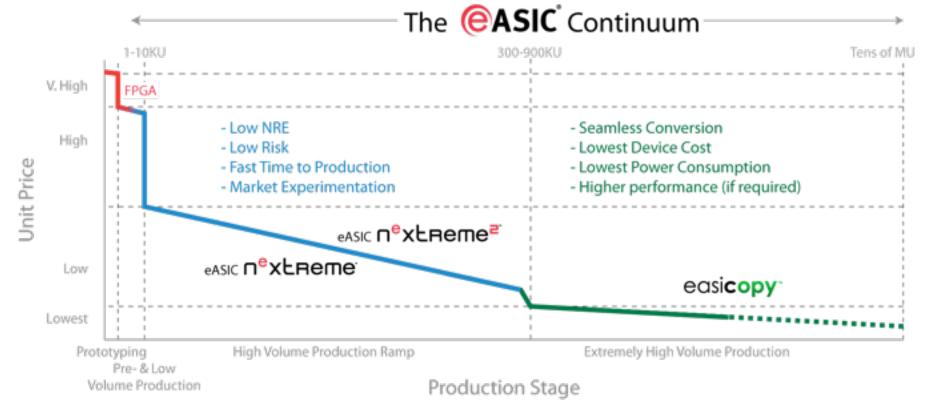

## Memory eASIC FLASH Controller Platforms

Production Volume To 1MU (Higher with ASIC Migration)