# Session 302-A: PCle Storage - 2 (PCle Storage Track)

Flash Drives: Block Storage or Memory?

Tony Roug, Virident

Director Solution Architecture

- Storage Class Memory: The Bridge

- Access Models: The Architecture

- Access Capabilities: The Value

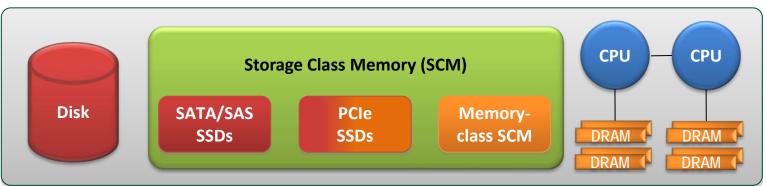

## Flash Memory Storage Class Memory

| Attribute           | Disk                  | SATA/SAS<br>SSDs         | PCle<br>SSD                    | Memory-class<br>SCM         | DRAM       |

|---------------------|-----------------------|--------------------------|--------------------------------|-----------------------------|------------|

| Capacity (GB)       | 100's-1000's          | 100's                    | 100's-1000's                   | 100's-1000's                | 10's-100's |

| Read<br>performance | 10's ms,<br>~100 MB/s | 100's us,<br>~100's MB/s | 50 – 75 us,<br>2 – 4 GB/s      | 200 – 400 ns,<br>2 – 5 GB/s | ~100 ns,   |

| Write performance   | 10's ms<br>~100 MB/s  | 100's us<br>~100 MB/s    | ~25 – 50 us,<br>~0.5 – 1+ GB/s | ~5 us,<br>2-5 GB/s          | 10's GB/s  |

### PCIe SSDs established, Memory-class emerging

- Storage Class Memory: The Bridge

- Access Models: The Architecture

- Access Capabilities: The Value

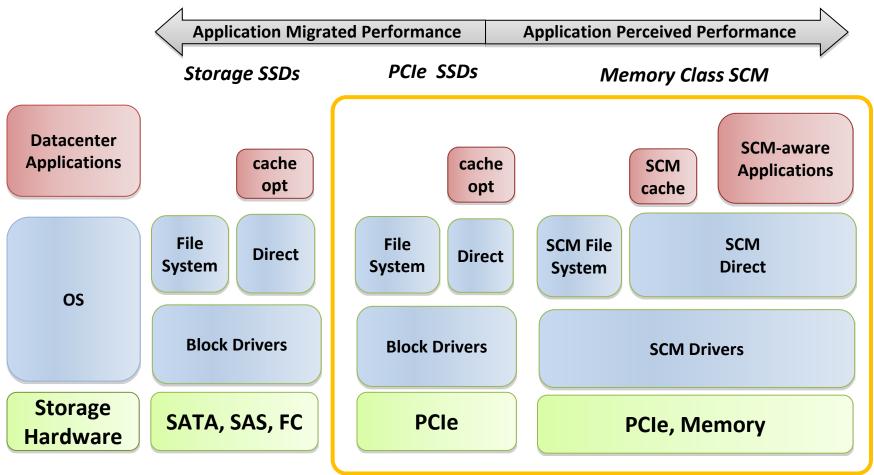

## Block versus Memory access

Optimization required for applications to realize memory class benefit

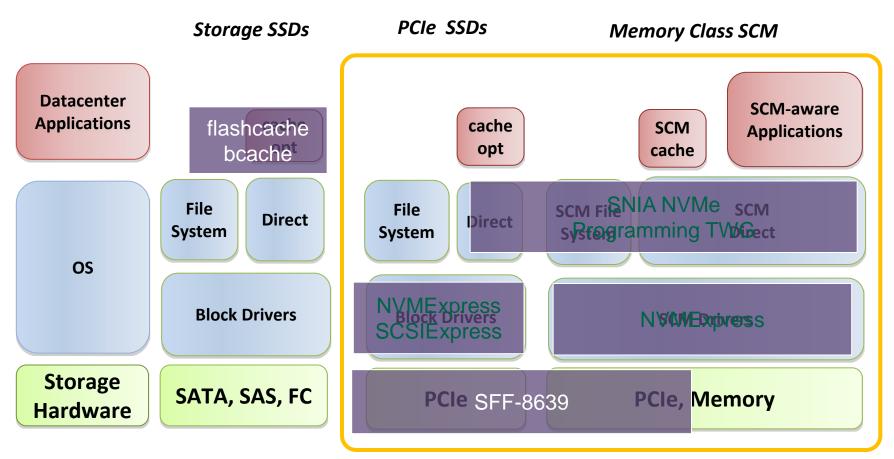

## Open industry directions

### Industry agreement for optimized architecture in place

- Storage Class Memory: The Bridge

- Access Models: The Architecture

- Access Capabilities: The Value

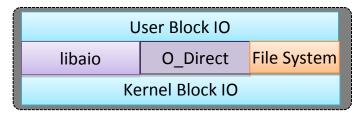

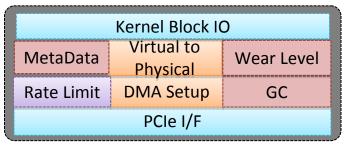

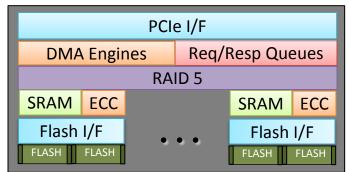

# Example PCIe Block Capabilities: Virident FlashMAX

#### **User Level**

- File open and close, file read and write, raw read and write

- Multiple threads through libaio

- Direct DMA from user to board/board to user through o\_direct

- CLI: monitor, diag, beacon, secure erase

#### Kernel Level

- block register: register, unregister, open, release, ioctrl

- block transfer: request, queue

- DMA scatter/gather: blk rg map sg

- rate limit: guaranteed minimum performance at 100% capacity

- wear leveling: identification/adaptation to app access patterns

#### **Board Level**

- partition options: 512 and 4K sector size

- write acceleration mode: maxperformance, maxcapacity

- · reliability option: raid5 enabled/disabled

### PCIe SSD optimizations within a block level interface

# NVM Express: "memory class" capabilities?

| Function       | NVMExpress 1.0 Capability                    | Block Compatibility  |  |

|----------------|----------------------------------------------|----------------------|--|

| Basic          | Read, Write                                  | Read, Write          |  |

| Features       | Flush                                        | Sync Cache           |  |

|                | Format                                       | Format               |  |

| ACID           | Fused Operations                             | Compare and Write    |  |

| Operations     | Atomic Write Unit                            | ACID Conshilition    |  |

|                | Write Atomicity                              | ew ACID Capabilities |  |

| Performance,   | Queues/PRP                                   |                      |  |

| Endurance,     | Data Set Management: Incompressible, Access  |                      |  |

| and Efficiency | Size, Write Prepared, Sequential Read/Write, | New Performance      |  |

| Features       | Access Freq, Access Latency                  | Capabilities         |  |

|                | Compare                                      |                      |  |

|                | Namespaces                                   |                      |  |

|                | Deallocate                                   | TRIM/UNMAP           |  |

|                | Power Management                             | Start Stop           |  |

| Data           | End-to-end Protection + Metadata             | DIF/DIX              |  |

| protection     | Format Secure Erase                          | Secure Erase         |  |

|                | Write uncorrectable                          | Write Long           |  |

|                | Write protect                                | WRPROTECT            |  |

New capabilities make "memory class" access possible, but not easy

parita Orara, CA

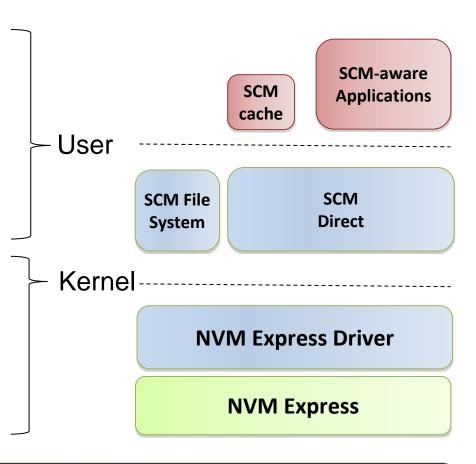

## Enabling SCM: Making it easy

- streamline the application access path:

e.g. RDMA access

- 2. **offer improved semantics**: e.g. atomicwrite

- 3. **simplify caching implementations**: e.g. key-value store,

- 4. **construct cluster-level solutions**: e.g. synchronize cross-server activities and orchestrate server to SAN data movement

- 5. emulate memory: e.g. mmap and malloc

- expose internals of flash management:

e.g. optimized file system with snapshot,

cross-card data transfers, trading capacity

vs performance

Create industry standard capabilities enabling memory class access

- Storage Class Memory:

- First level value enabled by block mode

- Access Models:

- NVM Express enables memory class usage models

- Access Capabilities:

- Industry agreement on application enabling technology launched

- SNIA Programming TWG

## **Thanks**

Tony Roug

Phone: 4085829647

Email: tonyr@virident.com