## Design Considerations for UFS & eMMC Controllers

Andrew Haines

VP Marketing

Arasan Chip Systems, Inc.

- Mobile Storage in SoC

- Challenges in Mobile Storage Controller Designs

- Enabling Mobile Storage Design Ecosystem

- Summary

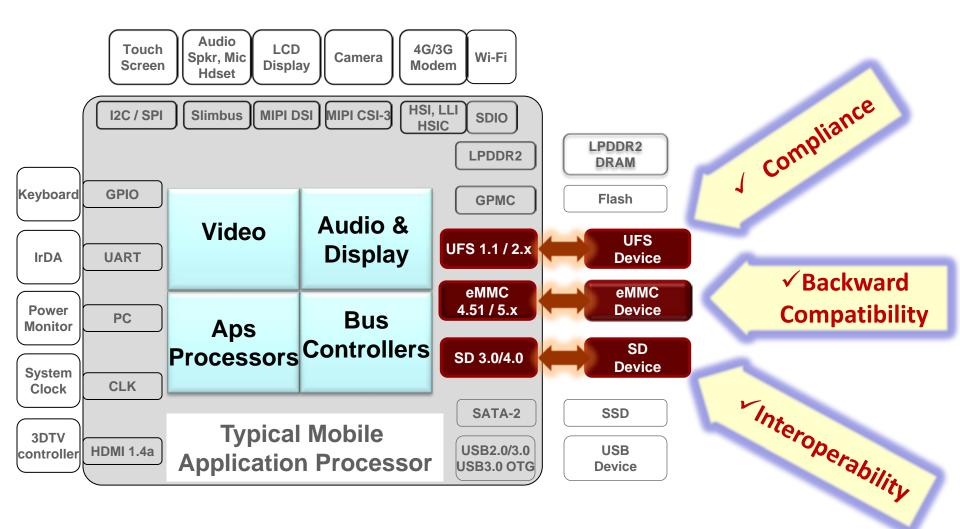

### Multiple Mobile Storage Interfaces in Application Processor

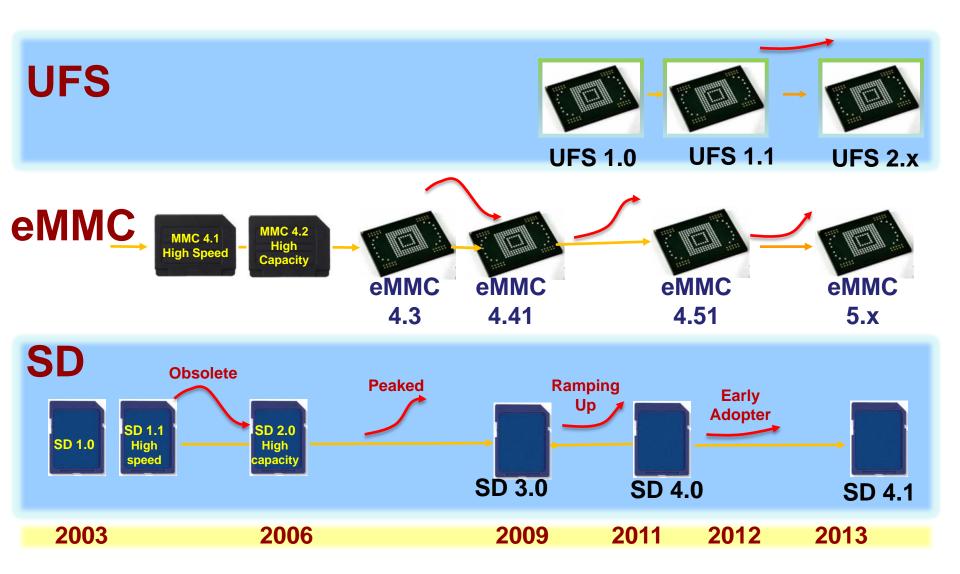

### Mobile Storage Evolution Faster Than Ever

## Challenges of Backward Compatibility eMMC

|                   | eMMC<br>4.41           | eMMC<br>4.51      | eMMC<br>5.0              |  |

|-------------------|------------------------|-------------------|--------------------------|--|

| Max<br>Throughput | High Speed<br>832 Mbps | HS200<br>1.6 Gbps | HS400<br>3.2 Gbps        |  |

| Data Lines        | 4 or 8-bit             |                   | 8-bit                    |  |

| Signal Count      | 10 Pins                |                   | 11 Pins<br>(Data Strobe) |  |

| IO Voltages       | 1.2 V / 1.8 V<br>3 V   |                   | 1.2 V / 1.8 V            |  |

| Interface         | DDR-52                 | HS200             | HS400                    |  |

| Data Strobe       | No                     |                   | Yes                      |  |

| Tuning<br>(Read)  | No                     | Yes               |                          |  |

| Clock (MHz)       | 0 – 52 MHz             | 0 – 200 MHz       |                          |  |

#### emory eMMC Compliance

- eMMC Device spec published by JEDEC

- Compliance can be done through 3<sup>rd</sup> party

Compliance Testers

- No formal compliance guidelines

# **Challenges of Backward Compatibility UFS**

|                      |                                | UFS 1.0                                             | UFS 1.1 | UFS 2.0  |

|----------------------|--------------------------------|-----------------------------------------------------|---------|----------|

| Transaction<br>Layer | Host<br>Interface              | HCI 1.0                                             | HCI 1.1 | HCI 2.0  |

| Link<br>Layer        | UniPro™                        | v1.40 v1.41                                         |         | v1.60    |

|                      | # of Lanes                     | Single Lane Single Lane                             |         | 2-Lane   |

| Physical<br>Layer    | M-PHY                          | v1.0                                                | v2.0    | v3.0     |

|                      | Data Rate                      | 1.5 Gbps 2.9 Gbps                                   |         | 5.8 Gbps |

|                      | # of Lanes                     | 1                                                   |         | 2        |

|                      | Interface                      |                                                     |         |          |

|                      | Diff<br>V <sub>peak-peak</sub> | 500 mV Max (non-terminated) 250 mV Max (terminated) |         |          |

Source: JEDEC

### Flash Memory UFS 1.1 Compliance

|                      | Protocol | Rev. | Test Spec                | Certification     |  |

|----------------------|----------|------|--------------------------|-------------------|--|

| Transaction<br>Layer | UFS      | 1.1  | UFS<br>Test Spec<br>v1.0 | UFSA              |  |

| Link Layer           | UniPro   | 1.41 | UniPro<br>CTS_v1.0_r01   | MIPI /<br>UNH-iOL |  |

| PHY Layer            | M-PHY    | 2.0  | M-PHY<br>CTS_v0.99       |                   |  |

#### **Design Challenges**

Can I have all these validated before starting my SoC design?

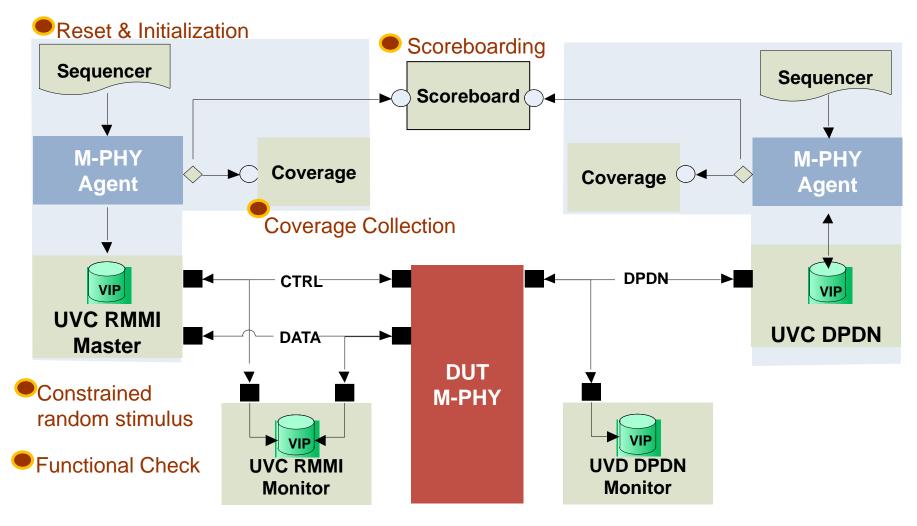

#### M-PHY® Verification Before Silicon

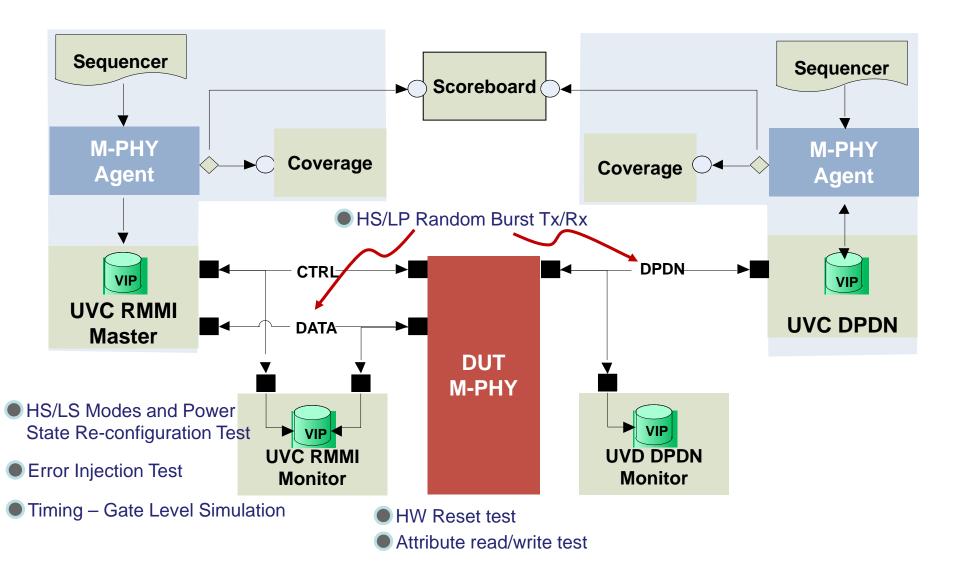

### M-PHY Verification Before Silicon

#### **M-PHY Verification Cases**

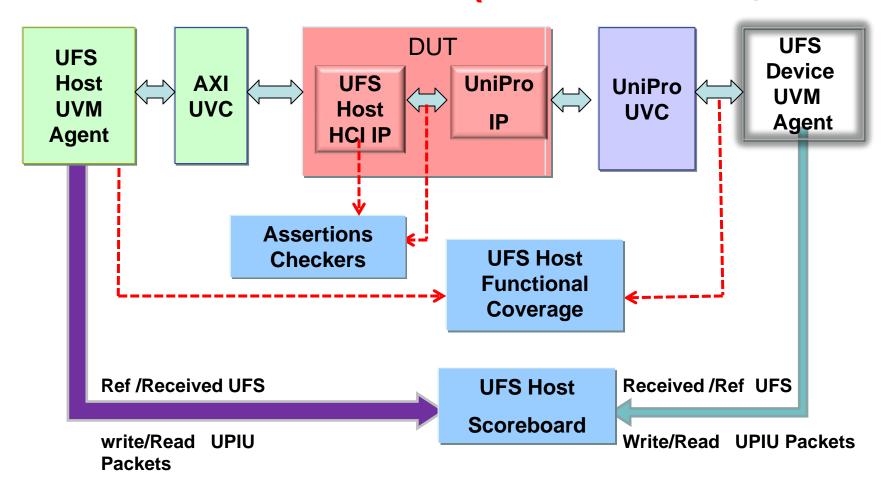

### **UFS Controller Verification Before Silicon (UFS-HCI + UniPro)**

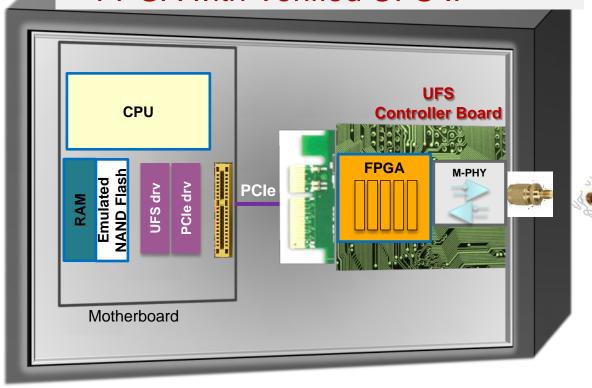

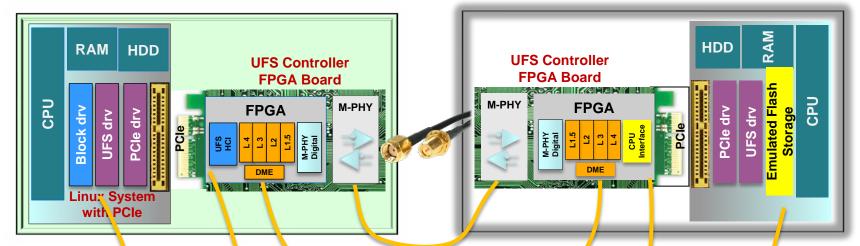

#### Migrate to FPGA based System

- A black-box approach enables quick access to a validation platform

- FPGA with Verified UFS IP

### FPGA System for Device Validation & Software Development

Host

**Device**

**Tested M-PHY Signals**

**Certified UniPro**

Verified and Tested UFS-HCI or System Bus Interface

Verified and Tested Driver and Stacks

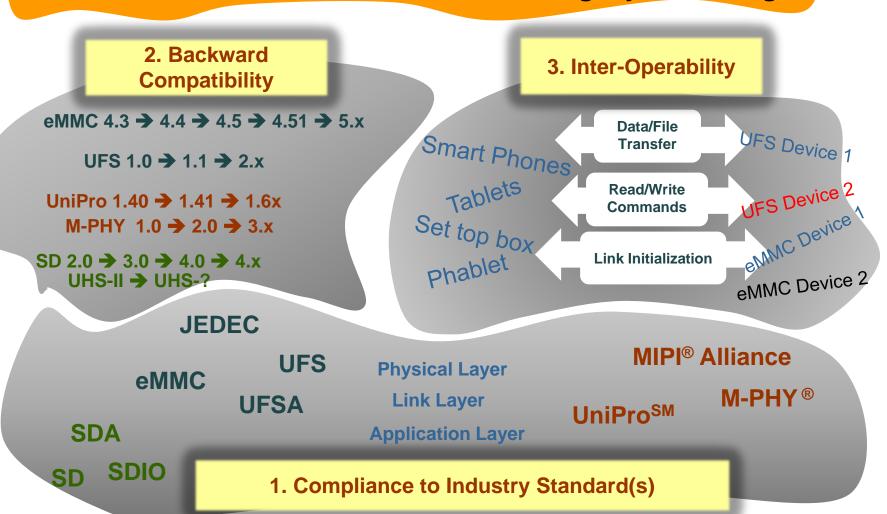

# **Enabling UFS/eMMC Design Ecosystem**

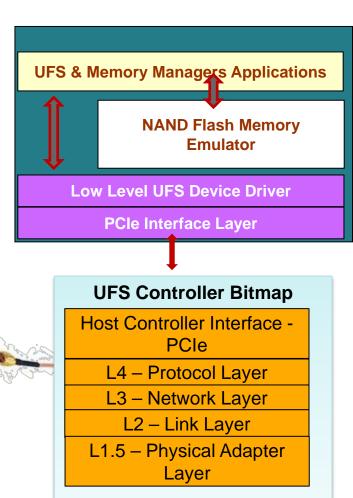

- FPGA based Development Platform productized into Validation Platform

- IP, software stacks and PHY come together

- Used by IP vendor (e.g., Arasan) for Interoperability testing with other pioneers

- Used by Test & Measurement vendors as target platforms

- For validation of protocol generators and analyzers

- Ultimately used by SoC/Device vendors as target or reference platforms for silicon validation

- Assured of IP interoperability, compliance, and backward compatibility

- New JEDEC storage standards continue to evolve for new markets

- Early IP/SoC validation enables compliance and compatibility for fast time-to-market

- Different SoC vendors at different stages of spec adoption

- Different spec revisions from different OEM's

- Backward compatibility and Interoperability a must among vendors

- IP vendors continue to

- Lead the pack in transforming specs to RTL and GDSII

- Keeping backward compatibility with older standards in new designs

- Enabling ecosystem-wide Inter-Op and compliance through

- Software stacks

- Hardware Validation Platforms

All items available before starting your SoC/Device designs !!

#### **THANK YOU**