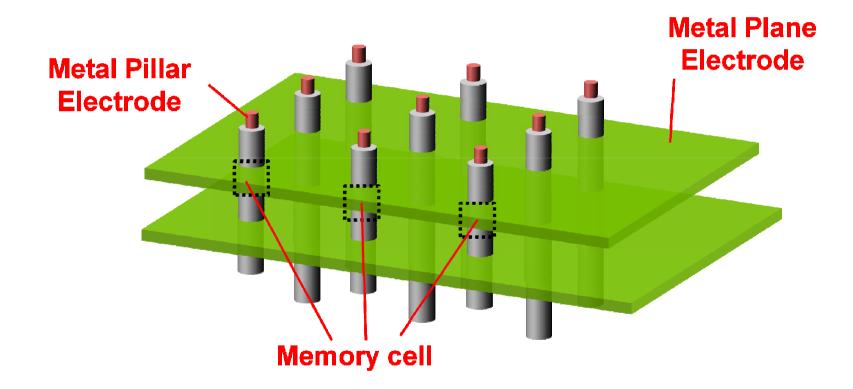

## **3D Vertical RRAM**

#### Henry (Hong-Yu) Chen, H.-S. Philip Wong <u>hongyuc@stanford.edu</u> Stanford University, CA, USA Collaborator: Peking University, China

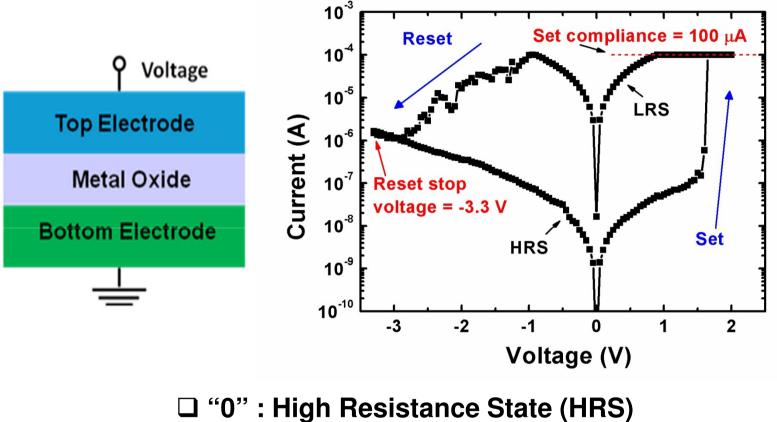

□ '1' : Low Resistance State (HRS)

□ '1'' : Low Resistance State (LRS)

□ HRS→LRS: SET

□ LRS→HRS: RESET

# Flash Memory Why 3D Architecture in RRAM?

## **RRAM has showed excellent single-cell performance.**

|                             | FLASH    | RRAM     |

|-----------------------------|----------|----------|

| cell area (F <sup>2</sup> ) | <4 if 3D | <4 if 3D |

| multi-bit                   | 3        | 3 2      |

| scalability                 | <20nm    | <10nm    |

| voltage                     | >20V     | <3V      |

| speed                       | ~10µs    | <10ns    |

| energy/bit                  | ~100pJ   | ~0.1pJ   |

| endurance                   | <1E5     | 1E6-1E12 |

| retention                   | >10years | >10years |

## A technology path toward 3D integration is needed in RRAM.

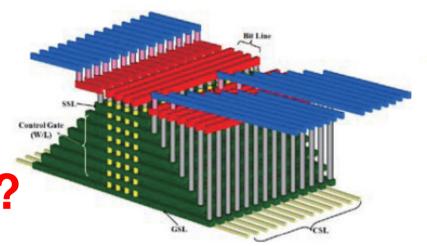

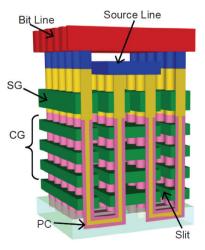

#### 3D NAND by Samsung, VLSIT, 2009

3D NAND by Toshiba , VLSIT, 2009

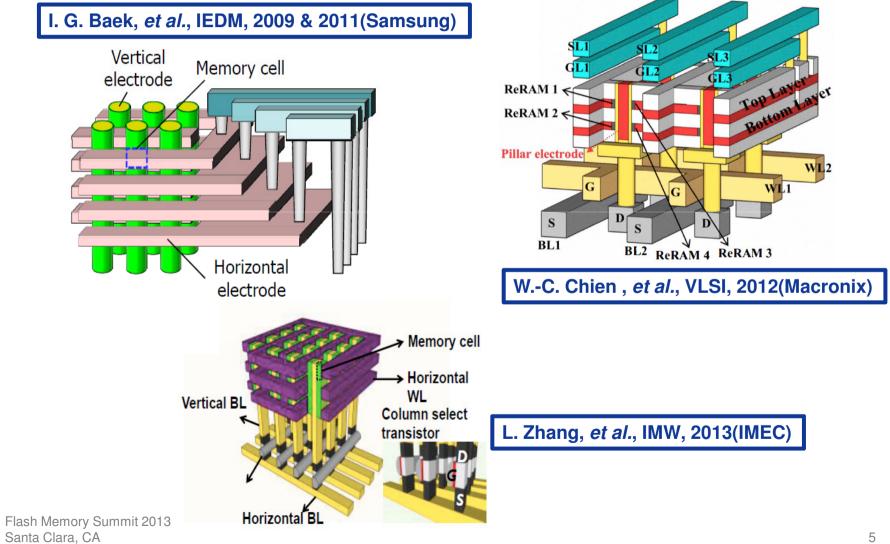

#### **Recent Advances in Demonstration**

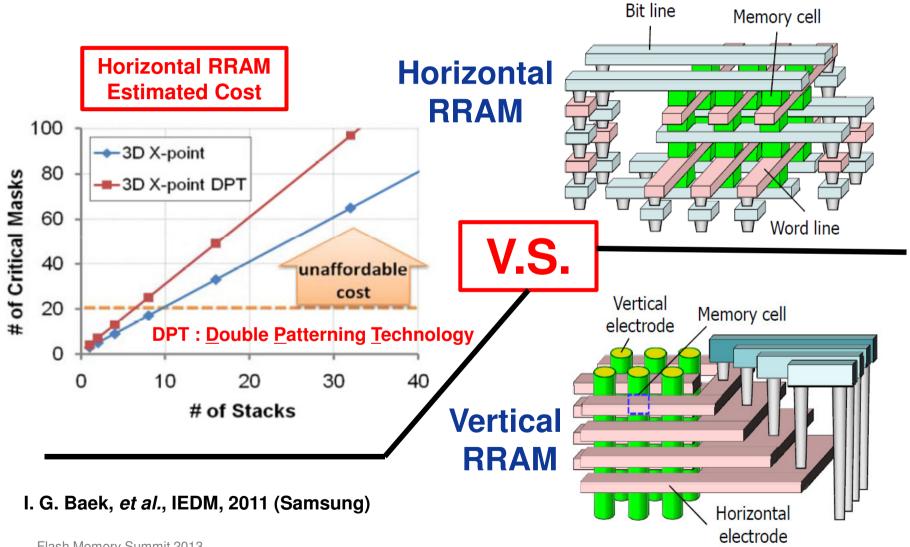

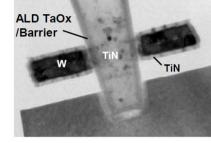

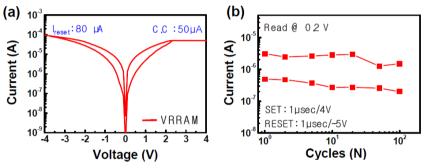

#### 1. Samsung [ I. G. Baek, et al., IEDM, 2011 ]

TiN/TaOx/barrier/TiN Size: 30nm in width Switching Voltage:~3/-4V Reset Current: ~80 μA Endurance: 100 Cycles

Memory

SUMMIT

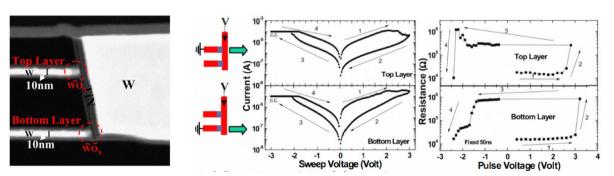

#### 2. Macronix [ W.-C. Chien , et al., VLSI, 2012 ]

W/WOx/SP-TiN/TiN Size: 10nmx100nm Speed: ~50ns Reset Current: ~200 µA Switching Voltage:~3/-2.5V Good read immunity Endurance: 600 Cycles(T) Endurance: 300 Cycles(B)

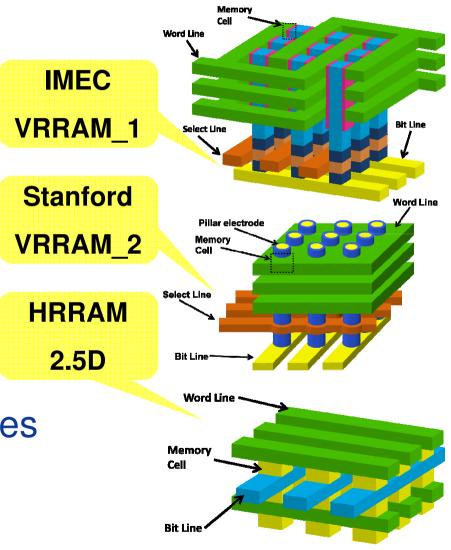

- 3D Vertical RRAM Demonstration

- Key Issues for 3D Memory Array

- Summary

#### <u>3D Vertical RRAM Demonstration</u>

- Key Issues for 3D Memory Array

- Summary

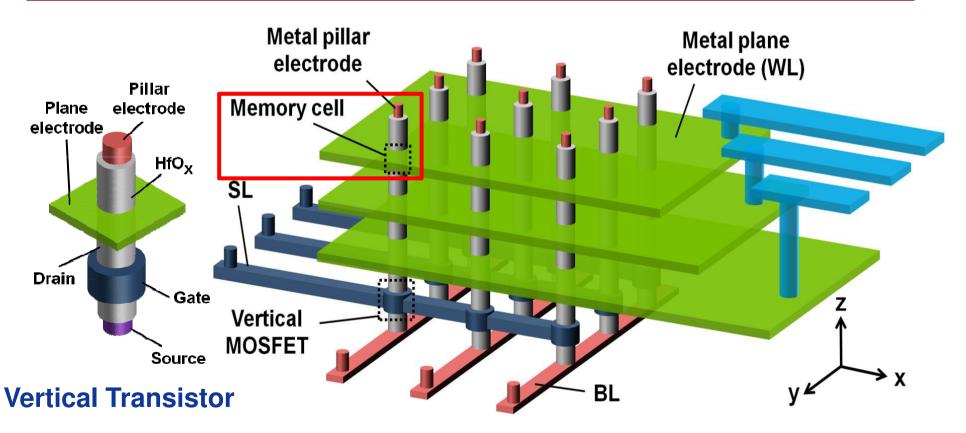

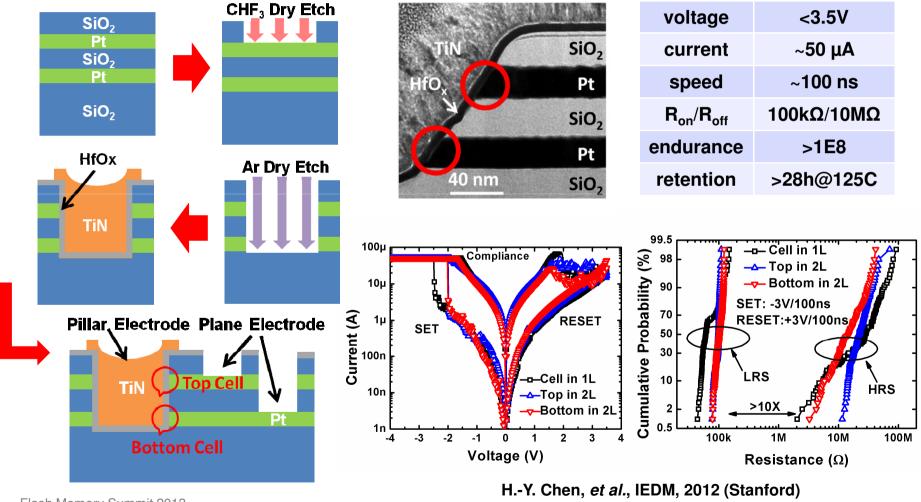

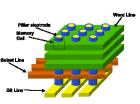

H.-Y. Chen, et al., IEDM, 2012 (Stanford)

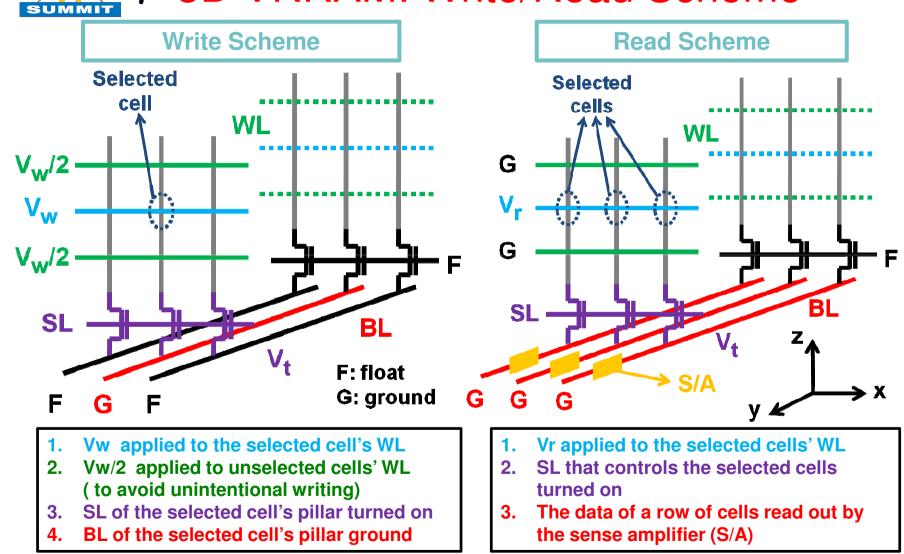

#### Each Vertical RRAM Cell is randomly accessible in the array!

H.-Y. Chen, et al., IEDM, 2012 (Stanford)

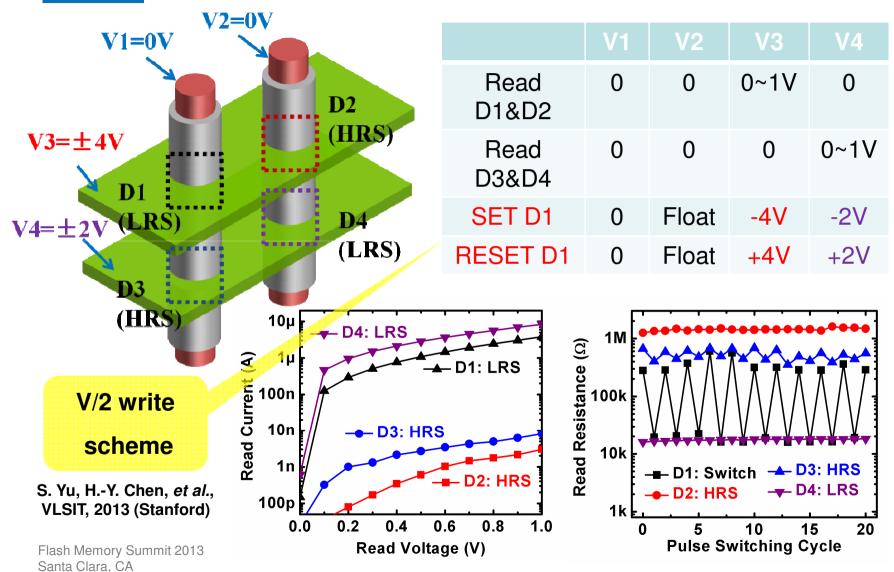

3D VRRAM: Write/Read Scheme

Flash Memory Summit 2013 Santa Clara, CA

Memory

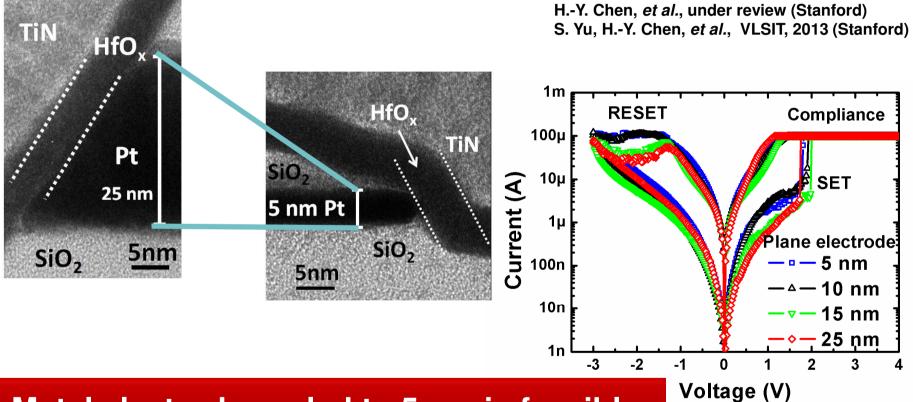

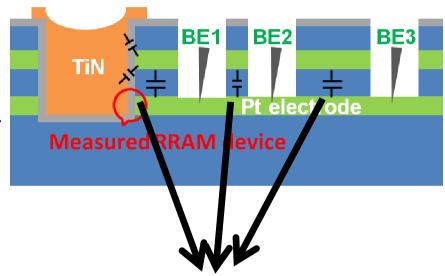

#### **Device Fabrication and Performance**

Flash Memory Summit 2013 Santa Clara, CA S. Yu, H.-Y. Chen, et al., VLSIT, 2013 (Stanford)

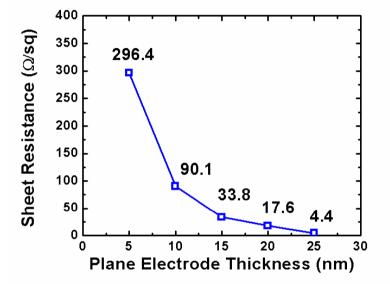

#### Metal electrode scaled to 5 nm is feasible. => Improve integration density

#### **Demonstration of Array Operation**

Memory

SUMMIT

- 3D Vertical RRAM Demonstration

- Key Issues for 3D Memory Array

- Summary

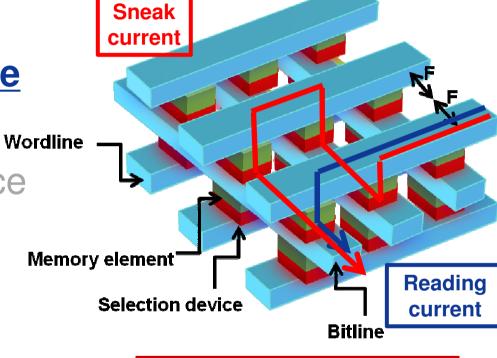

- Sneak path leakage

- Selection Device

- Parasitic capacitance

- Line resistance

- Plane resistance

- Interconnection

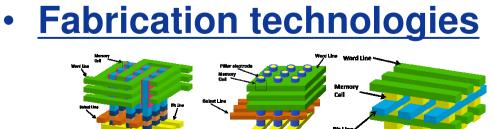

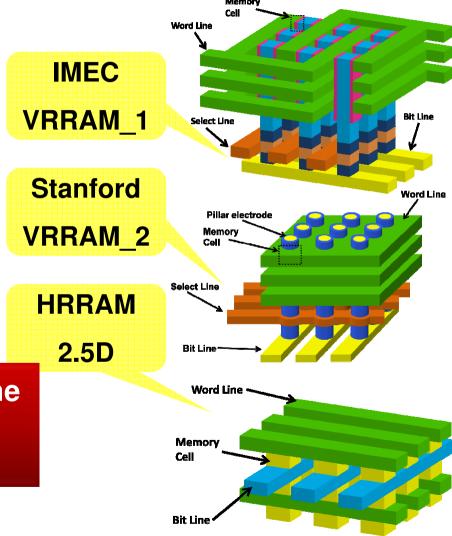

- Fabrication technologies

Memory

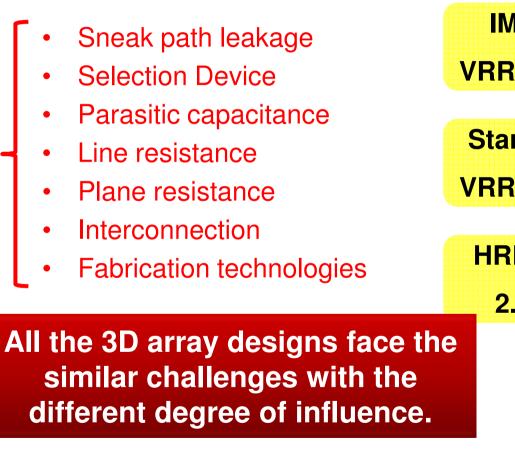

### Memory Challenges for 3D Memory Array

- Sneak path leakage

- Selection Device

Wor

- Parasitic capacitance

- Line resistance

- Plane resistance

- Interconnection

- Fabrication technologies

Sneak path causes read disturbance problem and increases the power consumption.

### Memory Challenges for 3D Memory Array

- Sneak path leakage

- Selection Device

- Parasitic capacitance

- Line resistance

- Plane resistance

- Interconnection

- Fabrication technologies

Sufficient on/off ratio requirement

High current density requirement Ex. (>10MA/cm<sup>2</sup>)

Polarity requirement

High endurance requirement

Scalability requirement

3D low temperature fabrication requirement...

- Sneak path leakage

- Selection Device

- Parasitic capacitance

- Line resistance

- Plane resistance

- Interconnection

- Fabrication technologies

Flash Memory Summit 2013 Santa Clara, CA

Parasitic capacitance causes RC delay.

- Sneak path leakage

- Selection Device

- Parasitic capacitance

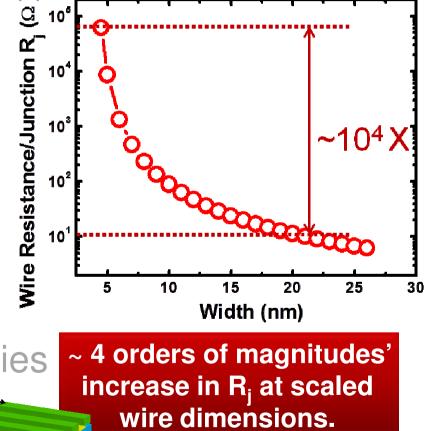

- Line resistance

- Plane resistance

- Interconnection

- Fabrication technologies

Flash Memory Summit 2013 Santa Clara, CA

Memory

J. Liang, et al. IMW 2012, p. 61.

- Sneak path leakage

- Selection Device

- Parasitic capacitance

- Line resistance

- Plane resistance

- Interconnection

- Fabrication technologies

Flash Memory Summit 2013 Santa Clara, CA

Memory

The thinner the electrode, the more resistive plane electrode =>Higher switching voltages

H.-Y. Chen, et al., under review (Stanford)

- Sneak path leakage

- Selection Device

- Parasitic capacitance

- Line resistance

- Plane resistance

- Interconnection

Fabrication technologies In

Werd Line Word L

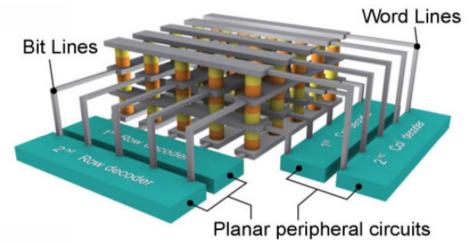

Flash Memory Summit 2013 Santa Clara, CA Complicated wire routing Increased circuit overhead

- Sneak path leakage

- Selection Device

- Parasitic capacitance

- Line resistance

- Plane resistance

- Interconnection

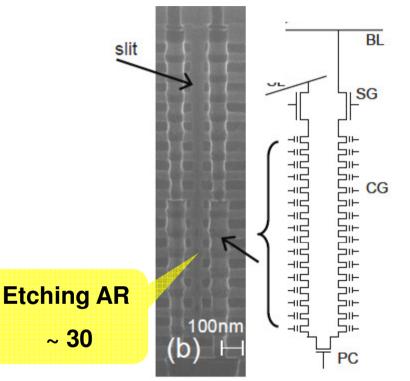

R. Katsumata, et al. VLSI 2009, p. 136.

#### Flash Memory Summit 2013 Santa Clara, CA

**sh** Memory

#### Etching capability CMOS-friendly material

Memory

SUMMIT

- 3D vertical RRAM cross-point array is promising for next generation mass storage due to the effective bit cost.

- A comprehensive understanding for the particular VRRAM array is reported in this talk:

- (1) memory architecture design

- (2) read/write schemes

- (3) device fabrication, scaling, and characterization

- (4) array operation demonstration

- Key issues for developing 3D memory array were discussed.

- Stanford Non-Volatile Memory Technology Research Initiative (NMTRI) member companies

- □ 973 Program (2011CBA00602), China

- Stanford Nanofabrication Facility (SNF), a member of the NSF-supported National Nanotechnology Infrastructure Network (NNIN)

- □ H.-Y. Chen is additionally supported by

- Intel Fellowship

- Taiwanese Government Scholarships to Study Abroad

- IEEE Electron Devices Society PhD Student Fellowship

- 3D vertical RRAM cross-point array is promising for next generation mass storage due to the effective bit cost.

- A comprehensive understanding for the particular VRRAM array is reported in this talk:

- (1) memory architecture design

- (2) read/write schemes

- (3) device fabrication, scaling, and characterization

- (4) array operation demonstration

- Key issues for developing 3D memory array were discussed.