Flash Memory Summit 2013 Plenary Session: Flash Below 20 nm: What is Coming and When

# Challenges in 3D NAND

### Gill Lee

Senior Director / Principal Member of Technical Staff Silicon Systems Group Applied Materials, Inc.

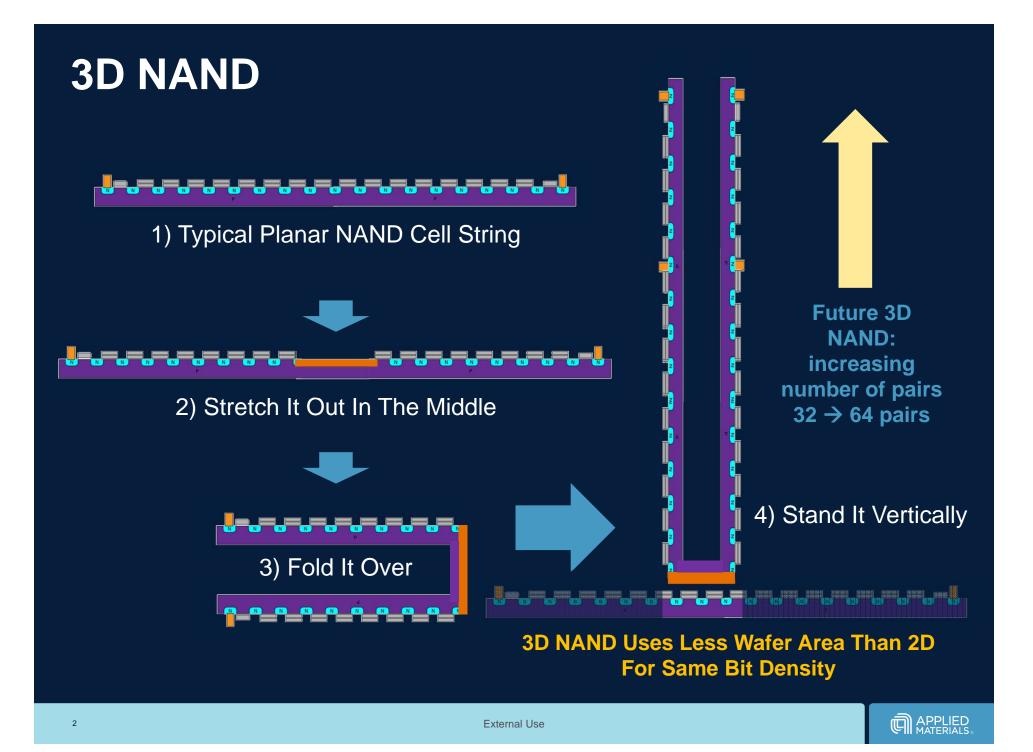

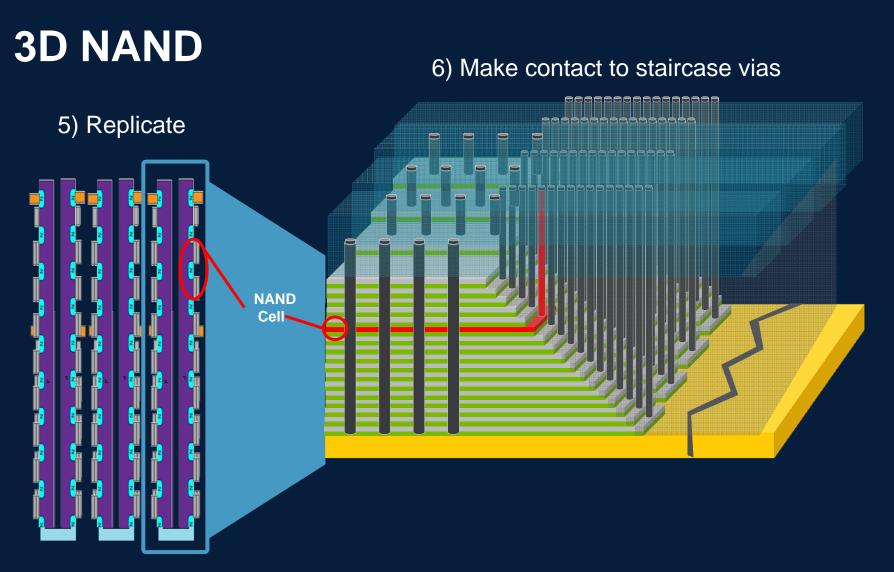

3D NAND does not require leading-edge lithography, but it will require new deposition and etch technologies.

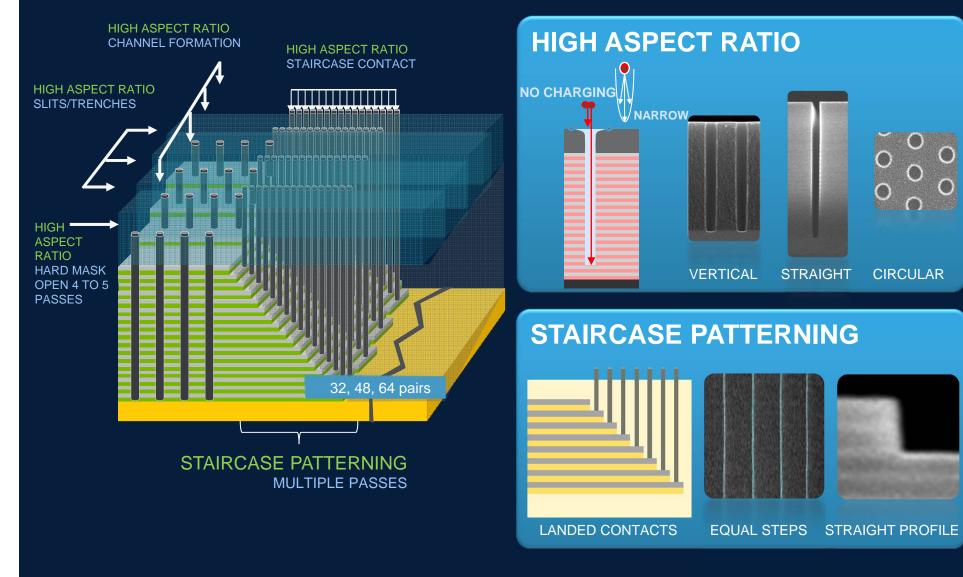

#### **3D NAND: Game Changer for Etch and Deposition PLANAR 3D NAND CD DEFINITION AND SCALING CD DEFINITION AND SCALING** (~50nm) (<15nm) Etch and Deposition Grows Lithography Lithography drops **ETCH ETCH** 2 Lower aspect ratios High aspect ratios Staircase patterning (trim and etch) Multi-patterning (SATP, SAQP) DEPOSITION **DEPOSITION** Single layer Multi-layer stacks 3 Thinner films Thick films (active and hardmask)

4

External Use

APPLIED MATERIALS

### **3D NAND: New Etch Applications**

5

CIRCULAR

## **3D NAND: New CVD Applications**

#### **Critical Hardmask**

Channel, Word Line, Metal Contact High Aspect Ratios up to 60:1

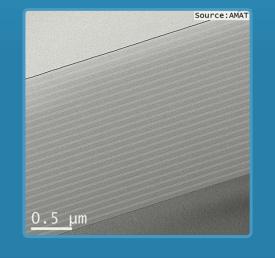

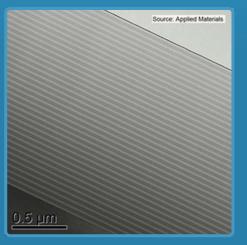

#### **Gate Stack**

Oxide/Nitride or Silicon

#### **CVD** Gapfill

Isolation and Interlayer Dielectrics

#### **Gate Stack Challenges:**

- Film Thickness determines Gate Length; Uniformity is Critical

- Manufacturing costs will pace adoption due to lower throughputs

#### **Gate Stack Solution:**

- Innovative Precision CVD Chamber Design with

- Uniform deposition with layer-to-layer precision

- > Superior repeatability with independent station control

- Higher Chamber throughput efficiency with lower operating cost

#### Sources: VLSI and IEDM

External Use