# Is Your Tester Ready for PCIe Gen 3.0?

A Signal Integrity Tutorial

Eric Kushnick, Advantest

- How to Measure Signal Integrity

- PCI-SIG Specifications

- Signal Integrity Factors

- Path Loss (Bandwidth)

- Reflections

- Crosstalk

- Conclusions

# Memory How to measure Signal Integrity

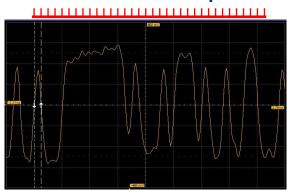

- Various measures of Signal Integrity

- Risetime

- Amplitude

- Jitter

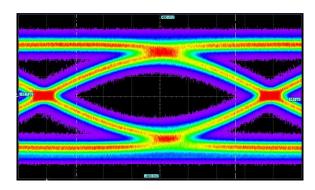

- The eye diagram encompasses all of the above.

- PCI-SIG specifies the eye diagram for PCIe

### **PCI-SIG Specifications**

- PCI-SIG determines the PCIe specifications

- PCI\_Express\_Base\_r3.0

- Gives component specifications.

- Volts and ps are at the chip package pins.

- PCI\_Express\_CEM\_r3\_0

- Card Electromechanical specification.

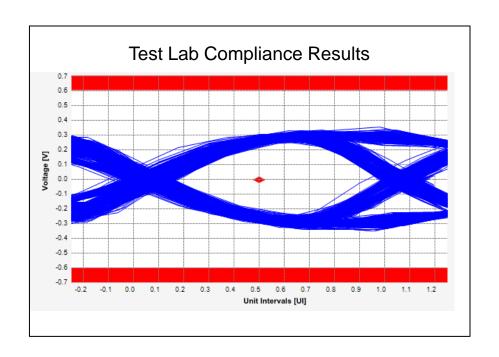

- Compliance eye diagrams must be met for both the addin card and a system board at the PCIe connector.

- Tester is a system board.

# Memory Signal Integrity Factors

- Tester signal integrity challenge

- Long signal paths compared to a motherboard

- Good signal integrity at the DUT requires control of:

- Path Loss (Bandwidth)

- Reflections

- Crosstalk

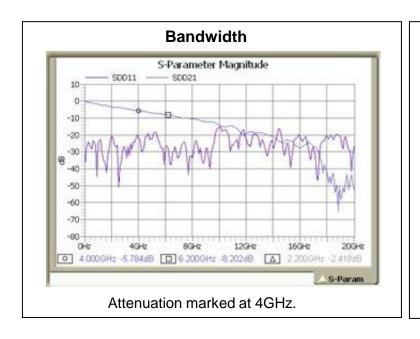

## Path Loss (Bandwidth)

- Path Loss (Bandwidth)

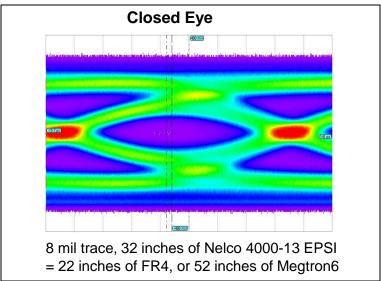

- Focus on losses at data rate / 2

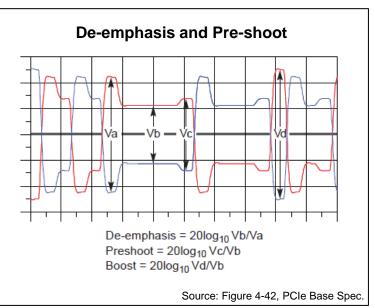

- De-emphasis, Pre-shoot, and Receive EQ make up for part of the signal loss.

## Path Loss (Bandwidth)

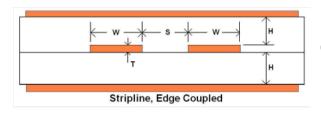

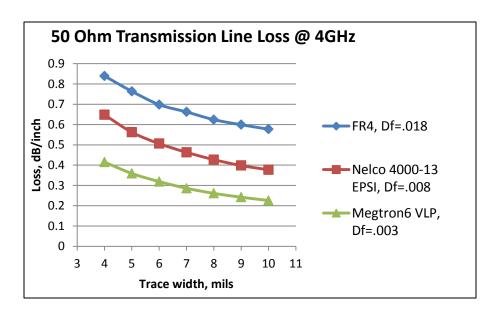

- PCB losses

- Trace width and surface roughness (ohmic loss)

- Dielectric loss (loss tangent, tan  $\delta$ , Df)

Geometric scaling produces equal impedance

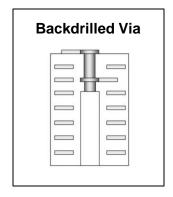

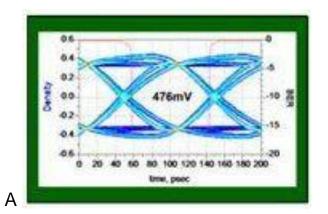

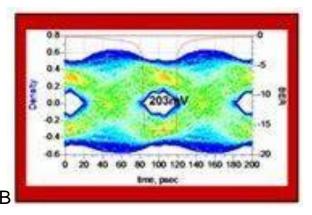

- Reflections occur at impedance discontinuities.

- Connectors

- Often capacitive. 85 ohms helps.

- Stubs

- Vias must be blind or backdrilled

Eye Diagrams of a 10Gbps signal, A) with backdrilled vias, and B) without backdrilling.

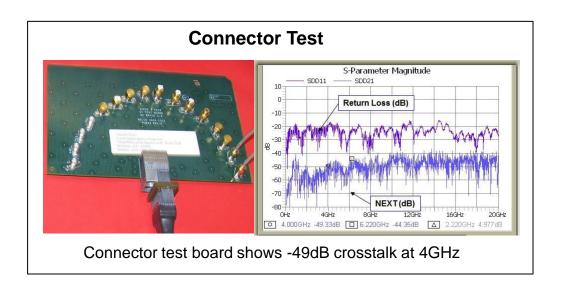

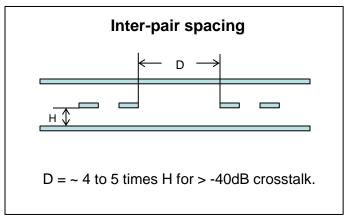

#### Crosstalk

- Connectors

- Separate Tx and Rx

- Ground shield or ground pins between signal rows

- PCB Traces

- Inter-differential pair distance

Careful design leads to good signal integrity results.

- [1] Bert Simonovich, "Bert's Practical Design Notes: An Overview of Vias", http://www.pcbdesign007.com/pages/columns.cgi?clmid=61&artid=82810

- [2] Bert Simonovich, "Bert's Practical Design Notes: The "Stubinator" vs. Back-Drilling",

- http://www.pcbdesign007.com/pages/columns.cgi?clmid=61&artid=83398