# Designing a Configurable NVM Express Controller/Subsystem

Amit Saxena, VP, Engineering

"The IP enabled solutions provider"

### **AGENDA**

**Company Overview**

**NVMe SSDC Subsystem**

NVMe Features & Configurability

**Configurable IP Components**

Summary

**NVMe SSDC Subsystem**

NVMe Features & Configurability

**Configurable IP Components**

#### **Summary**

### **The Mobiveil Team**

#### Leadership

- Management with 25+ years experience in Semiconductor/Silicon IP/Systems software

- Previously founded GDA Technologies, Inc and grew to strong IP and Services group, 500+ engineers strong.

#### **Key differentiators**

Developed several highly configurable key high speed IP blocks in the last 10+ years (PCI Express, Hyper Transport, Serial RapidIO, SPI4.2, DDR4/3,Flash Controllers etc)

#### Locations

Headquarters in Milpitas, CA India design centers: Chennai & Bangalore Sales: Offices/Reps worldwide

# **Mobiveil IP Advantages**

**NVMe SSDC Subsystem**

NVMe Feature & Configurability

**Configurable IP Components**

Market leading & most exhaustively proven cores in the market: Industry leaders are using these cores

**Consortium Participation**: RIO – Member, PCISIG – Member, HMC - Member

**Superior Technical Solution**: Most Feature rich IP, Complete Customization and delivery Solution

Support: Clear IP Focus & Worldwide Support

**3rd Party Partnerships for complete Solution:** (Verification and PHY IPs)

Standard Body Certified Cores: All Mobiveil IPs are validated and certified: PCI Plug fest, UNH, RTA

# **NVMe SSDC Subsystem**

## **NVMe SSDC Subsystem**

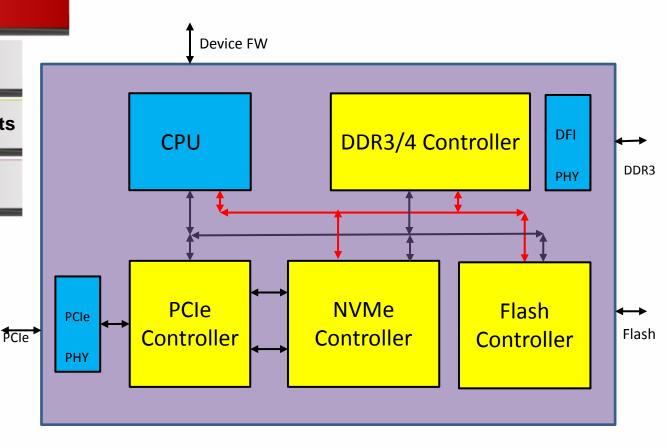

#### **NVMe SSDC Subsystem**

NVMe – Features & Configurability

**Configurable IP Components**

Summary

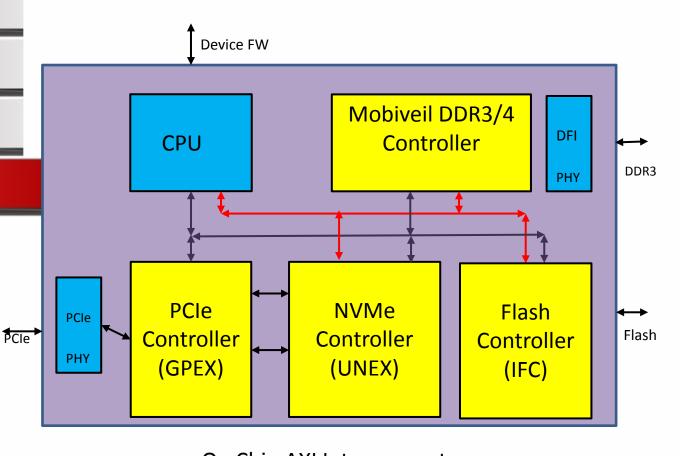

On Chip AXI Interconnect

On Chip APB Interconnect

Inter block AXI Interconnect

**NVMe SSDC Subsystem**

**NVMe - Features**

**Configurable IP Components**

**Summary**

### **NVMe - Features**

- A Register level interface that allows host software to communicate with a non-volatile memory subsystem

- Defines a standard command set for use with the NVM subsystem

- Optimized for Enterprise and Client solid state drives, typically

- attached to the PCI Express interface

- Defines Pair of Submission and Completion IO Queues

- Defines parallel operation by supporting up to 64K I/O Queues with up to 64K commands per I/O Queue.

- Defines many Enterprise capabilities like end-to-end data protection, enhanced error reporting, and virtualization

- Supports differentiated services, i.e., different qualities of service (QoS)Targets

- Supports Multi-Path IO and Namespace Sharing capabilities

- Supports Reservations

- Supports multiple name spaces

**NVMe SSDC Subsystem**

**NVMe Configurability**

**Configurable IP Components**

Summary

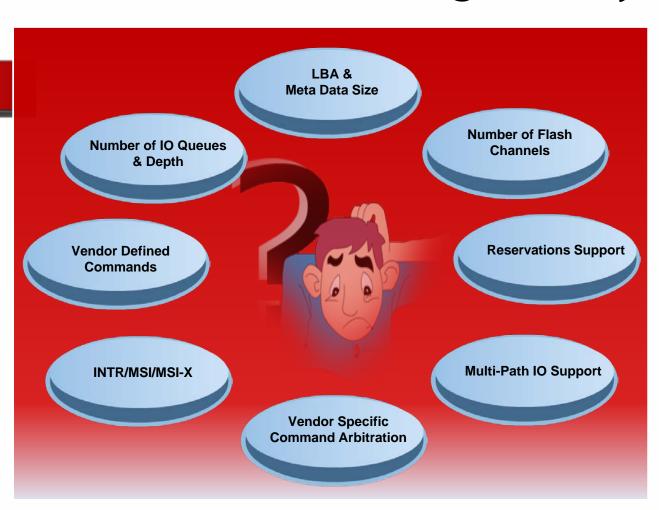

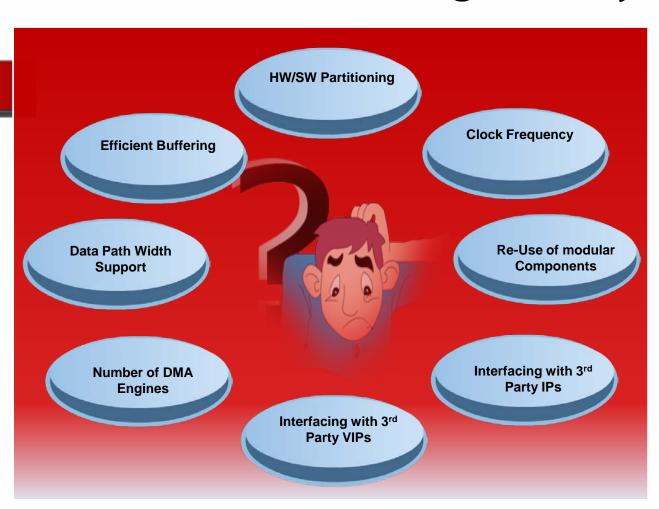

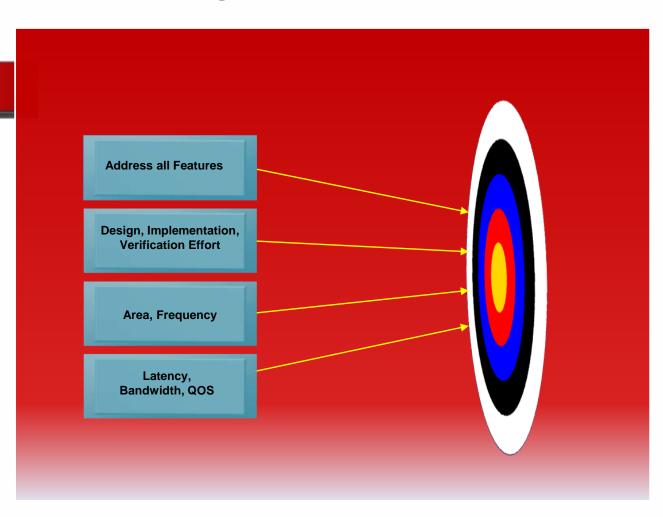

# **NVMe Configurability**

**NVMe SSDC Subsystem**

**NVMe Configurability**

**Configurable IP Components**

Summary

# **NVMe Configurability**

**NVMe SSDC Subsystem**

**NVMe Controller**

**Configurable IP Components**

**Summary**

## **Configurable NVMe Controller**

# Configurable IP Components

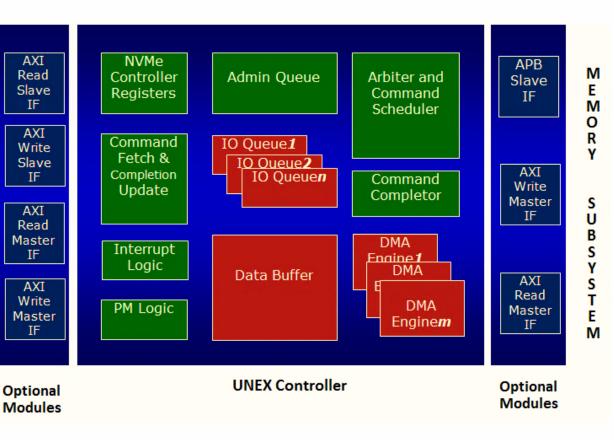

# **NVM Express Controller (UNEX)**

**NVMe SSDC Subsystem**

C

S

U

В

S

S

М

NVMe Features & Configurability

#### **UNEX**

#### **Summary**

- √ Highly Configurable

- ✓ Technology Independent

## **NVM Express (UNEX) Controller**

#### **NVMe SSDC Subsystem**

NVMe Features & Configurability

#### **UNEX**

#### **Summary**

- √ Highly Configurable

- ✓ Technology Independent

### **UNEX Features**

- Compliant to NVM Express 1.1 specification

- Supports configurable number of IO Queues

- Supports configurable Queue depth

- Supports Round Robin or Weighted Round Robin with Urgent Priority arbitration mechanism

- Host memory page size support of 128MB

- Efficient and Streamlined Command handling

- Supports Fused Operations

- Supports All Optional Admin Commands

- Supports All Optional NVM Commands

- Supports Multi-Path IO and Namespace Sharing capabilities

- Supports Reservations

- Supports multiple name spaces

- Optional AXI interfaces for NVMe implementation in SoC

- Well defined Command Interface for local CPU to perform subsystem initialization and to handle all non-hardware accelerated commands

- Targets FPGA, Structured ASIC and Standard Cell technologies

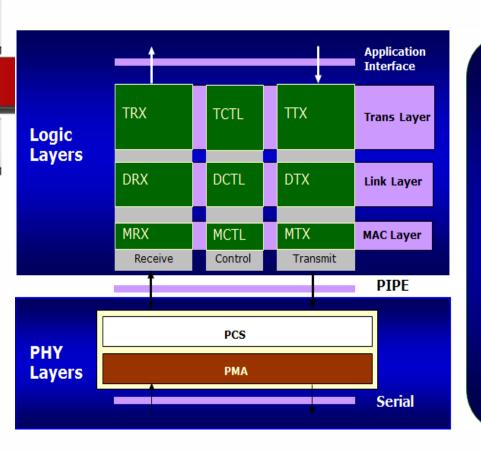

# PCI Express Controller (GPEX)

PCI Express (GPEX)

#### **Company Overview**

**NVMe SSDC Subsystem**

NVMe Features & Configurability

#### **GPEX**

#### **Summary**

- √ Highly Configurable

- ✓ Technology Independent

- ✓ System Validated

**NVMe SSDC Subsystem**

NVMe Features & Configurability

#### **GPEX**

#### **Summary**

- ✓ Highly Configurable

- ✓ Technology Independent

- ✓ System Validated

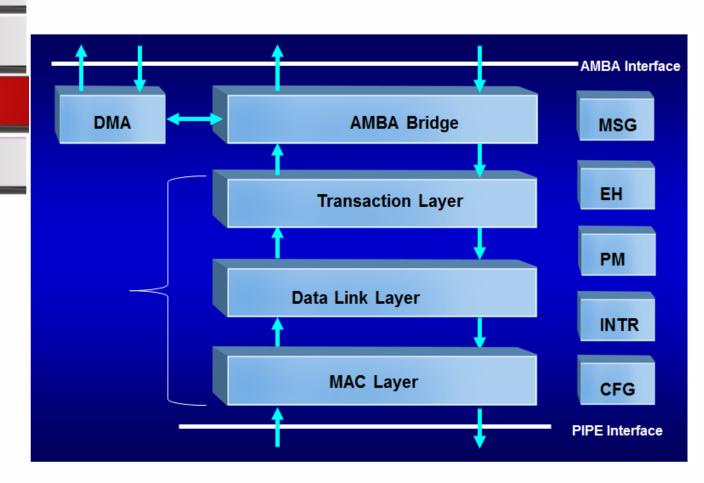

# PCIe-AMBA Bridge

# DDR3/4 Memory Controller

**NVMe SSDC Subsystem**

NVMe Features & Configurability

**DDR3/4 Controller**

#### **Summary**

- ✓ Highly Configurable

- ✓ Technology Independent

Silicon Proven

# DDR3/4 Memory Controller

#### **NVMe SSDC Subsystem**

NVMe Features & Configurability

**DDR3/4 Controller**

#### **Summary**

- √ Highly Configurable

- ✓ Technology Independent

Silicon Proven

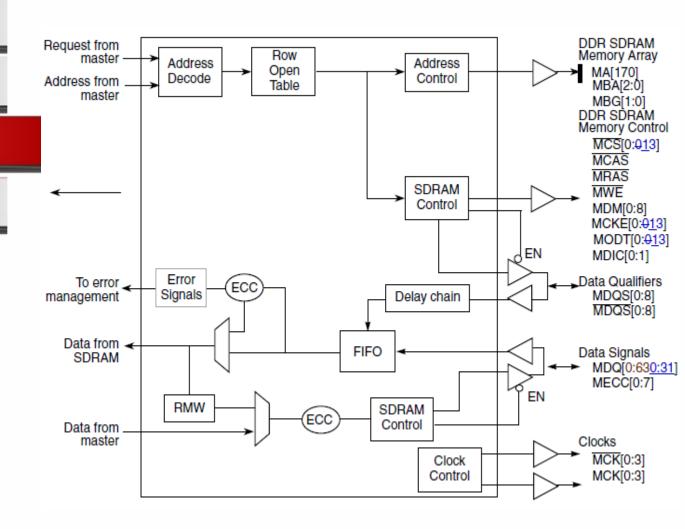

### DDR3/4 Controller Features

- Support for DDR3 and DDR4 SDRAM

- 64-/72-bit SDRAM data bus, 32-/40-bit SDRAM, 16-/24bit SDRAM

- Supports Chip select interleaving

- Supports Partial array self refresh

- Support for data mask signals and read-modify-write for sub-double-word writes

- Support for double-bit error detection and single-bit error correction ECC (8-bit check word across 64-bit data)

- Open page management (dedicated entry for each logical bank)

- Automatic DRAM initialization sequence or softwarecontrolled initialization sequence

- Write leveling supported for DDR3 memories

- Support for up to eight posted refreshes

# Integrated Flash Controller

**NVMe SSDC Subsystem**

NVMe Features & Configurability

**IFC**

#### **Summary**

- ✓ Highly Configurable

- ✓ Technology Independent

Silicon Proven

# Integrated Flash Controller

#### **NVMe SSDC Subsystem**

NVMe Features & Configurability

**IFC**

#### **Summary**

- √ Highly Configurable

- ✓ Technology Independent

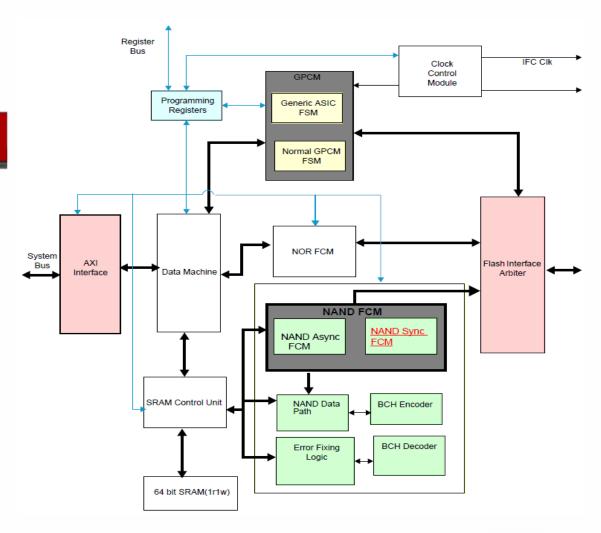

# Integrated Flash Controller Features

- Flash Controller with eight chip selects

- AXI V1.0 Slave Interface

- Separate Bus Interface for register access

- Support for error and debug registers

- Supports NAND, NOR and GPCM (SRAM and ROM) devices

- Support memory banks of size 64KByte to 4 GBytes

- Write protection capability (only for NAND and NOR)

- Provision of Software Reset

- NAND Flash Features

- x8/ x16 NAND Flash Interface

- Support for ONFI-2.2 Asynchronous interface (8/16 Bit)/Source

Synchronous interface (8 bit) and mandatory commands.

- BCH code for 4 bit & 8 bit Error correction per sector of 512 bytes (Using GF-2^13 Galois field) and 24 & 40 bit ECC per sector of 1K bytes (Using GF- 2^14 Galois field)

- Optional ECC generation and checking

- Flexible timing control to allow interfacing with proprietary NAND devices

- SLC and MLC Flash devices support with configurable page sizes of up to 8KB

# Mobiveil NVMe SSDC Subsystem

**NVMe SSDC Subsystem**

NVMe Features & Configurability

**IFC**

#### **Summary**

On Chip AXI Interconnect

On Chip APB Interconnect

Inter block AXI Interconnect

INDIA: EMM YES PARK, 3rd Floor, #69 (Old #137), Jawaharlal Nehru Road, Ekkattuthangal, Chennai 600032, Ph: +91-44-4208 6803, +91-44-4208 6804

2984, 2nd Floor, 12th Main Road, HAL 2nd Stage, Indira Nagar, Bangalore 560008, Ph: +91-80-42087666