# Device-Level Security Implementation to SSD by Controller (Hiroshi Watanabe)

Hiroshi Watanabe National Chiao Tung University

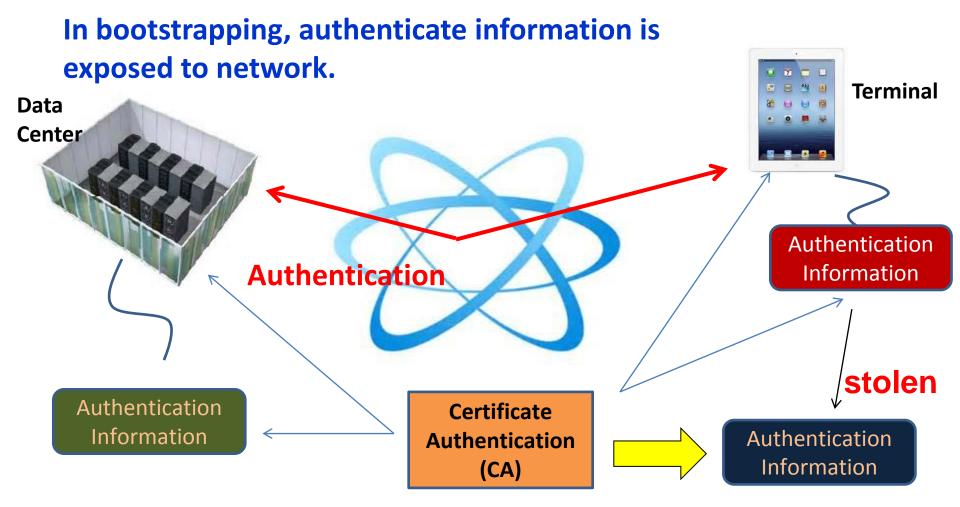

### Who will manage CA?

Flash Memory Summit 2014 Santa Clara, CA

Not distinguish

Santa Clara, CA

# Why will Device-level Security be demanded?

## Memory Security Classification

- Memory chip is a smallest unit connected in network.

- 2. How many memory chips are used all over the world?

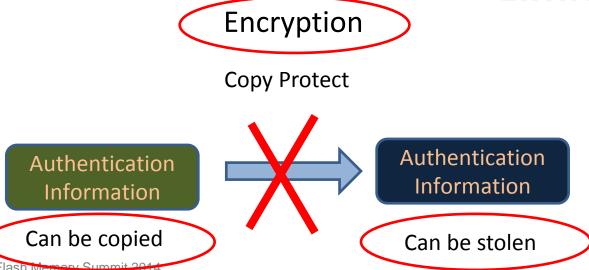

Software Base Central Encryption

**Device Level**

#### Cell Array

#### **Enhanced RDF**

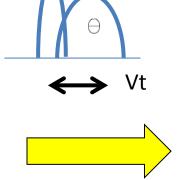

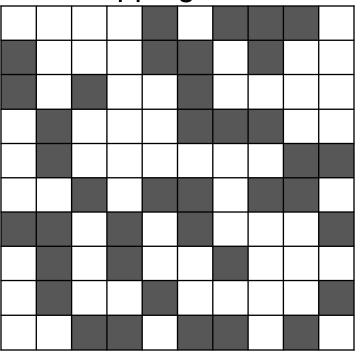

# Vt fluctuation mapping

### **RDF** = Random Dopant Fluctuation

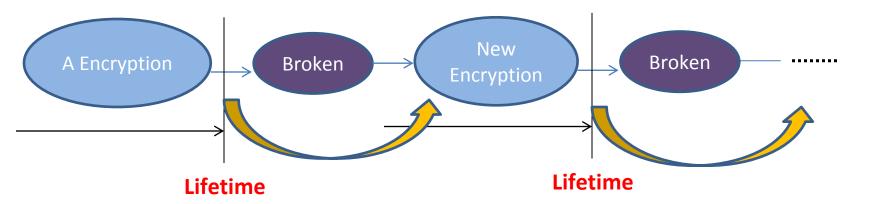

#### Lifetime Controller

- 1. CMOS Compatible

- 2. Can be embedded to memory controller

- 3. Demonstrated as Integrated <u>Battery-Less</u> Electronic Timer in experiment

H. Watanabe, et al., IEEE TED vol. 58, No. 3, 792 (2011)