# RRAM Opportunity for High density memory application

6. Aug. 2014SuOck ChungSK hynix R&D Div.

## ICT tech trends

### **Emerging devices**

- . Wearable

- . Automotive

- . Mobile health-care

. IoT

Cloud

Big data

Virtualize

Network

### **New computing system**

- . Exascale

- . Multi-cores

- . New memory technology

- Byte accessibility

- Capacity?

- Latency?

- Bandwidth / power ?

- Endurance?

- → SCM

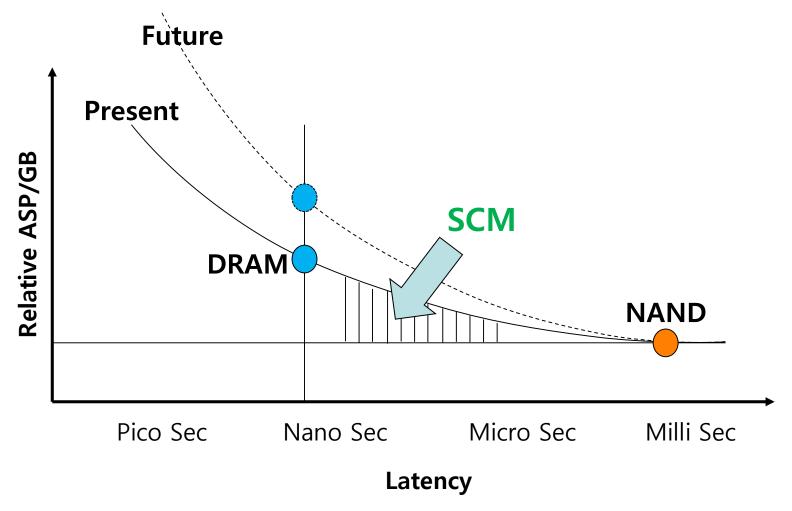

## Flash Memory Gap b/w DRAM ~ NAND

## **RRAM Potentials**

| ←Low Risk high→    | DRAM | NAND | PRAM<br>(SLC) | STTRAM | RRAM<br>(TMO) | RRAM<br>(CBRAM) |

|--------------------|------|------|---------------|--------|---------------|-----------------|

| Byte-Accessible    |      | •    |               |        |               |                 |

| Write Latency      | •    | •    | •             | •      | •             | •               |

| Write Bandwidth    | •    | •    |               | •      |               |                 |

| Endurance          | •    | •    |               | •      |               |                 |

| Data Retention     | •    |      | •             | •      | •             |                 |

| Power / Bandwidth  |      | •    | 0             | •      |               |                 |

| 3D Solution        | •    | •    |               | •      | •             | •               |

| Bit Density (Cost) | 0    | •    | 0             | •      |               |                 |

| Manufacturability  | •    | •    | 0             | •      |               | 0               |

#### Requirements for SCM

- Non-volatile, byte accessible

- High capacity + Short latency + Wide B/W @ moderate power

#### ReRAM is a good candidate

- Smaller power consumption than PRAM (I\_reset < 1/3)</li>

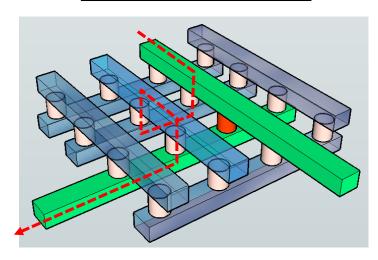

- Cross Point Array (XPA) + Multi-Level Stacking (MLS)

## Major challenges

#### **Sneak current effect**

- Selected cell → Sneak path

- Originated from imperfect off

- Large operation power,

Sensing noise issue

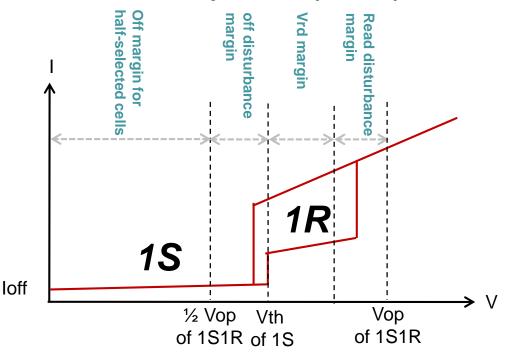

- Non-linear 1R → 1S1R Lower the loff of 1S

#### 2 Terminal Operation (1S+1R)

- Simple process merit

- Narrow data window

- → Good match of 1R+1S I-V

- → Higher Vop ?

- Recent ICT tech trend requires SCM type memory (high capacity + shorter latency + smaller power). RRAM is an attractive candidate for SCM.

- SK hynix has explored and developed core technologies (especially, cell and array architecture) for RRAM production.

- Stackable selector's I\_off and cell data window are key success factors for high density RRAM product.