# Understanding the Impact of Threshold Voltage on Flash Reliability and Performance

Wei Wang<sup>1</sup>, Tao Xie<sup>2</sup>, Deng Zhou<sup>1</sup>

<sup>1</sup>Computational Science Research Center, San Diego State University <sup>2</sup>Computer Science Department, San Diego State University

28th ACM International Conference on Supercomputing

#### **Outline**

- Background and model analysis

- Threshold voltage reliability model

- Testing methodology

- Experimental results

- Model establishment

- A case study: threshold voltage reduction

Summary

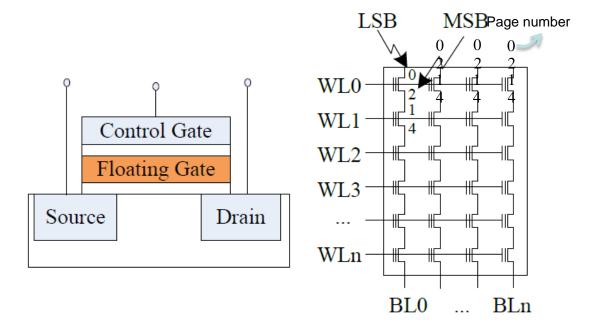

#### NAND Flash

NAND flash based solid state drives (SSDs) have been largely adopted in supercomputing centers.

(a) Flash memory cell and block structure

(b) Flash memory

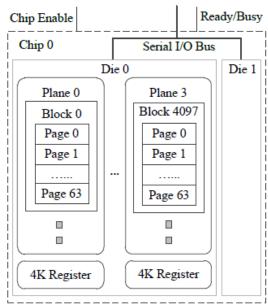

#### **MLC Flash**

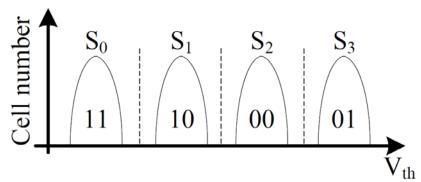

Flash memory uses threshold voltages to represent data information

- Each memory cell can store 2 bits data

- A narrowed threshold voltage range

- A shrunk memory cell size

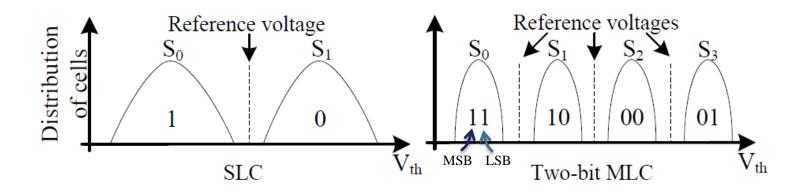

## Threshold Voltages

What is the impact of threshold voltages on flash performance and reliability?

ISPP is a standard cell programming process

$$V_{th} = V_{start} + \beta \Delta V_{pp} N_s$$

$N_s$  represent the number of programming steps;  $\beta$  is a material related coefficient.

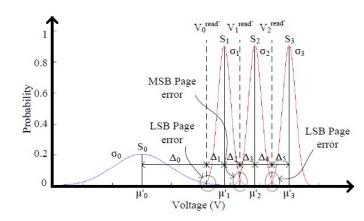

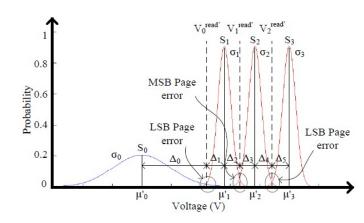

#### Memory Threshold Voltage Distribution

- Cells are not identical

- Threshold voltages of cells programmed to the same state are different among cells

Probability density function (Gaussian)

$$f(x) = \sum_{s=0}^{2^{M}-1} P(S_s) \frac{1}{\sqrt{2\pi}\delta_s} \exp\{\frac{-(x-\mu_s)^2}{2\delta_s^2}\}$$

•  $P(S_s)$  is the probability of being state  $S_s$ . In a 2-bit MLC  $P(S_s) = \frac{1}{4}$ .

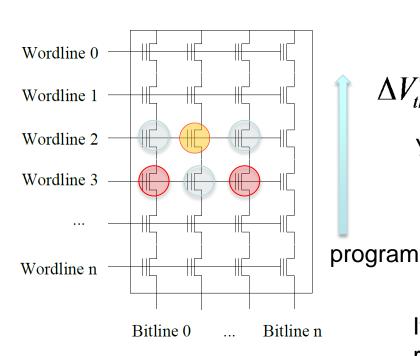

#### Cell-to-cell Interference

$$\Delta V_{th}^{(p,q)} = \gamma_{fg1} \Delta V_{th}^{(p,q+1)} + \gamma_{fg2} (\Delta V_{th}^{(p-1,q)} + \Delta V_{th}^{(p+1,q)})$$

$Y_{fg1}$  and  $Y_{fg2}$  are the floating gate coupling ratios.

$$\Delta V_{th}^{(p,q)} = (\gamma_{fg1} + 2\gamma_{fg2}) \Delta V_{th}^{\text{max}}$$

If the maximum threshold voltage difference is reduced, the floating gate coupling effect is reduced.

## Threshold Voltage Reliability Model

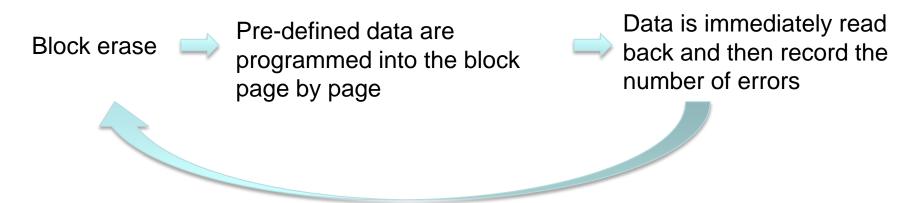

## **Testing Methodology**

####

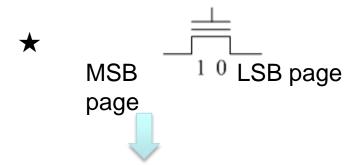

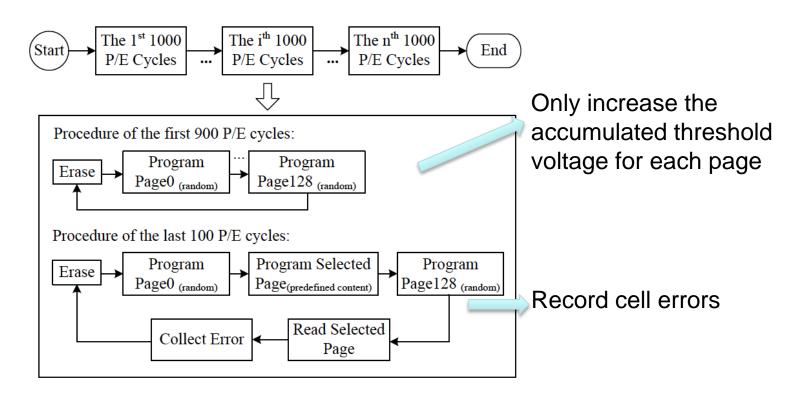

- ★ The threshold voltage of each state in a flash memory is fixed by its internal logic.

- ★ Each state (i.e., data pattern) represents a particular threshold voltage level.

• We can control threshold voltage of a memory cell by programming different data patterns to it.

★ The number of bit errors per page

O The number of errors per cell: Any bit flip in a 2-bit cell is recorded as a cell error.

Cell errors are collected during every P/E (program/erase) cycle

Pre-defined data eliminate the cell-to-cell interference that exists in real applications

#### A revised P/E scheme

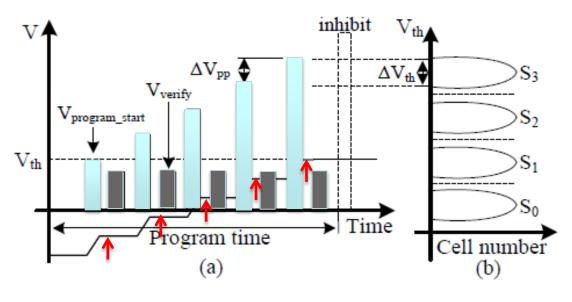

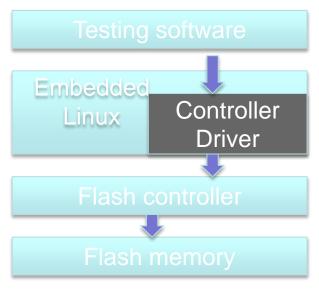

#### Hardware Platform

- Xilinx Xupv5-Lx110t evaluation board

- Ming II flash daughter board

#### Software Stack

- Flash controller on FPGA, no ECC;

- Embedded Linux, 3.0 kernel version;

- A driver for controller;

- Testing software preforms the P/E scheme and count errors.

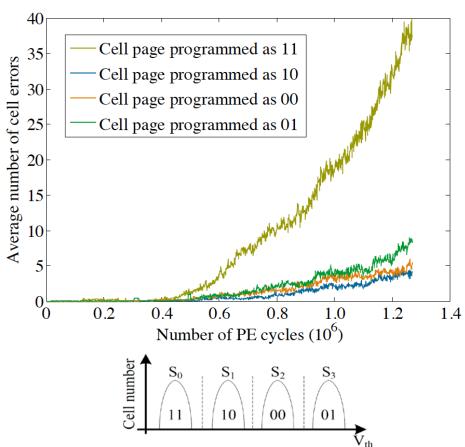

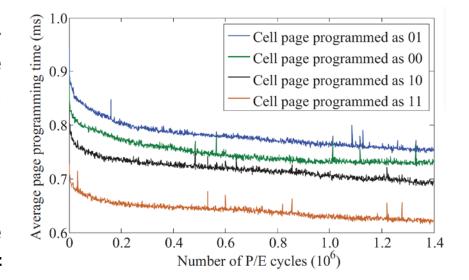

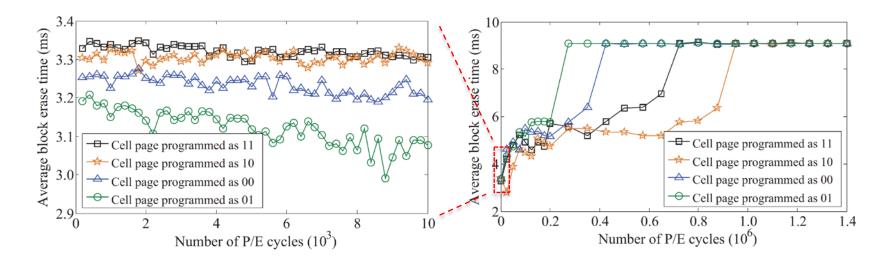

## Experimental Results (1/2)

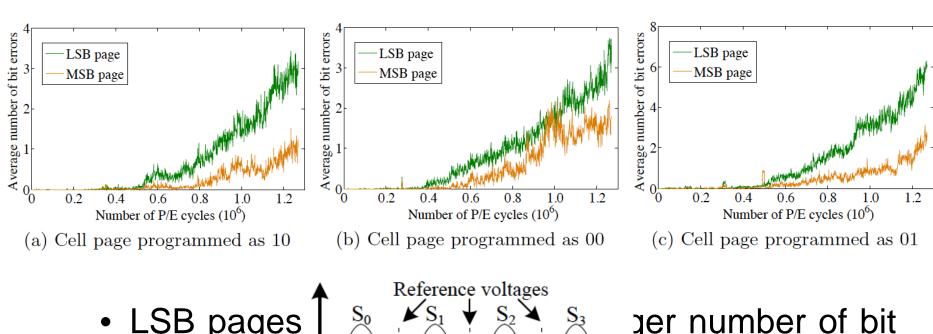

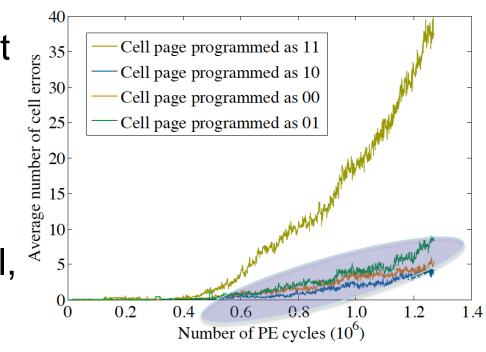

#### Average number of cell errors in four cell pages

- (1) The number of cell errors increases as the P/E cycles enlarge;

- (2) The cell page programmed exhibits the most unreliable characteristic;

- (3) Cell pages programmed to a higher voltage incur more the P/E errors as cycles enlarge;

## Experimental Results (2/2)

Number of errors in LSB and MSB pages

• LSB pages errors than programmir Two-bit MLC

ger number of bit ages under all

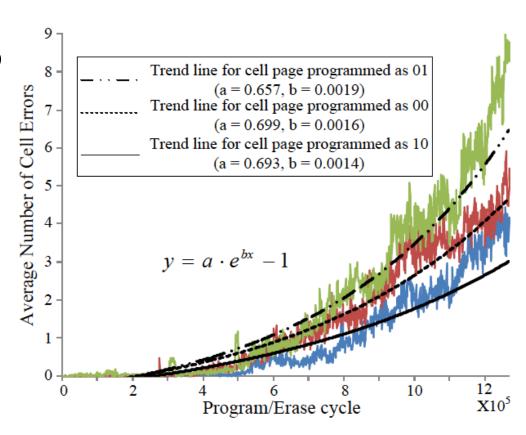

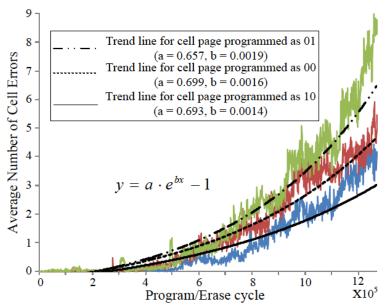

## Model Establishment (1/4)

- Consider the three programming states

- Use the nonlinear least square fitting method

Compared the exponential-law model, degree 2, 3, and 4 polynomial model

## emory Model Establishment (2/4)

Model errors (mean square deviation) comparison

| Cell page | Exponential-<br>law | Degree 2<br>polynomial | Degree 3<br>polynomial | Degree 4<br>polynomial |

|-----------|---------------------|------------------------|------------------------|------------------------|

| '10'      | 14.619              | 16.784                 | 20.276                 | 215.551                |

| '00'      | 9.628               | 14.482                 | 16.646                 | 74.392                 |

| '01'      | 8.442               | 7.934                  | 13.436                 | 15.571                 |

## Model Establishment (3/4)

- Parameter fitting

- Find a set of a and b

- As each pair of a and b represent a state (i.e., V<sub>th</sub>)

$$a = -5E^{-4} \ln(V_{th}) + 0.0019$$

$$b = 0.036 \ln(V_{th}) + 0.6616$$

#### Model Establishment (4/4)

$$Err = (-5E^{-4}\ln(V_{th}) + 0.0019)e^{(0.036\ln(V_{th}) + 0.6616)N} - 1$$

**General Form:**

$$Err = (\alpha_1 \ln(V_{th}) + \beta_1)e^{(\alpha_2 \ln(V_{th}) + \beta_2)N} - 1$$

The  $\alpha_1$ ,  $\beta_1$ ,  $\alpha_2$ , and  $\beta_2$  are determined by the characteristics of a flash memory

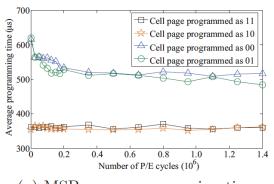

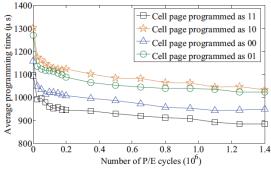

## Page Programming (1/2)

- Pages programmed to a lower threshold voltage have a better programming performance.

- The programming time decreases as the number of P/E cycles increases.

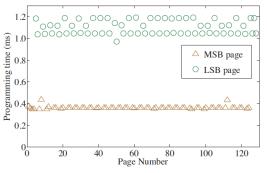

## Page Programming (2/2)

(b) LSB page programming time

(c) Page programming time in a block

- Programming speed of an MSB page is much faster than that of an LSB page.

- Programming time of MSB pages that are programmed as '00' and '01' is 1.42 times longer than that of MSB pages programmed as '11' and '10'.

- MSB pages have almost the same programming time, whereas the programming time of LSB pages varies substantially.

#### **Block Erase**

- In flash's early lifetime, blocks programmed to a higher threshold voltage have a shorter erase time.

- The erase time increases to 9 *ms* when flash comes to the end of its lifetime.

# A Case Study: Threshold Voltage Reduction

## A Case Study

- The value of threshold voltage influences flash reliability and performance.

- Why not reducing the threshold voltages of each state in an MLC flash memory?

- We propose the Threshold Voltage Reduction (TVR) approach by reducing the margin between two adjacent states.

- Performance and reliability

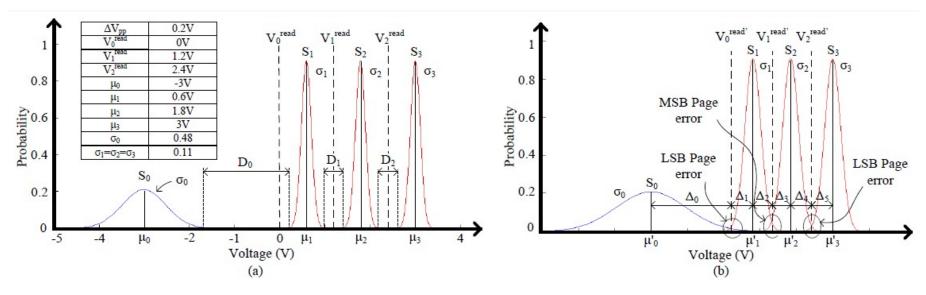

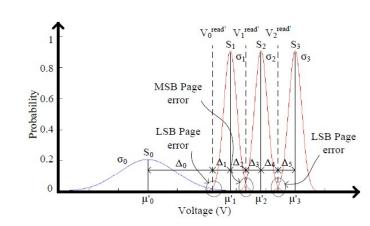

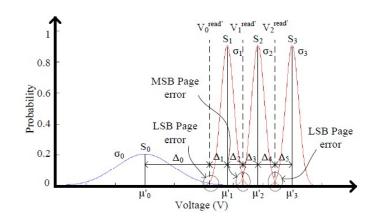

#### Threshold Voltage Reduction

(a) A normal V<sub>th</sub> distribution.

(b) A TVR applied V<sub>th</sub> distribution.

(b) Shows an extreme case that the width of all the three margins are shrunk to zero. (retention free)

#### TVR Analysis(1/3)

The probability that the voltages of cells cross the read reference voltage can be calculated by the tail probability function.

$$RBER_{MSBpage} = \frac{1}{4}Q_{1}\left(\frac{\left|\Delta_{2}\right|}{\delta_{1}}\right) + \frac{1}{4}Q_{2}\left(\frac{\left|\Delta_{3}\right|}{\delta_{2}}\right)$$

$$RBER_{LSBpage} = \frac{1}{4}Q_{0}\left(\frac{\left|\Delta_{0}\right|}{\delta_{0}}\right) + \frac{1}{4}Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) + \frac{1}{4}Q_{2}\left(\frac{\left|\Delta_{4}\right|}{\delta_{2}}\right) + \frac{1}{4}Q_{3}\left(\frac{\left|\Delta_{5}\right|}{\delta_{3}}\right)$$

$Q_s(x)$  is the tail probability function of each state.

#### TVR Analysis(2/3)

To simplify the computation, we assume that a forward state change and a backward state change have the same probability.

$$Q_{1}\left(\frac{\left|\Delta_{2}\right|}{\delta_{1}}\right) = Q_{2}\left(\frac{\left|\Delta_{3}\right|}{\delta_{2}}\right)$$

$$Q_{0}\left(\frac{\left|\Delta_{0}\right|}{\delta_{0}}\right) = Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{2}\left(\frac{\left|\Delta_{4}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{5}\right|}{\delta_{3}}\right)$$

$$Q_{0}\left(\frac{\left|\Delta_{1}\right|}{\delta_{0}}\right) = Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{5}\right|}{\delta_{3}}\right)$$

$$Q_{0}\left(\frac{\left|\Delta_{1}\right|}{\delta_{0}}\right) = Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{5}\right|}{\delta_{3}}\right)$$

$$Q_{0}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

$$Q_{0}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

$$Q_{0}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

$$Q_{0}\left(\frac{\left|\Delta_{1}\right|}{\delta_{1}}\right) = Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right)$$

$$Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

$$Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

$$Q_{1}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{2}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

$$Q_{2}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

$$Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right) = Q_{3}\left(\frac{\left|\Delta_{1}\right|}{\delta_{3}}\right)$$

## TVR Analysis(3/3)

For modern flash memory, RBER must be lower than 4.5E-4 (industry standard).

$$\Delta_0 \approx 1.40; \Delta_1 = \Delta_4 = \Delta_5 \approx 0.36; \Delta_2 = \Delta_3 \approx 0.34$$

The maximum threshold voltage that can be reduced is determined.

## Flash Memorp rogramming Speed Improvement

Programming speed is determined by ISPP

$$V_{th} = V_{start} + \beta \Delta V_{pp} N_{s}$$

$$\lceil N_{s} \rceil = \frac{\Delta V_{th}}{\beta \Delta V_{pp}}$$

19 steps → 9.5 steps

Programming speed is improved by 50% on average.

#### Reliability Improvement

Threshold voltage reliability model

$$Err = (-5E^{-4}\ln(V_{th}) + 0.0019)e^{(0.036\ln(V_{th}) + 0.6616)N} - 1$$

RBER is lower than 4.5E-4

12.46E5 → 13.35E5 P/E cycles Reliability is improved by 7.1%.

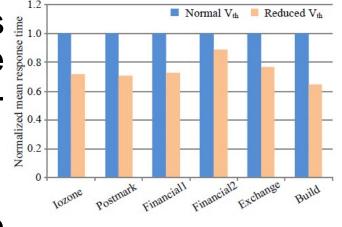

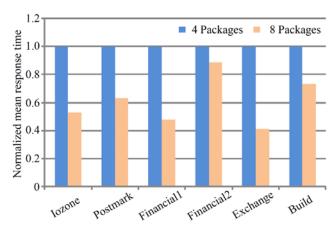

#### Impact on SSDs (1/2)

- DiskSim 4.0 and Microsoft SSD module

- Real-world traces (Financial 1, Financial 2, lozone, and postmark)

|      |    | Blocks per<br>Plane |   | Dies per<br>package |            |

|------|----|---------------------|---|---------------------|------------|

| 4 KB | 64 | 2,048               | 4 | 2                   | 4 - (4, 8) |

| Block erase (µs) | Program (µs)     | Read (µs) |

|------------------|------------------|-----------|

| 2,000            | 200 – (100, 200) | 20        |

## Impact on SSDs (2/2)

TVR can reduce SSD's overall mean response time by 11% to 35% (in a 4- by 11% to 35% (in a 4- channel example).

When we increase the package parallelism from 4 to 8, the overall mean response time consistently decreases (in exchange the improvement is 59%).

#### Summary

- The threshold voltage in MLC plays a very important role in both flash performance and reliability.

- An empirical threshold voltage reliability model is established based on experimental results.

A TVR approach that can improve flash performance and reliability is proposed.

#### **Future Work**

Consider the data retention requirement and improve the TVR approach.

Reducing the average programming voltage level by transforming high threshold voltage data patterns into low threshold voltage date patterns.

#### Acknowledgements

- We thank Steven Swanson and his Non-volatile Systems Laboratory for their support on the hardware platform.

- We thank the anonymous reviewers for their constructive comments that improve this paper.

This work was supported in part by the U.S. National Science Foundation under grant CNS (CAREER)-0845105.

## Questions?