## Spin Transfer Technologies An Allied Minds Company

### Orthogonal Spin Transfer (OST) A Better Approach

Flash Memory Summit August 2014

## **Company Background**

$\triangleright$

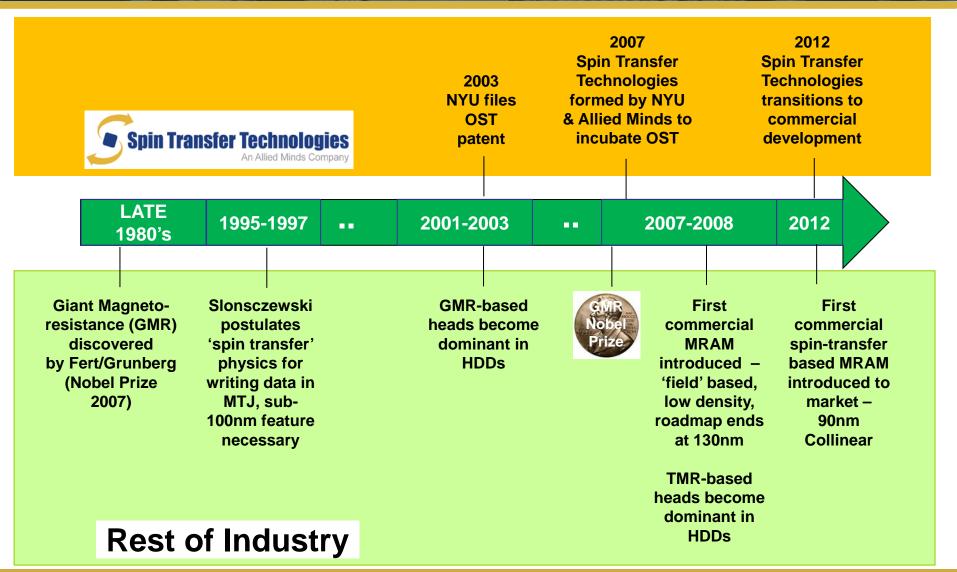

### History

### Technology

- Formed in 2007 by Allied Minds and NYU to commercialize Orthogonal Spin Transfer (OST) MRAM research led by Professor Andrew Kent

- In 2012, raised \$36 million financing from Allied Minds and Invesco and opened Silicon Valley headquarters

- OST-MRAM is a disruptive innovation in the field of spin transfer MRAM devices and offers advantages over other MRAM

- Higher speed, lower cost, lower power consumption, higher reliability, and enhanced lithographic scalability

### **Opportunity**

- Served Market

Opportunity of \$150

Billion in 2015

- Targeted as a replacement for DRAM, SRAM or flash memory

$\succ$

Markets in storage

systems, mobile

devices, computing,

microcontrollers and

SOCs in standalone or

embedded

configurations

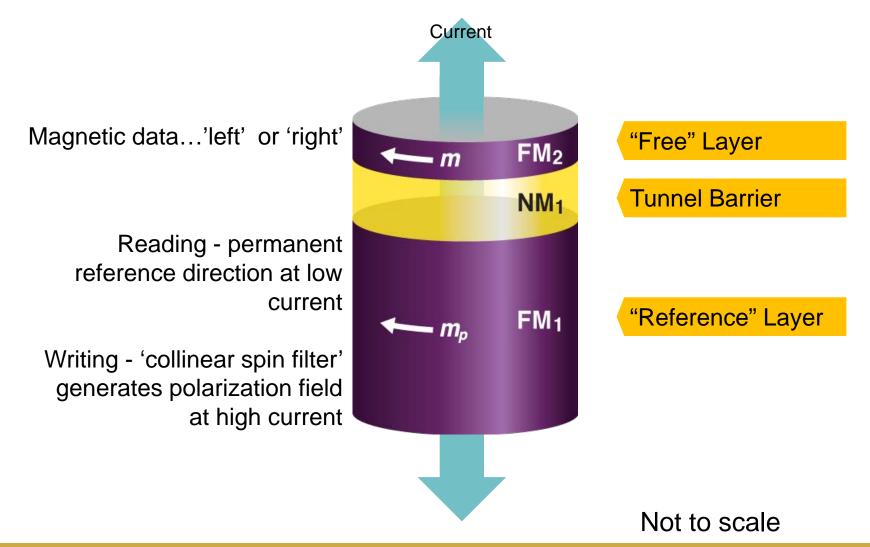

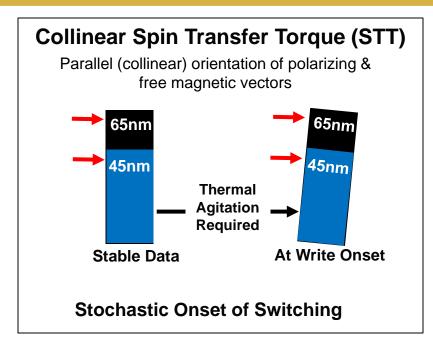

## Magnetic Tunnel Junction with Collinear Spin Filter

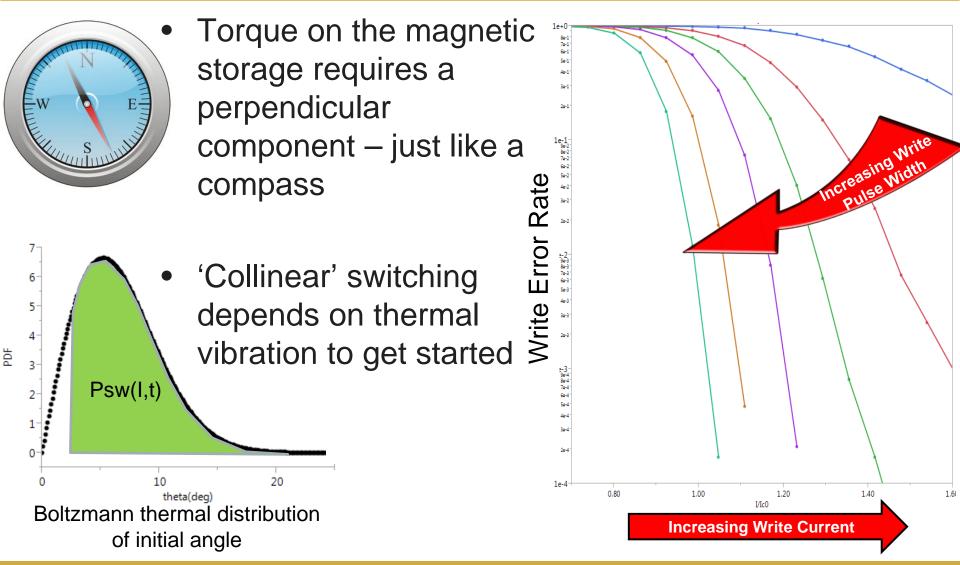

## Getting the 'write' started

### Collinear Spin Transfer – In a Performance Box

## Write Error Rate (WER) →Cost, i.e. ECC Write Voltage $\rightarrow$ Power and Endurance

#### Write Pulse Width →Performance and Power

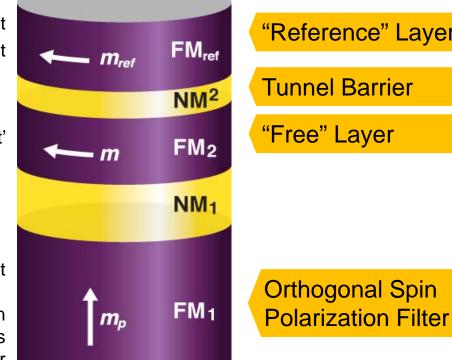

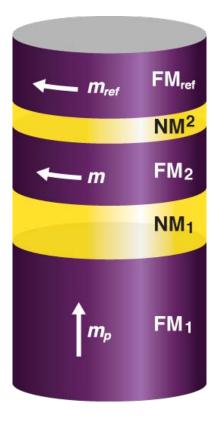

## **Magnetic Tunnel Junction** with Orthogonal Spin Filter

Reading - reference @ low current Writing - 'collinear spin filter' @ high current

Magnetic data...'left' or 'right'

Writing - 'orthogonal spin filter' @ high current

Strong perpendicular component to 'spin polarization field' instantaneously starts switching of magnetic data in free laver

Not to scale

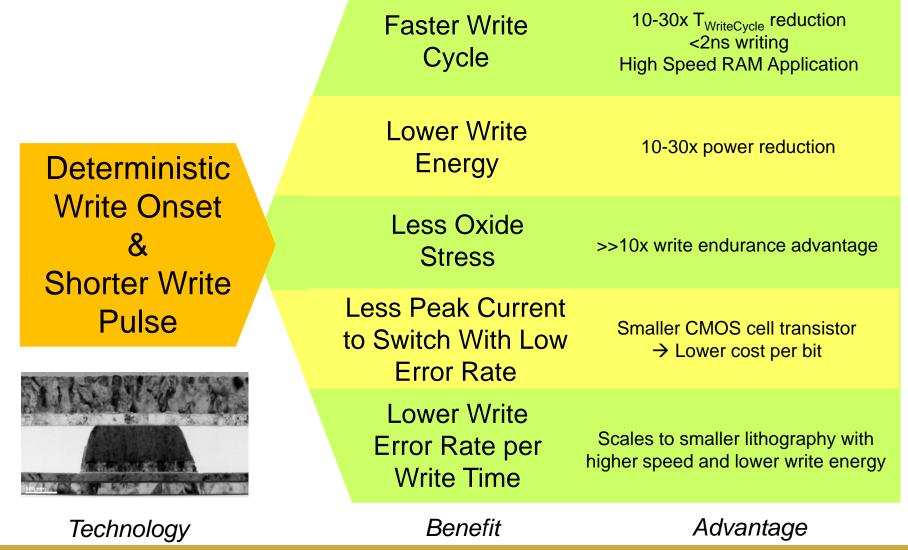

### OST Technology Benefits And Advantages

## **Product Benefits of OST**

| Tech Feature                 | Product Benefit                    | OST Comparison to Collinear-<br>ST                                                     |

|------------------------------|------------------------------------|----------------------------------------------------------------------------------------|

| Shorter write<br>pulse       | Faster write cycle                 | 10-50x t <sub>WriteCycle</sub> reduction<br><1ns writing<br>High speed RAM application |

|                              | Lower write energy                 | 10-50x power reduction                                                                 |

|                              | Less oxide stress                  | >>10x write endurance advantage                                                        |

|                              | Less total charge to switch<br>MTJ | Smaller CMOS switching transistor<br>→ smaller cost per bit                            |

| Deterministic<br>write onset | Higher intrinsic bit stability     | Scale to smaller lithography at high stability                                         |

#### **Collinear STT-MRAM vs. OST-MRAM** Spin Polarized Current Switching Analogy

|                           | STT                | OST                 |

|---------------------------|--------------------|---------------------|

| Switching Onset Delay     | Stochastic         | Deterministic       |

| Energy Required to Switch | Longer Write Pulse | Shorter Write Pulse |

| Scalability               | Less Scalable      | More Scalable       |

## Path to MRAM

# Among MRAM approaches, STT's OST-MRAM is uniquely advantaged

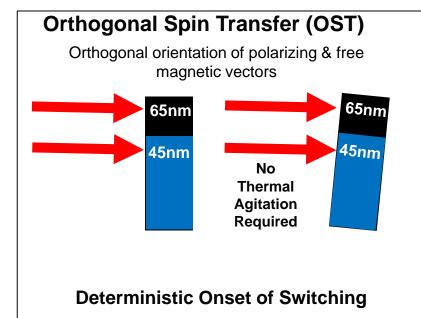

| Comparisons             | OST-MRAM                                                                                             | Other spin-torque MRAM                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Configuration           | Orthogonal orientation of pinned<br>magnetic vector versus free magnetic<br>layer (patent protected) | Parallel orientation of pinned and free magnetic vectors                    |

| Switching Process       | V Deterministic                                                                                      | 🗴 Stochastic                                                                |

| Switch Time             | No delay in onset                                                                                    | Incubation delay in onset                                                   |

| Switch Time Variability | <ul> <li>Reliable, short switch times</li> </ul>                                                     | X Variability in switching time                                             |

| Current                 | Switching at low currents allows smaller transistors                                                 | Large current to induce quicker switching                                   |

| Switching Energy        | <ul> <li>Low switch energy in proportion to<br/>reduced switching time</li> </ul>                    | <ul> <li>Average switch energy set by<br/>slowest switching bits</li> </ul> |

| Scalability             | <ul> <li>Scalable to small dimensions</li> </ul>                                                     | Scalability barriers at larger feature size                                 |