## NVDIMM CONTROLLER ARCHITECTURE

PAUL SWEERE Vice President, Engineering Viking Technology

## **NVDIMM**

- "Hybrid" Memory Module Combining DRAM and NAND

- Plugs Into JEDEC Standard DDR DIMM Socket

- Leverages Beneficial Characteristics Of Each Memory Technology

- Speed, endurance, and random byte addressability of DRAM

- Non-volatility of NAND Flash

- Enables Main Memory Persistence

- Data in DRAM is preserved through system power cycles

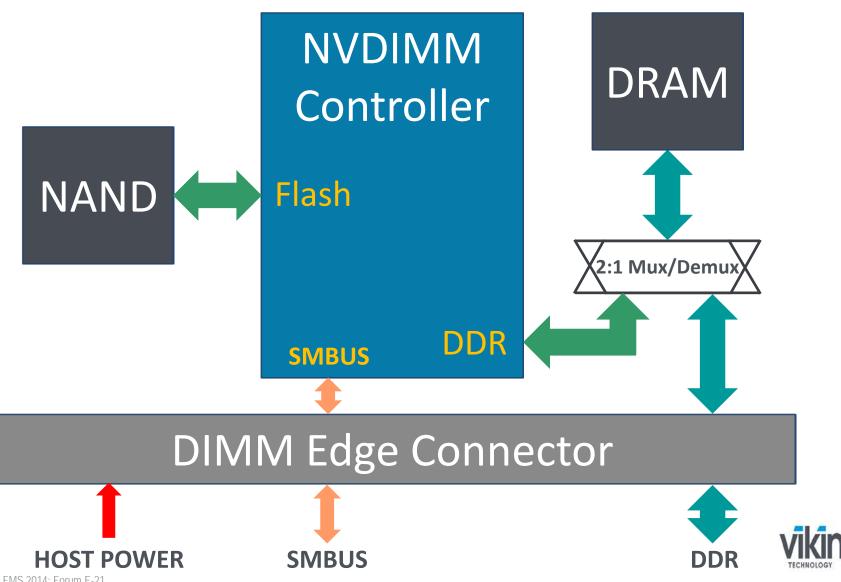

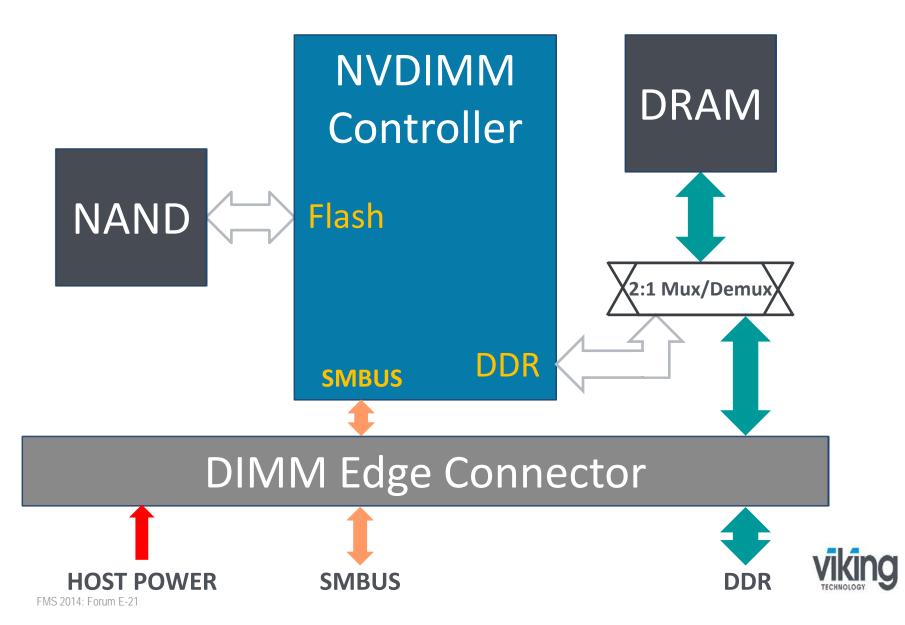

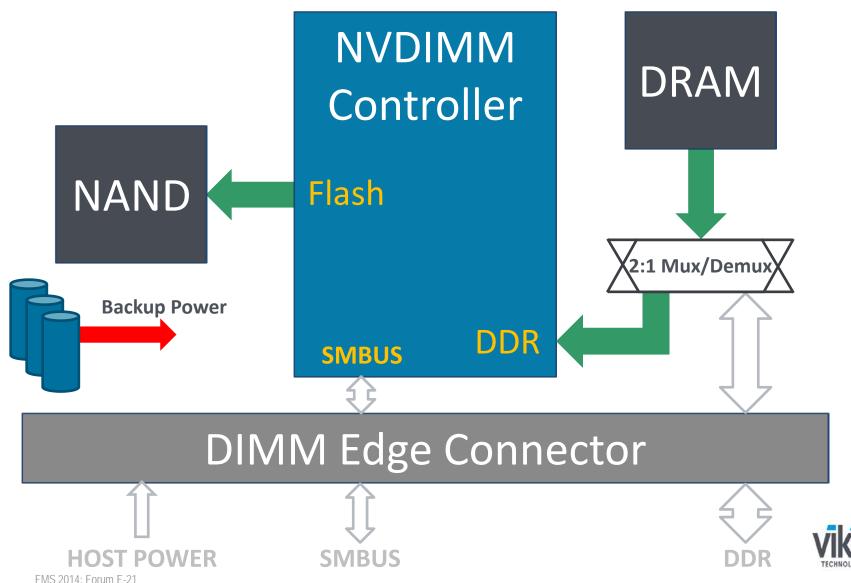

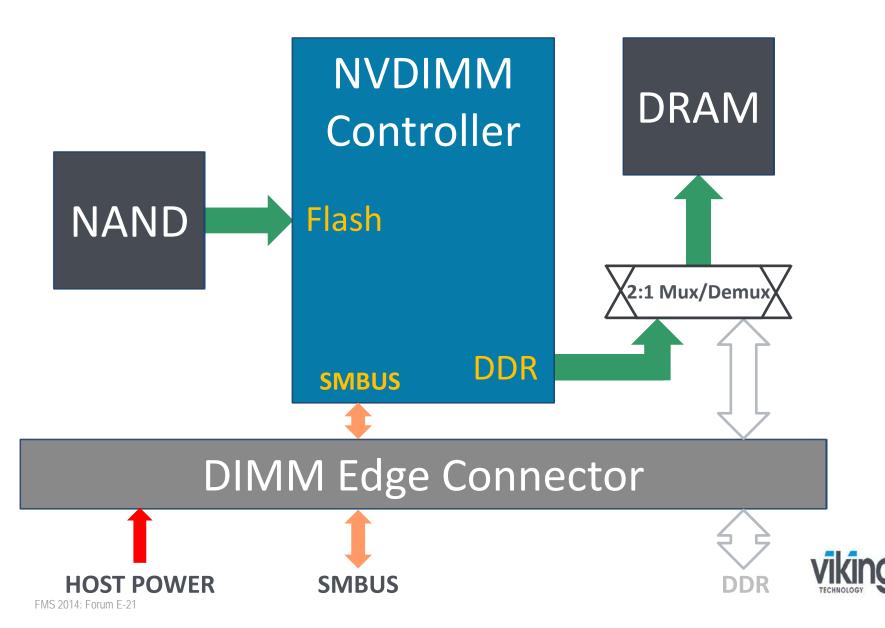

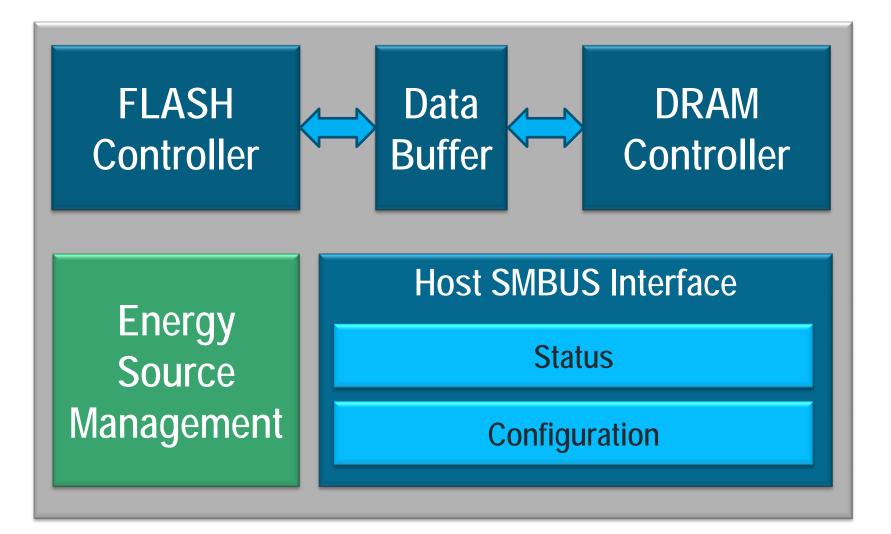

## **NVDIMM Block Diagram**

# **Standard DIMM Operation**

# **SAVE Operation**

# **RESTORE** Operation

#### **NVDIMM Controller**

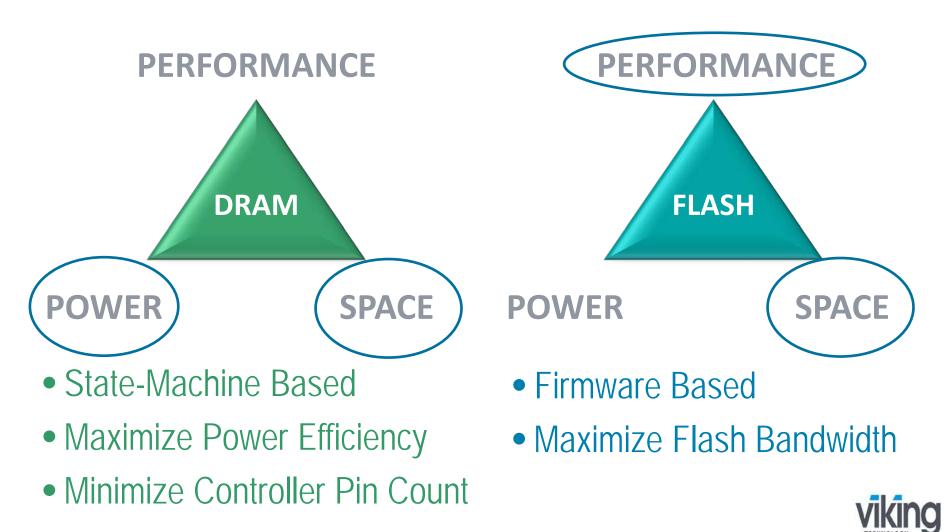

## **Memory Controller Design Tradeoffs**

• Key Goals: Minimize SAVE energy, board space, and cost

#### **Flash Controller Comparison**

|                                          | General Purpose SSD Controller                                              | NVDIMM Controller                                                                                        |

|------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Workload                                 | Heavy read to heavy write %,<br>random, sequential, small or large<br>block | During SAVE, 100% large block<br>sequential writes, During RESTORE,<br>100% large block sequential reads |

| Endurance                                | 1-10 DWPD                                                                   | <1 DWPD                                                                                                  |

| Static Data<br>Retention                 | Years                                                                       | Not required to preserve SAVE'd images once they've been restored.                                       |

| Performance<br>Consistency               | Tolerant to some variation in latency,<br>bandwidth                         | Strict requirement to complete SAVE<br>within maximum time limit. Write B/W<br>needs to be consistent.   |

| ECC, Wear<br>Leveling, Bad<br>Block Mgmt | Required. ECC strength appropriate to flash technology being deployed.      | Required. ECC strength appropriate to flash technology being deployed                                    |

| Garbage<br>Collection                    | Complex                                                                     | Straightforward                                                                                          |

| Read Disturb,<br>Read Scrub              | Required                                                                    | Not Required                                                                                             |

|                                          |                                                                             |                                                                                                          |

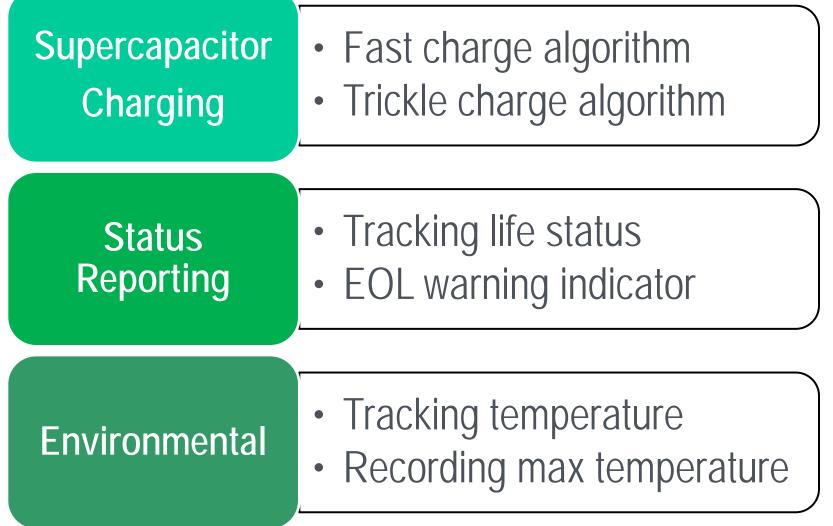

### **Energy Source Management**

### **Host Control / Status Interface**

#### Configuration

- ARM / DISARM NVDIMM

- Automatic SAVE Trigger Types

#### Control

- Commands: SAVE, RESTORE, ERASE

- Reset

#### Status

- NVDIMM Operating Mode

- Energy Source Health

- Flash Statistics

# **Questions?**

# **Thank You**