# **FLASH MEMORY SUMMIT**

#### PERSISTENT MEMORY APPLICATIONS TRACK AUGUST, 2014

Kaladhar Voruganti Senior Technical Director NetApp, CTO Office

© 2014, NetApp , All Rights Reserved

### Talk Focus: Persistent Memory Design Center

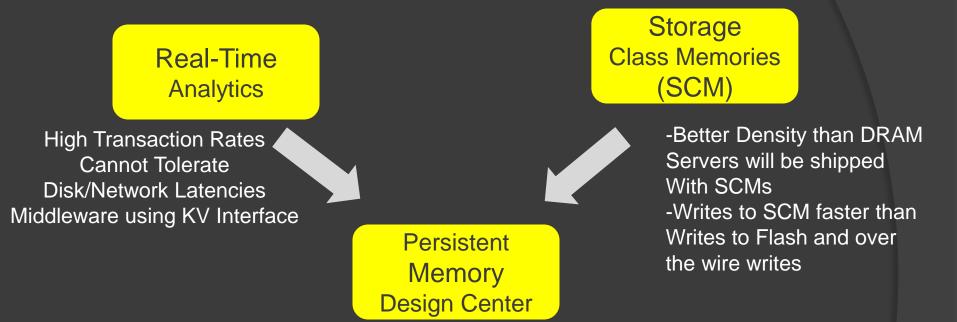

### **Confluence of Trends**

Primary Data Management Moving to Host (Key Control Point)

## **Real-Time Analytics Applications**

| Applications                                                                         | Characteristics                                                                                                                                   | Middleware | Products                                                         |  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------|--|--|

| Reservation<br>Banking<br>Financial                                                  | <ol> <li>Moderate Transaction Rate</li> <li>ACID</li> <li>Batch OLAP Queries on copy of data</li> <li>Moderate amount of data</li> </ol>          | SQL        | DB2,<br>Oracle,<br>SQLServer                                     |  |  |

| Document Systems,<br>User Preference Data<br>Machine Generated<br>Logs/Data          | <ol> <li>Eventual Consistency</li> <li>Very large amount of data</li> <li>Key-Value Access Model</li> <li>Both Batch/Real-time queries</li> </ol> | NoSQL      | Hbase,<br>Cassandra<br>CouchDB<br>MongoDB                        |  |  |

| Supply-Chain Apps<br>Fraud Detection<br>Stock Trading<br>Mobile Location<br>Services | 3 Mostly ACID Semantics                                                                                                                           |            | NuoDB,MemSQL,<br>SQLFire, VoltDB<br>SAP Hana, Oracle<br>TimesTen |  |  |

#### Different Types of Persistent Memory

|                          | PCM                                                      | STT-MRAM                                                   | ReRAM<br>/Memristor                      | N-RAM<br>(Nantero)                                      | DRAM                                 | NAND<br>(SLC/MLC)<br>2D-planar |

|--------------------------|----------------------------------------------------------|------------------------------------------------------------|------------------------------------------|---------------------------------------------------------|--------------------------------------|--------------------------------|

| Storage<br>Mechanism     | Phase change –<br>amorphous and<br>crystalline           | Magnetization of<br>ferromagnetic<br>layer                 | I on transport<br>and redox<br>reactions | Carbon nanotube-<br>based resistance<br>change elements | Charge on a<br>capacitor             | Floating Gate                  |

| Feature Size F           | 45nm                                                     | 65 nm                                                      | 30nm                                     | 22.nm                                                   | 36nm                                 | 22.nm                          |

| Cell Size                | 4.8F <sup>2</sup>                                        | 20 F <sup>2</sup> [14 F <sup>2</sup> (54n m)<br>(Grandis)] | 4 F <sup>2</sup>                         | 6F <sup>2</sup>                                         | 6 F <sup>2</sup>                     | 4 F² /2 F²                     |

| Read latency             | 12 ns                                                    | tor Endurance 8 Sr                                         | 10 ns                                    | 50us/100us                                              |                                      |                                |

| Write / Erase<br>latency | Better Endurance & Speeds than Flash<br>Byte Addressable |                                                            |                                          |                                                         | 10 ns                                | 500us/1m s                     |

| Write endurance          | 1E9                                                      | 1112                                                       |                                          | >169                                                    | 1E16                                 | 1E 5/ 1E 4                     |

| Data Retention           | >10yrs                                                   | >10 yrs                                                    | > 10 yrs                                 | >10yrs                                                  | 64 ms                                | >10 yrs (Fn of<br>writes)      |

| Write Voltage (V)        | з                                                        | 1.8                                                        | 0.6                                      | 3.5                                                     | 2.5                                  | 15                             |

| Read Voltage (V)         | 12                                                       |                                                            |                                          |                                                         | 1.8                                  | 1.8                            |

| Write Energy<br>(pJ/bit) | Lov                                                      | ver speeds but bette<br>DRAN                               | 4E-15                                    | 2E-9                                                    |                                      |                                |

| Idle Power               |                                                          |                                                            |                                          |                                                         | Med. (refresh)                       | Low                            |

| MLC (bits/cell)          | 2                                                        | Difficult                                                  | pated                                    | Possible                                                |                                      | 2/3 (max till 4)               |

| 3D solution              | Possible                                                 | At higher cost<br>(vertical MOSFET)                        | Feasible at<br>higher cost               | 2                                                       | Hybrid Memory<br>Cube applies<br>TSV | 3D (yes)                       |

| Scalability<br>Prospects | F < 10nm                                                 | F = 10-45nm                                                | F < 10nm                                 | F < 5nm                                                 | F=10nm                               | F = 10nm                       |

| Addressability           | byte                                                     | byte                                                       | 2                                        | ?                                                       | byte                                 | Page (r/w)<br>Block (erase)    |

### Two Persistent Memory Design Centers

### Transparent

© 2014, NetApp , All Rights Reserved

### "Transparent" NVM Adoption Drivers

- SCM/NVM treated as storage or DRAM

- Every app benefits from 'faster flash'

- Every app benefits from more 'memory'

DRAM cache in front of SCM

- Likely that mobile use cases will drive cost of SCM technologies down

## "Transparent" NVM Applications

#### Application characteristics

- Memory-based or Flash-based today

- Real-time latency / Hi Tx rate Databases

- Performance at any cost

#### **Current Design Center**

- POSIX Access Model

- Disk Optimized data structures (e.g. Column store) try to localize updates

- Coarse Grained file/LUN/Volume level Snapshots

- Coarse Grained SLOs (File, LUN/Volume) [specified out of band]

- Replication needed for both durability and HA

- Client-Network Storage Server Model

Persistent Memory Design Center

- Fine-grained Load/Store Access From User Space

- Processor Optimized Graph Data Structures that don't try to localize updates

- Data Structure level Versioning and recovery

- Data Structure level SLOs [specified in-band]

- Replication need for HA

- Peer to Peer Storage Model will gain traction

## "Disruptive" NVM Applications

- Memory-based or Flash-based today

- Real-time latency / Hi Tx rate

- Larger datasets than today's in-memory apps

- Apps that need zero downtime and instant recovery

# **Disruptive NVM Applications**

Medical/Wearable/Embedded

Conclusion: Asks

- Need end to end solutions (i.e. cannot develop persistent memory design center in isolation)

- Need to move checkpoints, versions to capacity storage

- Need New Hardware Service Models

- Need data structure level management semantic standards (e.g. persistence, consistency, SLOs)

- Need Rapid Re-Build Algorithms from slower media during failures