# **RRAM** in IoT

# Cliff Zitlaw Product Architect Crossbar Inc.

Flash Memory Summit 2014 Santa Clara, CA Session 304-C Flash and the Internet of Things

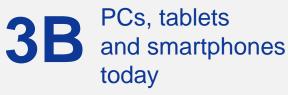

# IoT In the Next Few Years

Internet Connection Demands Increasing

IoT nodes increasing from:

### Computation Increasingly Moving to Nodes

### Technology Drivers Supporting Node Deployment

Sensors becoming increasingly affordable

Smartphones as a gateway for IoT nodes to the internet

Bandwidth cost dropped by 40x in the last 10 years

Processing costs dropped 60x in the last 10 years

# **RRAM as NVM Alternative in IoT**

Data Center – Block Oriented Data Storage

- Low latency(10<sup>-5</sup> s), high bandwidth, low power

- Native 3D compatible array architecture

- Alternatives: SSD, DRAM (disk cache), hard disk

Nodes – XiP Code and Random Access Data

- Low latency (10<sup>-8</sup> s), high bandwidth, low power

- CMOS BEOL compatible

- Alternatives: embedded NOR, discrete NOR

### Existing NV Memory Technology Comparison

|                           |                          |                            | RRAM                                    |                                        |

|---------------------------|--------------------------|----------------------------|-----------------------------------------|----------------------------------------|

| Feature                   | Embedded NOR             | NAND                       | Embedded 1T1R                           | 1TnR                                   |

| Non-Volatility            | Yes                      | Yes                        | Yes                                     |                                        |

| Random Read               | 40ns                     | 50us                       | 20ns                                    | 1us                                    |

| <b>Program</b><br>Time    | 268us/128B               | >1000us /8KB<br>(MLC)      | 12us/4B                                 | 64us/8KB                               |

| <b>Erase</b><br>Time/Size | 168ms/16KB               | >2ms(Block)                | Erase Not Required<br>EEPROM Emulation! |                                        |

| Endurance                 | 10 <sup>5</sup>          | MLC 10 <sup>3</sup>        | 10 <sup>8</sup> - 10 <sup>12</sup>      |                                        |

| Cell Size                 | 0.1um <sup>2</sup> @40nm | SLC 5F <sup>2</sup><br>MLC | 0.1um <sup>2</sup> @40nm                | SLC 4F <sup>2</sup> ,<br>Stacking, MLC |

| Cost                      | Med                      | Low                        | Low                                     | Very Low                               |

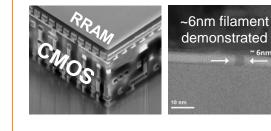

# Crossbar's RRAM-based Technology

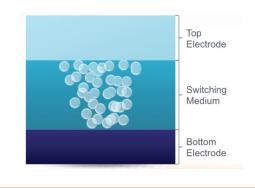

### Simple, 3 layer Approach

- Metallic top electrode

- Resistive switching

medium

- Non-metallic bottom electrode

- Electric field based filamentary switching

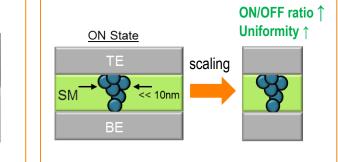

### CMOS Back-End-Of-Line Compatible

- RRAM layer(s) on top of CMOS logic

- Filament sizes less than 10nm demonstrated

- On/Off ratio improves with smaller geometries

### Array Architectures

- Data storage

- Approaching 4F<sup>2</sup> memory cell for data storage

- Natively 3D stackable

- Code storage

- Low latency

5

Flash Memory Summit 2014 Santa Clara, CA

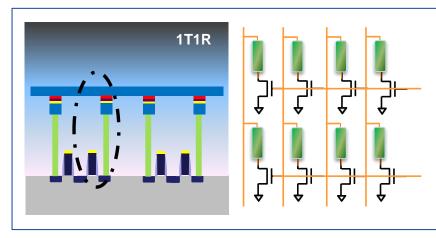

# **RRAM Array Architectures**

#### **1T1R with Linear RRAMs**

- Cell size dominated by the select transistor

- Suited for high speed embedded memory operation or high performance discrete NOR products

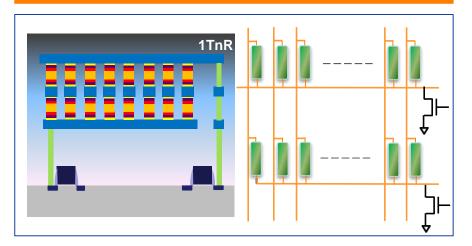

#### **1TnR with Non-Linear RRAMs**

- Effective cell size 4F<sup>2</sup>/ (number of RRAM layers)

- Under array is utilized for peripheral circuits – provides high array efficiency

- Suited for high density high performance memory (NAND/SCM memory)

### **Crossbar Development Schedule**

**1TnR Discrete**

**Device**

### **1T1R Embedded NOR Macro**

2Mb to 64Mb densities

Hard macro using 40um logic

Flash Memory Summit 2014 Santa Clara, CA

# **Thank You**

Flash Memory Summit 2014 Santa Clara, CA