# Emulating Rank Modulation in Flash Memories

Yue Li, Anxiao (Andrew) Jiang Eitan Yaakobi and Jehoshua Bruck

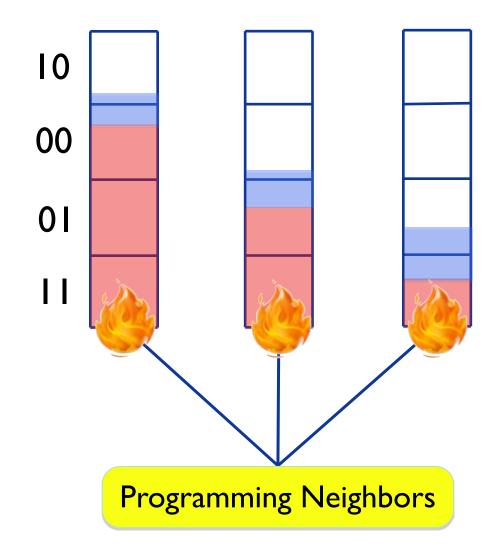

# Disturbance Issue

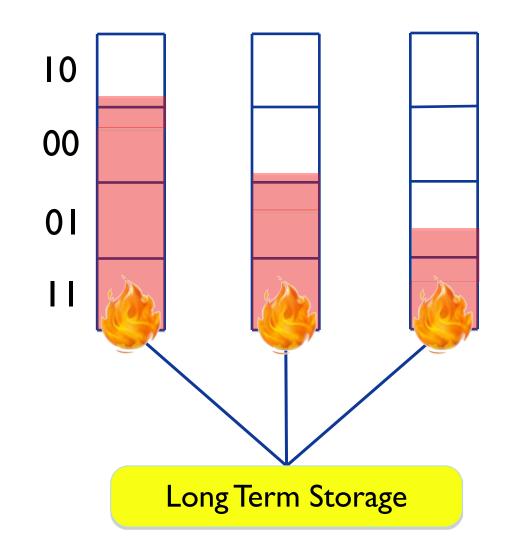

# Data Retention Issue

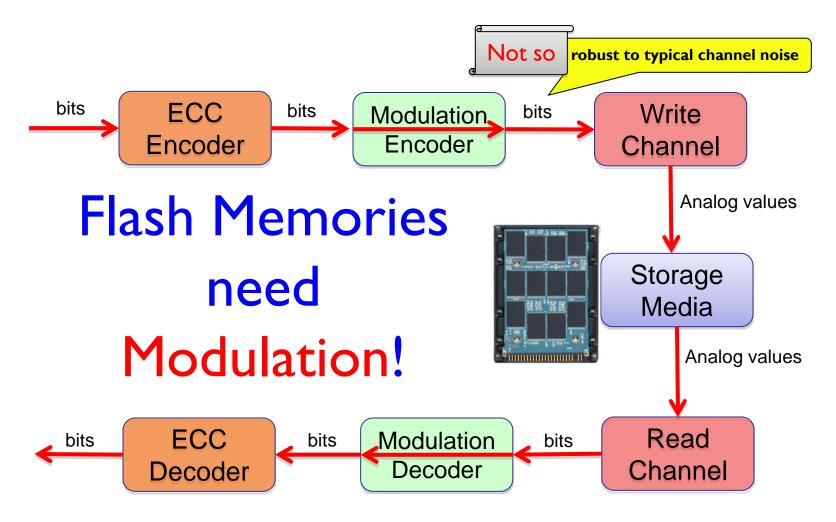

# Are there better data representations?

# Magnetic Recording vs Flash

## Flash Memory Rank Modulation: Use Relative Order!

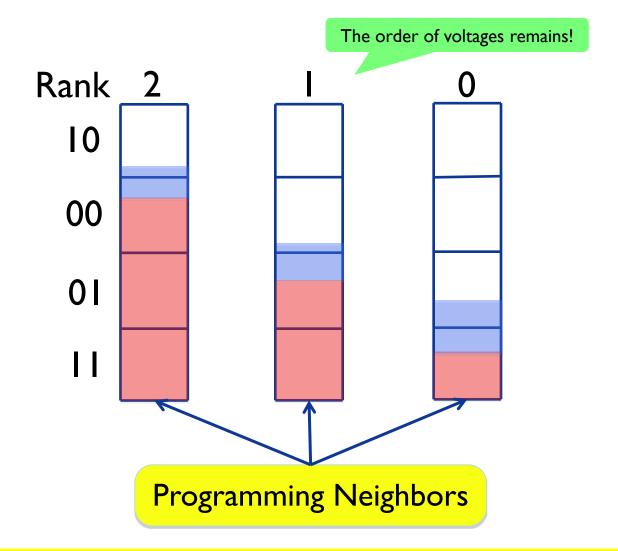

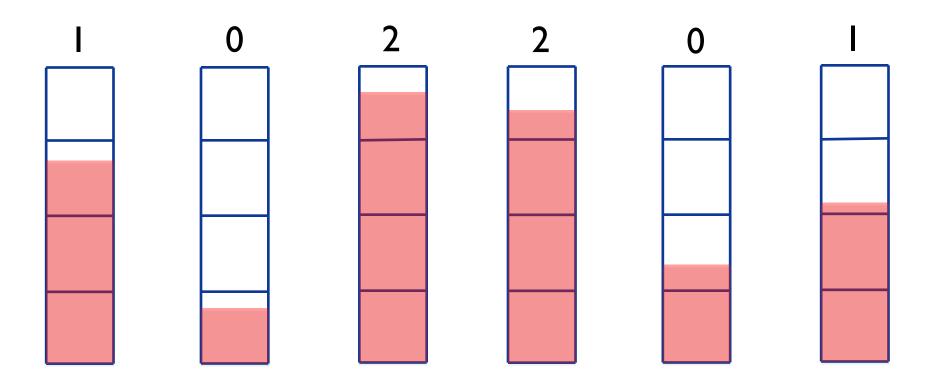

### Put More Cells in Each Rank

Example: 3 Ranks, 2 Cells/Rank

n: total number of cells

m: number of cells per rank

r: number of ranks, r = n / m

# $\log_2(n!/(m!)^r)/n$ (bits/cell) $\approx \log_2 r$

Cell Capacity (Bits/Cell)

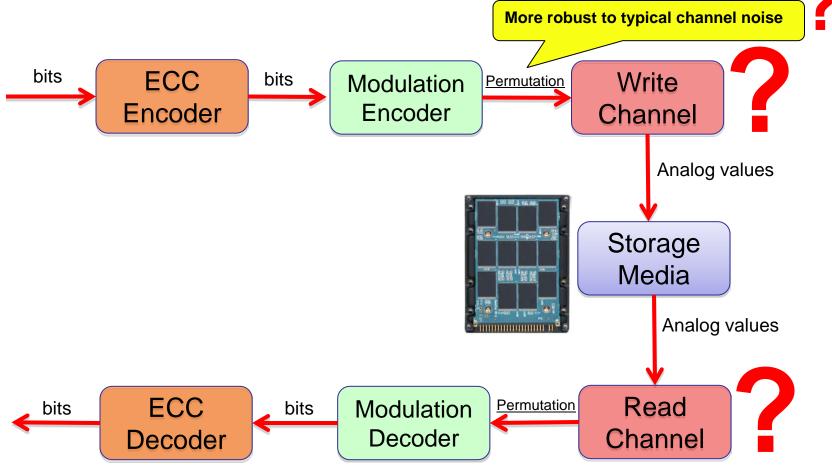

# Doing Rank Modulation

# Redesigning NAND Flash

#### emory Writing and Reading for Rank Modulation

## Program via standard interfaces

- Focus on r = 4 ranks for MLC

- Cell with rank k is programmed to level k

(k = 0, 1, 2, 3)

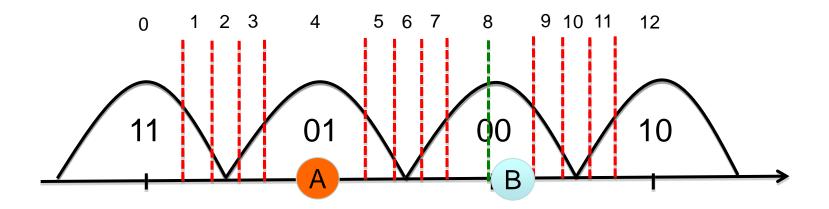

## Read via read-retry and sorting

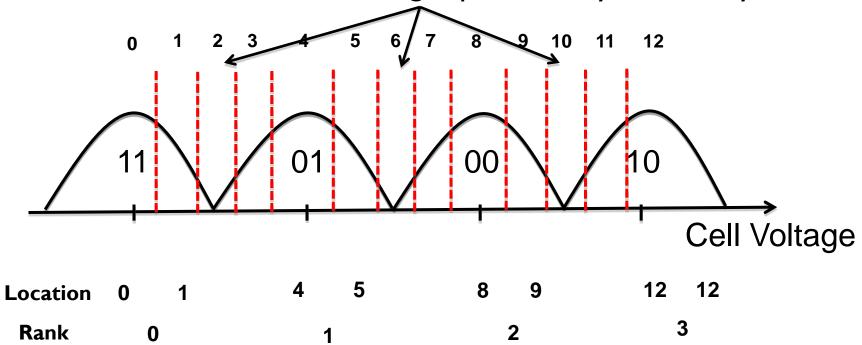

## Rank Modulation in MLC

Reference threshold voltages provided by read-retry

Example: n = 8, rank = 4

# **Experimental Configurations**

#### NAND flash chip

- Micron L84A 20nm MLC (MT29F64G08CBAB)

- 8 read-retry modes (we use modes 0 − 3)

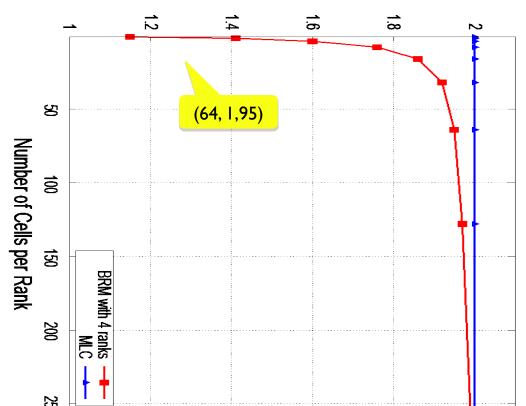

#### MLC v.s. RM without interference

- Cells tend to be underprogrammed

- Only program the even page of a wordline (WL)

- Skip the next WL after writing the current WL

#### MLC v.s. RM with interference

- Cell voltages drift to larger values

- Sequentially program each page in a block

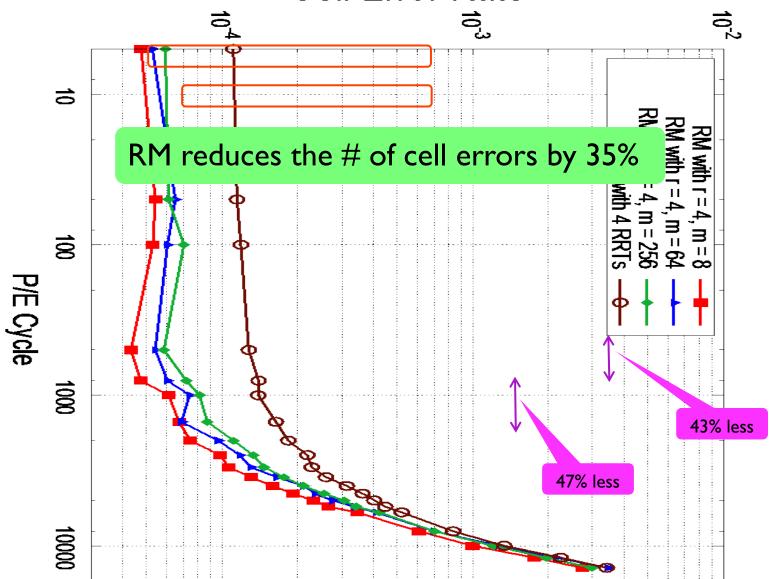

# Memory Comparing Cell Error Rates

- MLC

- A cell error happens if at least one bit of the cell is wrong

- Rank modulation

- A cell error happens if two cells switch their ranks

- e.g.  $(0, \underline{1}, \underline{0}, 3, 2, 1, 3) \leftarrow \rightarrow (0, \underline{0}, \underline{1}, 3, 2, 2, 1, 3)$

- Cell error rate =  $\frac{\text{Number of cell errors}}{\text{Total number of cells written}}$

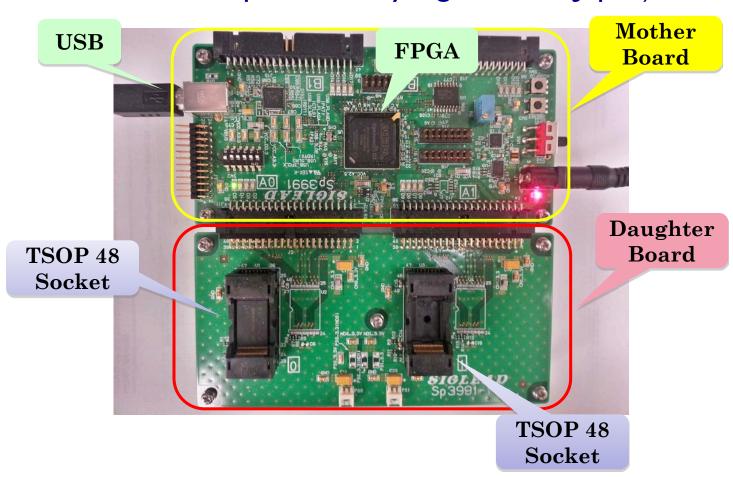

## FlashMemory NAND Evaluation Platform

- SigNAS-II

- FPGA based, produced by Siglead Inc. (Japan)

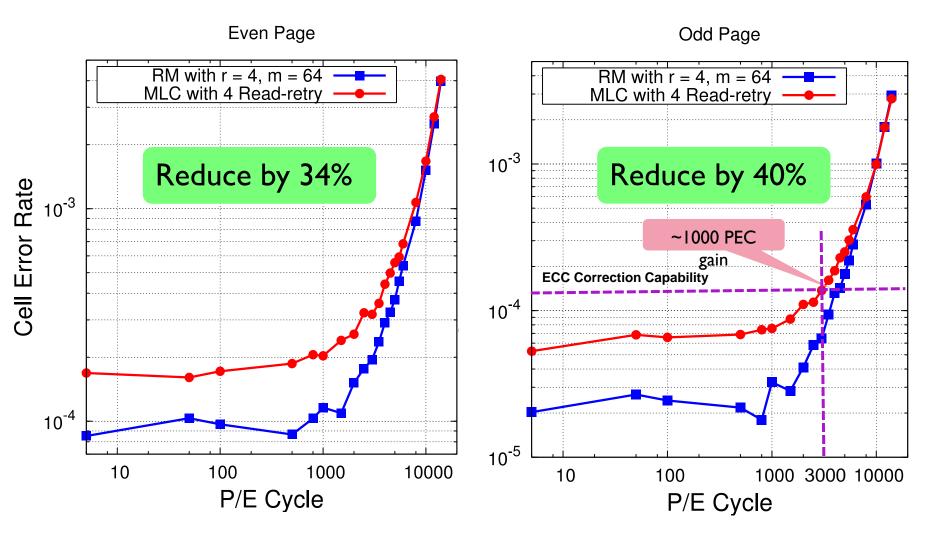

# Flash Memory Interference-free Performance

Cell Error Rate

# Performance under Interference

#### **Dominant Errors**

Better control of reference threshold voltages, and access to more read-retry modes will help!

#### Rank modulation

- is a modulator using relative order of voltages

- does not require redesigning flash

- reduce cell errors by 35% ~ 40% (comparing to MLC)

#### Ongoing work

- More characterizations, e.g. under retention, hardware latency

- Life time characterizations with ECC

- Supporting more chips from different vendors

# Memory Acknowledgement

#### Collaborators

- Eyal En Gad (Caltech)

- Dr. Yanjun Ma (Intellectual Ventures)

- Prof. Edwin Kan (Cornell)

- Kai Li and Oliver Hambrey (Siglead)

#### Vendors

- Micron NAND support team

- Hynix NAND flash technical marketing/FAQE team

#### Funding agencies

- Caltech office of technology transfer

- Intellectual Ventures