# Hardware NVMe implementation on cache and storage systems

### Jerome Gaysse, IP-Maker

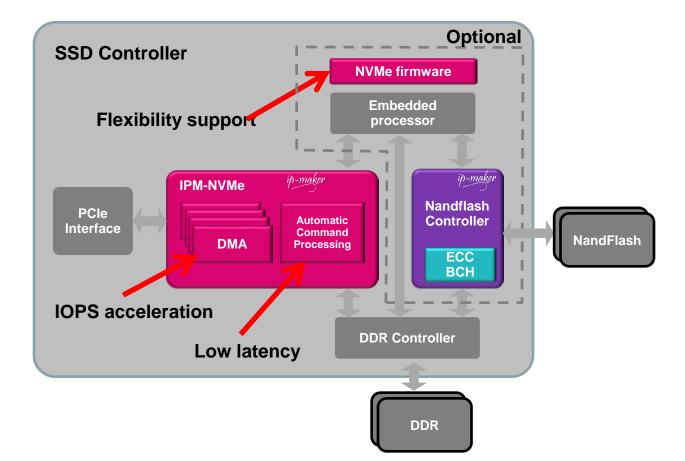

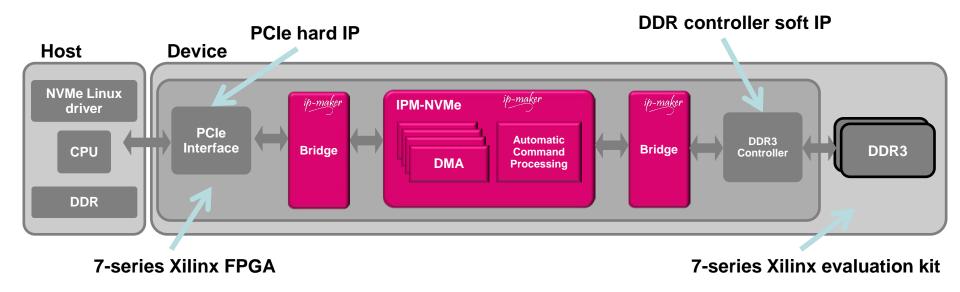

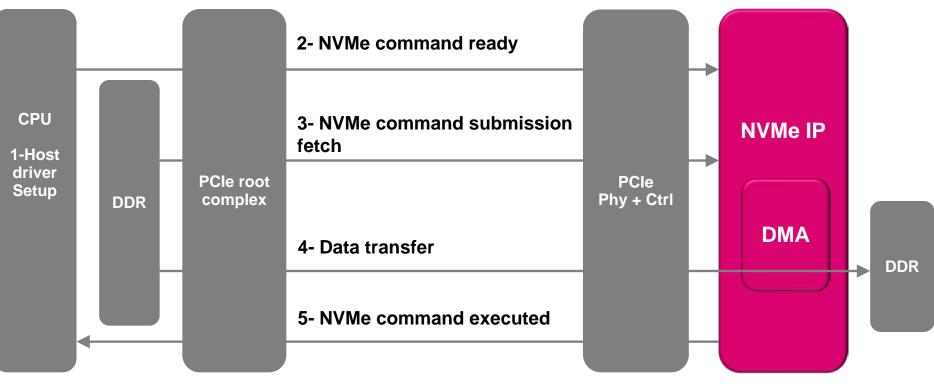

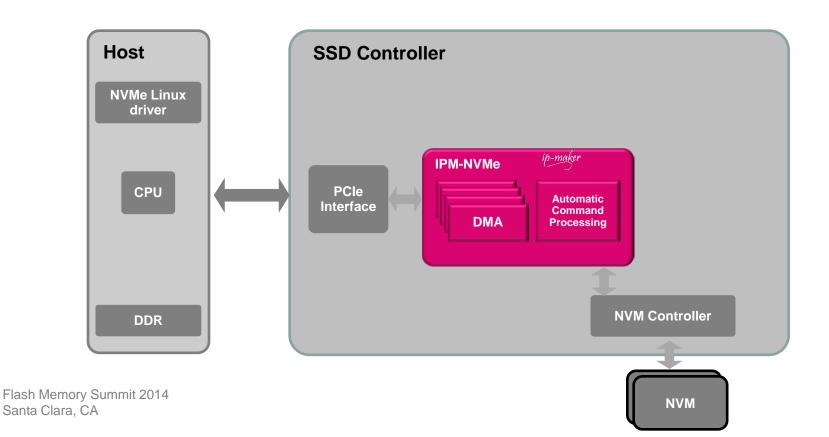

Hardware architecture

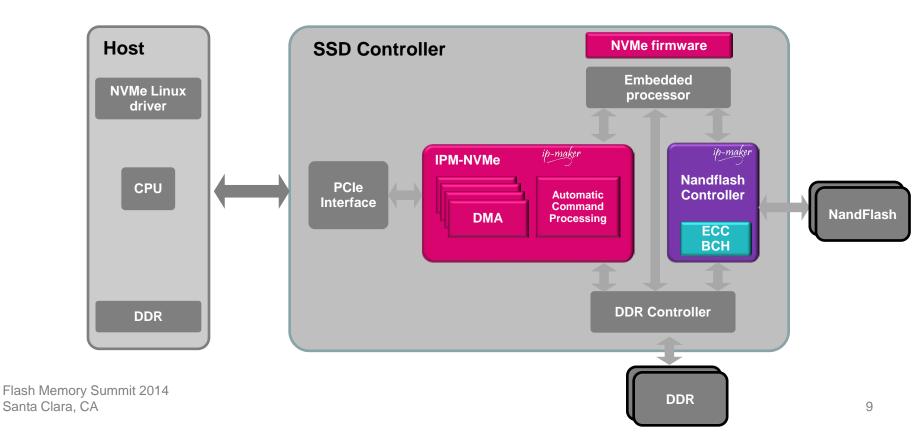

NVMe for storage

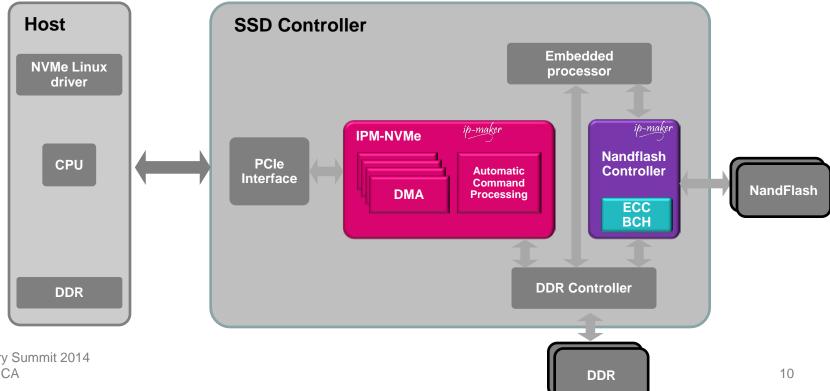

NVMe for cache/application accelerator

NVMe for new NVM

# Why NVMe for Data Center?

#### **Intensive applications**

Database Virtualization Big Data Analytics

# Data Center requirements

More performances (latency, IOPS) Higher memory capacity Non-volatile capabilities Lower power consumption

#### **Emerging technologies**

NandFlash New memories (MRAM/RRAM) New interfaces (NVMe)

IP-Maker makes the bridge

PCIe SSD for Storage Application acceleration

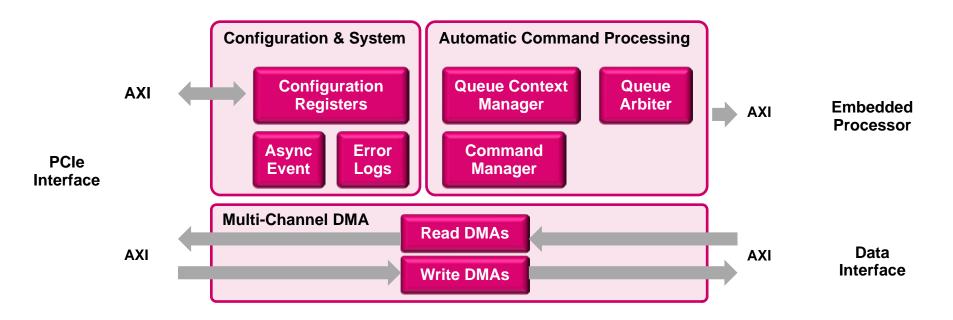

- Low latency with the automatic command processing

- IOPS acceleration with the multi-channel DMA

- Gen2 x4 configuration performances:

- IOPS: 350k

- Latency: 12µs

Lane speed is 5 Gb/s => 20 Gb/s

=> 610klOPS max?

But,

- 8/10bit coding

- => 499kIOPS max of data

- PCIe overhead (CRC...): 24B for a 256B payload

=> 446kIOPS max of useful data

- 90% bus use

- => 400klOPS max

- And other...

Flash Memory Summit 2014 Santa Clara, CA

# **Flash** Memory What is the latency for a Gen2 x4?

- 4µs for the host driver

- 8µs for all PCIe transactions

- Less than 0.1µs for the NVMe command processing

Flash Memory Summit 2014 Santa Clara, CA

- Hardware NVMe for high performance

- Firmware NVMe for command flexibility

- Hardware NVMe for high performance

- No need of flexibility: just performance

- CPU for NandFlash management

# Flash Memory NVMe for new NVM (MRAM, RRAM)

- Simplified architecture

- Lower latency

App to SSD IO Read Latency (QD=1, 4KB) NAND MLC SATA 3 ONFI2 NAND MLC SATA 3 ONFI3 NAND MLC PCIe x4 Gen3 ONFI3 Future NVM PCIe x4 Gen3 0 20 40 60 80 100 120 us

Flash Memory Summit 2013, Amber Hufflan, Intel

#### 12

- Benefits of a hardware NVMe architecture:

- Ultra low latency with hardware acceleration for NVMe command processing

- High IOPS with integrated multi-channel DMAs

- High memory capacity with scalable design

- New NVM capabilities

- Low power consumption thanks to hardware acceleration

## Visit IP-Maker booth #619 NVMe live demo!

Jerome Gaysse Business Development Manager jerome.gaysse@ip-maker.com www.ip-maker.com