# Taking Full Advantage of Ultra High Speed SD Cards

Miki Takahashi, Granite River Labs, Inc.

### Memory What is The Advantage of UHS-II?

- Faster Data Transfer

- Up to 312MB/s

- Easy Implementation

- Only 3 Differential Pairs

- Low EMI

- Differential Interface

- Low Power

- Low-Swing Signaling

- Low Power Mode

# Flash Memory What is The Advantage of UHS-II?

|                     | UHS-I                                     | UHS-II                                                            |

|---------------------|-------------------------------------------|-------------------------------------------------------------------|

| Interface Data Rate | 208MHz (4bits Data and Clock)             | 1.56Gbps (2 lanes Bi-Directional Data and Low Frequency RCLK)     |

| Clock Scheme        | Source Synchronous parallel Interface     | CDR Based Serial Interface                                        |

| Termination         | No                                        | Yes                                                               |

| Signal Swing        | 1.8V (3.3V Legacy Mode)                   | 400mV Differential Pk-Pk                                          |

| Electrical Spec     | Setup/Hold, Tr/Tf etc                     | Jitter Spec, Eye Mask                                             |

| Connector           | Treat as Mechanical Parts                 | Treat as Electrical Part (impedance, return loss)                 |

| Operational Mode    | Various Data Rates and DDR mode Supported | Various Data Rates, Half Duplex Mode,<br>Low Power Mode supported |

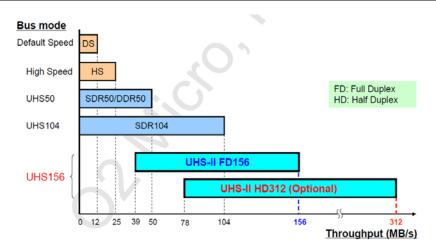

| Bus Spee   | ed Mode  | Maximum<br>Frequency | Signal<br>Voltage | Bus Maximum<br>Performance | Spec.<br>Version |

|------------|----------|----------------------|-------------------|----------------------------|------------------|

| Default Sp | eed (DS) | 25MHz                | 3.3V              | 12.5MB/sec                 | 1.01             |

| High Speed | d (HS)   | 50MHz                | 3.3V              | 25MB/sec                   | 1.10             |

| UHS-I      | SDR12    | 25MHz                | 1.8V              | 12.5MB/sec                 | 3.01             |

|            | SDR25    | 50MHz                | 1.8V              | 25MB/sec                   |                  |

|            | SDR50    | 100MHz               | 1.8V              | 50MB/sec                   |                  |

|            | SDR104   | 208MHz               | 1.8V              | 104MB/sec                  |                  |

|            | DDR50    | 50MHz                | 1.8V              | 50MB/sec                   |                  |

| UHS-II     | FD156    | 52MHz x30            | LVDS              | 156MB/sec                  | 4.00             |

|            | HD312    | 52MHz x30            | LVDS              | 312MB/sec                  | 4.20             |

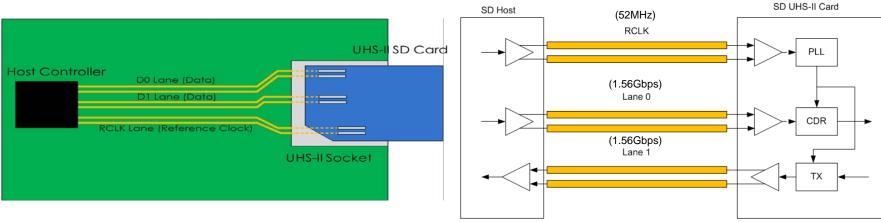

### Memory UHS-II Interface Overview

### **UHS-II Platform**

### Clocking and Data Transfer

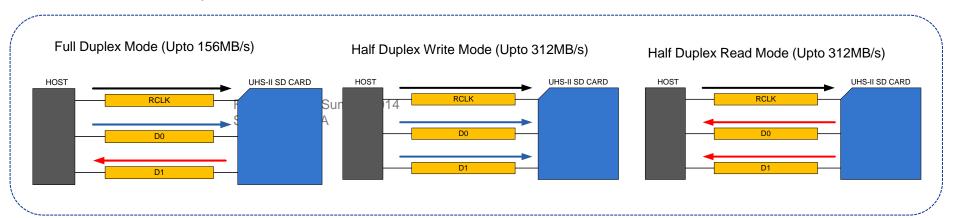

### **UHS-II Full and Half Duplex**

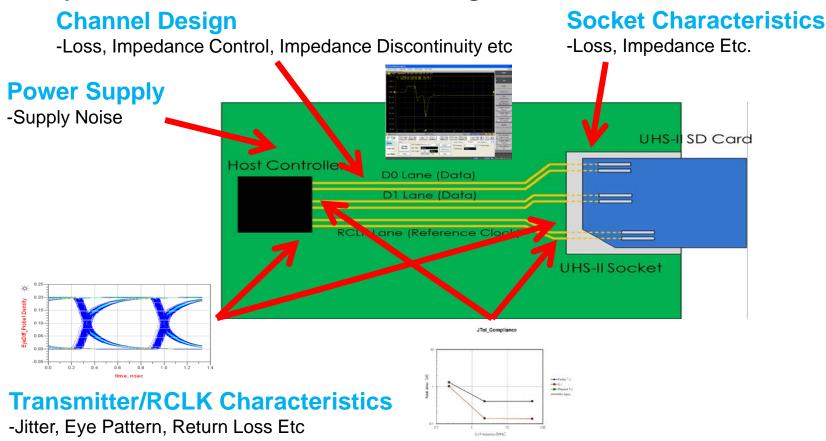

## **UHS-II Implementation/Validation**

Key Factors in Successful Design

### **Receiver Characteristics**

-Jitter Tolerance, Return Loss Etc

- "UHS-II Test Guidelines" are Released from SDA.

- -Electrical Test Guidelines

- -Protocol Test Guidelines

- "UHS-II Test Tools" are Available from Test Equipment Vendors.

### **Examples of Test Items**

#### **Electrical Test**

| TG1-5   | 3.2.2   | Host RCLK Tx Specifications (@TP2)          |   |

|---------|---------|---------------------------------------------|---|

|         |         | Fill out the results in Table List - 5      |   |

| TG1-5-1 | 3.2.2.1 | RCLK Frequency and Data Rate                | х |

| TG1-5-2 | 3.2.2.2 | Differential voltage (+/- <u>Vdiffmin</u> ) | х |

| TG1-5-3 | 3.2.2.3 | Rise/fall time (Tr/Tf)                      | х |

| TG1-5-4 | 3.2.2.4 | Common mode voltage (Vcm)                   | х |

| TG1-5-5 | 3.2.2.5 | Total jitter (Tj)                           | х |

| TG1-5-6 | 3.2.2.6 | Duty cycle (Tckh)                           | x |

| TG1-6   | 3.2.3   | Host D0/D1 Tx Specs (@TP2)                  |   |

|         |         | Fill out the results in Table List - 6      |   |

| TG1-6-1 | 3.2.3.1 | Differential voltage (+/- Vdiffmin)         | х |

| TG1-6-2 | 3.2.3.2 | Eye- pattern and Total Jitter               | x |

| TG1-6-3 | 3.2.3.3 | Rise/fall time (Ir/If)                      | x |

| TG1-6-4 | 3.2.3.4 | Common mode voltage (Vcm)                   | х |

| TG1-6-5 | 3.2.3.5 | EIDL state differential voltage (Vdiff_pd)  | x |

| TG1-6-6 | 3.2.3.6 | EIDL state common mode voltage (Vcm_pd)     | х |

| TG1-6-7 | 3.2.3.7 | Lane 0/1 skew ( <u>Skinter</u> )            | x |

#### Protocol Test

| No. | Test Item                                                                                                                                                                                                            | Target |        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| No. | Test item                                                                                                                                                                                                            |        | Device |

| 1-1 | Interface Speed (FD mode): Device shall fully support Interface speed from 39MB/sec to 158 MB/sec in FD mode.                                                                                                        |        | X      |

| 1-2 | Interface Speed (FD mode): Host shall support at least one Interface speed from 39MB/sec to 78 MB/sec in FD mode.                                                                                                    | х      |        |

| 1-3 | Interface Speed (2L-HD mode): Device shall fully support Interface speed from 78MB/sec to 312 MB/sec in 2L-HD mode.                                                                                                  |        | X      |

| 1-4 | Supporting Legacy SD I/F:<br>Host shall initialize Legacy SD I/F if UHS-II I/F is not detected.                                                                                                                      | х      |        |

| 1-5 | Direction of D0 and D1: As default, direction of D0 and D1 Lanes are downstream and upstream respectively.                                                                                                           | х      | x      |

| 1-6 | Direction of D0 and D1 on 2L-HD mode write: Direction of D0 and D1 Lanes are both downstream when Host sends data to Device.                                                                                         | х      | x      |

| 1-7 | Direction of D0 and D1 on 2L-HD mode read: Direction of D0 and D1 Lanes are both upstream when Host receives data from Device.                                                                                       | х      | x      |

| 1-8 | RCLK: RCLK shall be distributed individually to removable Devices. In case of Ring connection, RCLK is distributed by either point to point method (like Figure 3-8 (a)) or multi-drop method (like Figure 3-8 (b)). | х      |        |

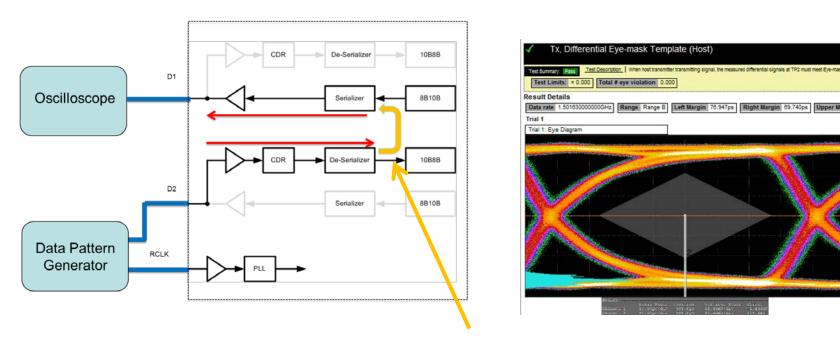

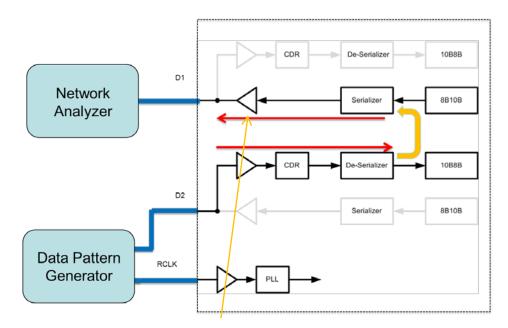

- Transmitter Test

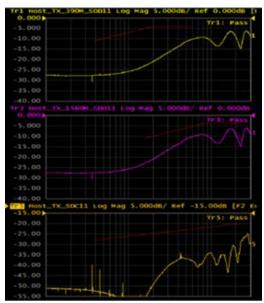

- Eye Pattern and TX Parameter Test

Loopback mode is defined in the spec.

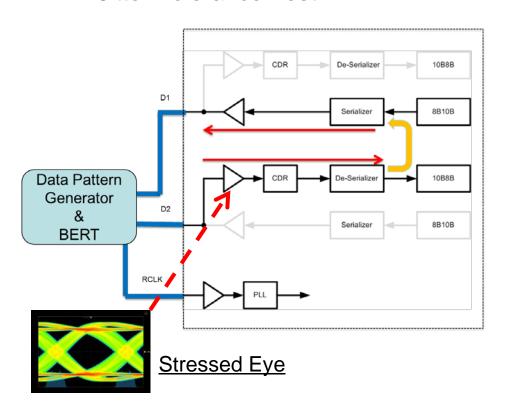

- Receiver Test

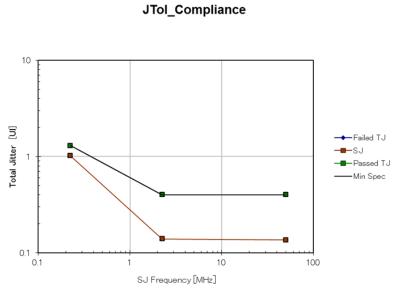

- RX Jitter Tolerance Test

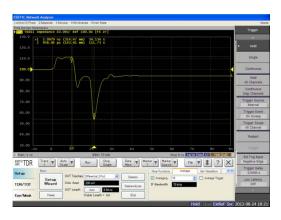

- Return Loss / Impedance Test

- Hot TDR and Return Loss

**Exercise The Transmitter**

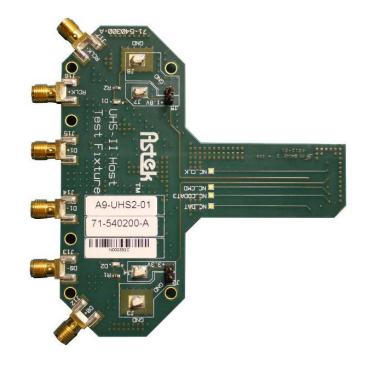

- Test Fixtures

- Card Test Fixture

### Host Test Fixture

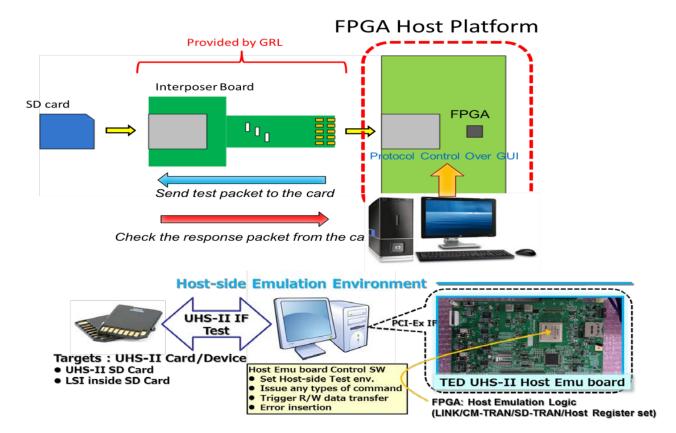

- Protocol Test (Test Demo at SDA Booth)

- UHS-II Host/Card Tester