#### How Good Is Your Memory? An Architect's Look Inside SSDs

Michael Abraham (mabraham@micron.com) Business Line Manager Micron Technology, Inc.

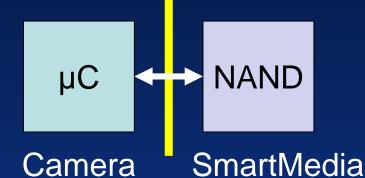

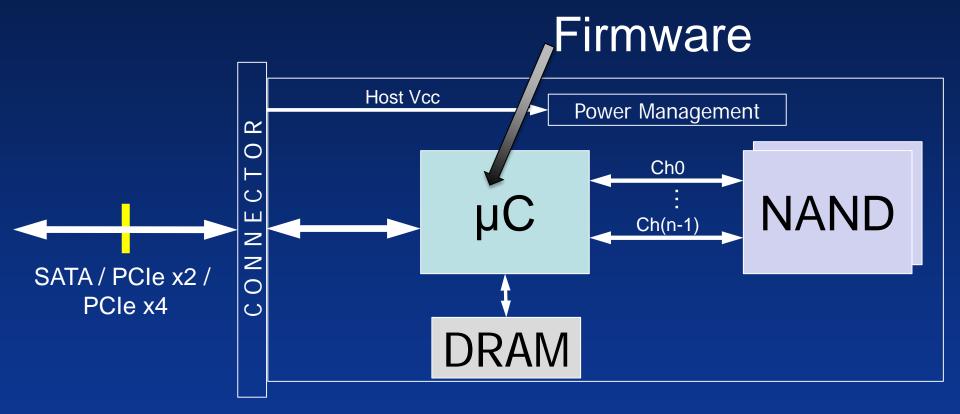

#### Farly Storage Optimizations

Slow

Early obsolescence

Inexpensive solution

μC/

**SRAM**

CF/USB/SD

# FasterUpgradeableSlightly more expensive

Santa Clara, CA August 2015 NAND

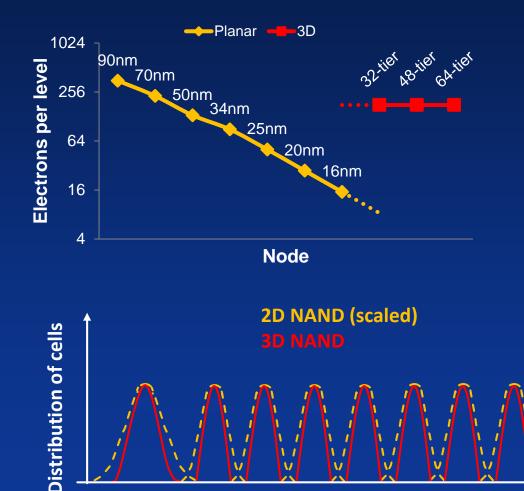

• The industry went through 7-9 NAND lithography transitions

Santa Clara, CA August 2015

Data based on publicly known information.

#### ry What Happened in That Decade?

- Density: 2Gb  $\rightarrow$  128Gb per die

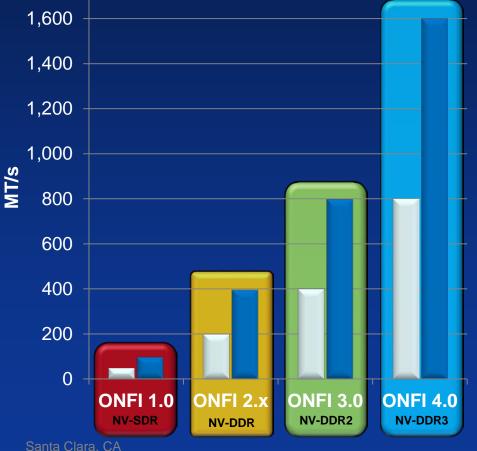

- Interface: 40MHz SDR  $\rightarrow$  266MHz DDR

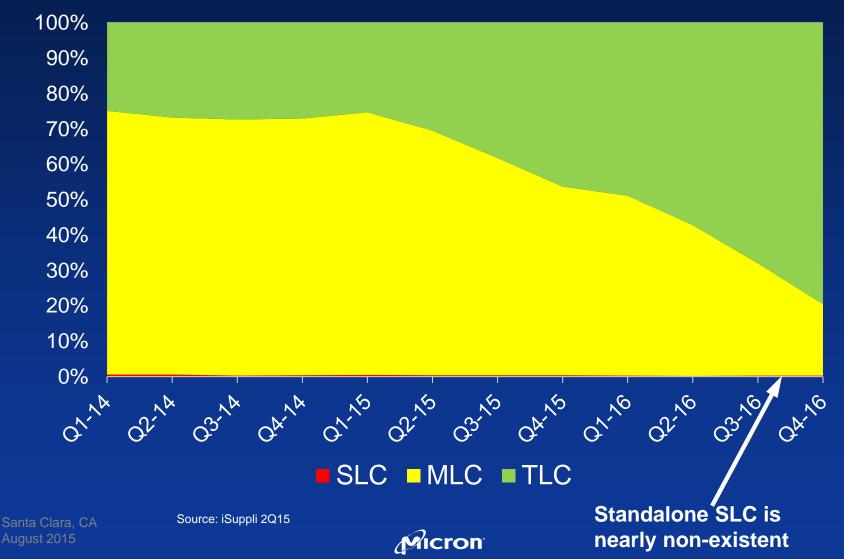

- Bits per Cell: SLC  $\rightarrow$  MLC  $\rightarrow$  TLC

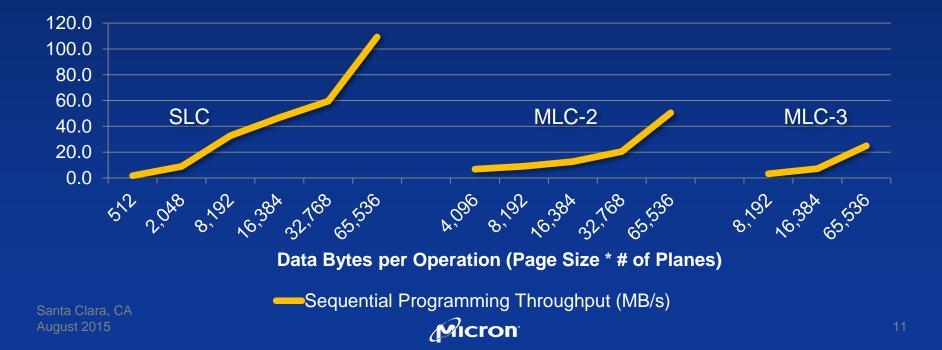

- Planes:  $1 \rightarrow 2 \rightarrow 4$

- Page size:  $2KB \rightarrow 16KB$

- Block size:  $128KB \rightarrow 8+MB$

- Packaging: 1ch TSOP-48  $\rightarrow$  4ch BGA

- ECC: 1-bit Hamming  $\rightarrow$  RS?/BCH  $\rightarrow$  LDPC

- Electrons per Cell State: >  $300 \rightarrow 16$

- Engineering skill: 1 college kid  $\rightarrow$  3+ PhDs

#### Could We Scale Planar NAND Beyond 16nm?

- Lower cost per bit

- Higher ECC

- Longer array operations

- Less data retention

- Less endurance

- More PhDs

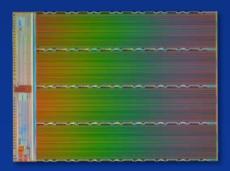

## 3D NAND: Standing NAND on Its Head

- 3D NAND cell architecture enables significant performance improvement

- 3D NAND cost improvement over planar expands with subsequent nodes

#### 3D NAND Reliability Relative to Planar NAND

3D NAND cell design simultaneously improves performance and reliability

- Vertical stacking allows large number of electrons per cell independent of scaling

- No longer relying on lithography to continue scaling

- Decreased interference between cells translates into higher cycling endurance

- Uses familiar memory materials – CT or FG

Vt

#### **3D NAND Enables New Die Densities**

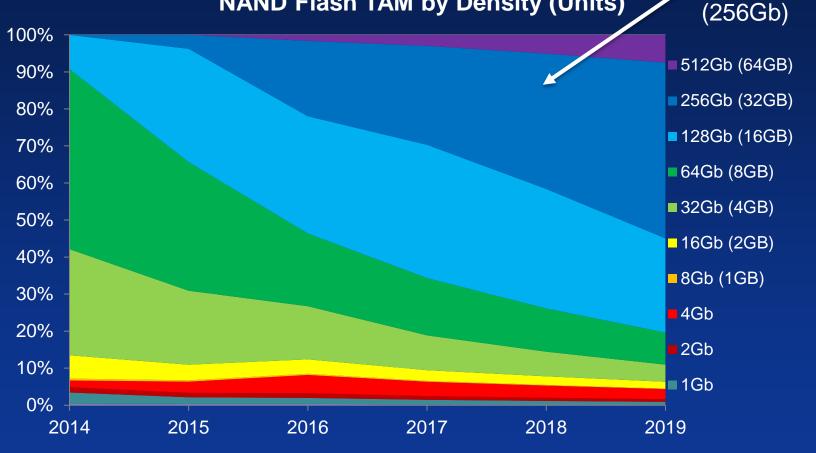

NAND Flash TAM by Density (Units)

3D NAND in

earnest here

#### 3D NAND Improves Array Performance

Faster write bandwidth a result of larger number of data bytes per operation and a reduction in tPROG

August 2015

### ONFI 4 Results in Lower Energy

Micron

Single Channel Package Dual Channel Package

- ONFI 4.0 to be introduced with 3D NAND

- Interface up to 800MT/s throughput

- Reduces energy per bit with 1.2V interface

- Density: Introduction of 256Gb

- Interface: ONFI 4.0, 1.2V

- Bits per Cell: MLC, TLC with SLC modes

- Electrons per Cell State: ~200

- Page/block/plane architecture follow traditional NAND scaling path

- Engineering skill: 1 college kid 3+ PhDs

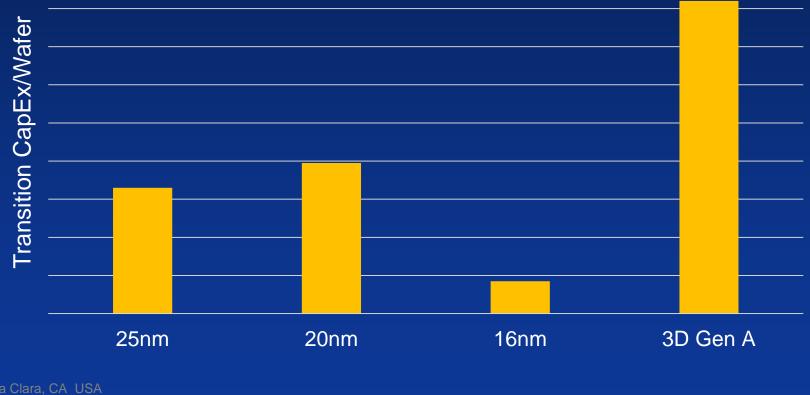

#### NAND Cost of Transition requires considerably new tooling

#### Questions?

- Business Line Manager in the Storage Business Unit at Micron

- Former NAND Architect

- Covers emerging memories and 3D XPoint<sup>™</sup>

- IEEE Senior Member

- BS degree in Computer Engineering from Brigham Young University

©2007-2015 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

Santa Clara, CA August 2015