# **Extending NAND Endurance with Advanced Controller Technology**

Wei Lin

System Architect, Phison wei\_lin@phison.com

PHISON's presentation contains forward-looking statements subject to significant risks and uncertainties. Actual results may differ materially from those contained in the forward-looking statements. Information as to those factors that could cause actual results to vary can be found in PHISON's annual reports and other documents filed from time-to-time with the TWSE. Except as required by law, we undertake no obligation to update any forward-looking statement, whether as a result of new information, future events, or otherwise.

#### PHSON Knows What You Need

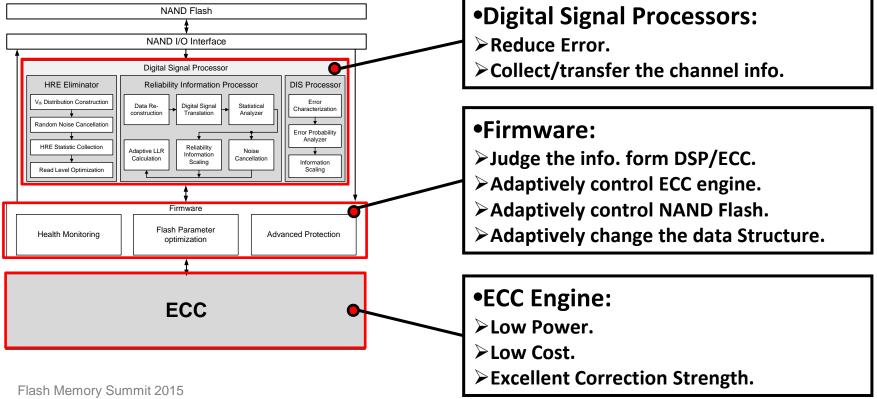

#### Error Handling Tech. in Controller

Santa Clara, CA

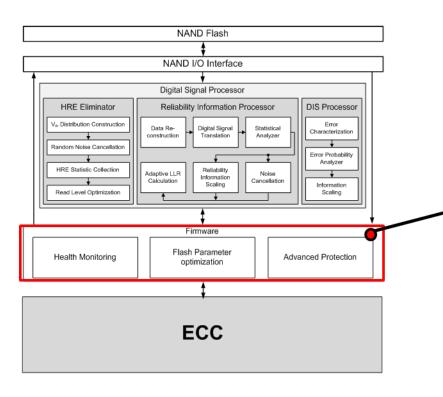

#### Flash Memory Error Handling Tech. in Controller

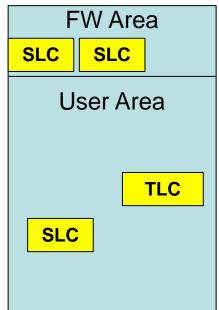

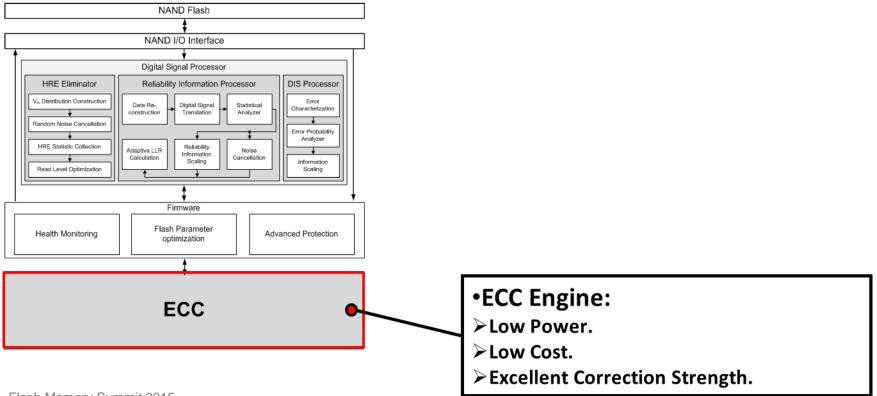

- Digital Signal Processors:

- **≻**Reduce Error.

- **➤** Collect/transfer the channel info.

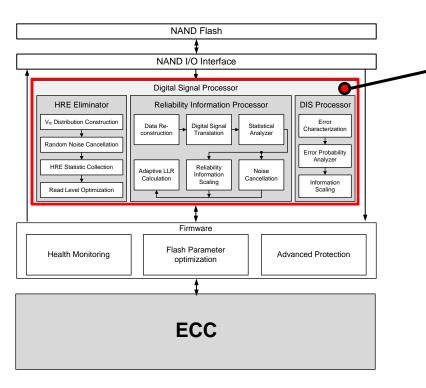

## PHISON PHISON Digital Signal Processor in Controller

- Monitor the health of the Data.

- Estimate/collect the channel information.

- Convert the channel information to reliability info. for ECC.

- Reduce the input errors (normal errors & HRE).

- Improve the decoding throughput.

- Reduce the complexity of the decoding flow.

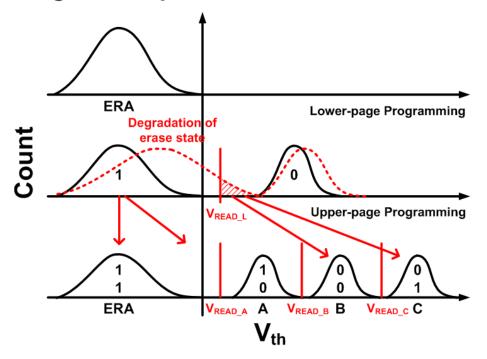

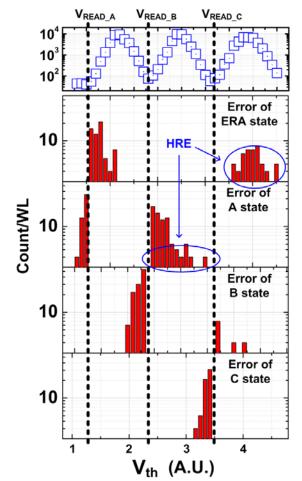

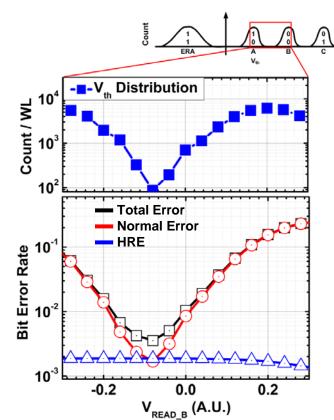

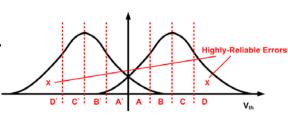

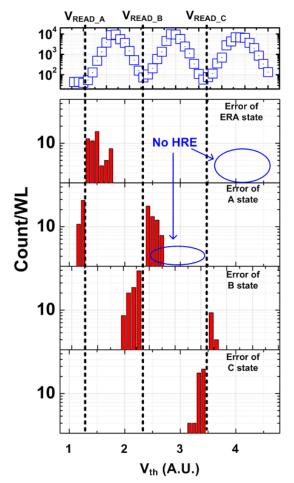

#### FlashMemory What's HRE?

#### **Program Sequence of MLC NAND Flash**

Flash Memory Summit 2015 Santa Clara, CA

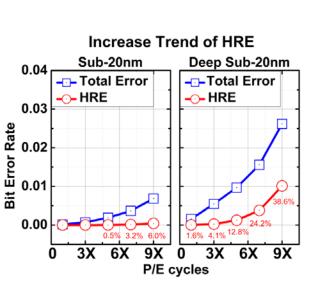

#### The Impact to the Reliability

**BCH**

**LDPC**

Reliability Information (RLY-I): | D | > | C | > | B | > | A |

RLY-I =

$$\log \frac{P(x_i=0|y_i)}{P(x_i=1|y_i)}$$

Flash Memory Summit 2015 Santa Clara, CA

#### **HRE Eliminator**

#### Flash Memory Error Handling Tech. in Controller

#### •Firmware:

- **➤ Judge the info. form DSP/ECC.**

- >Adaptively control ECC engine.

- >Adaptively control NAND Flash.

- >Adaptively change the data Structure.

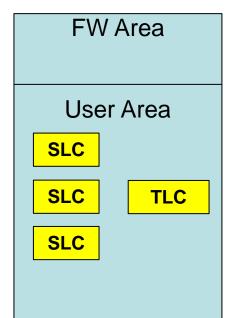

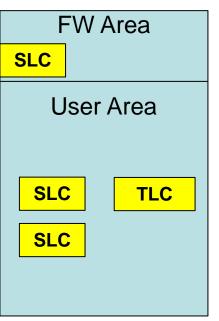

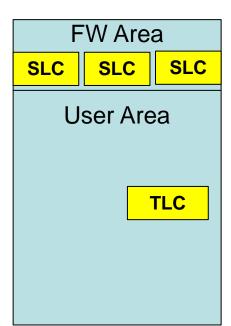

#### Adaptive Data Structure

#### Flash Memory Error Handling Tech. in Controller

Flash Memory Summit 2015 Santa Clara, CA

#### Migration of ECC Technologies

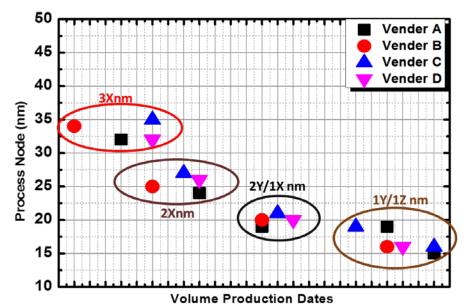

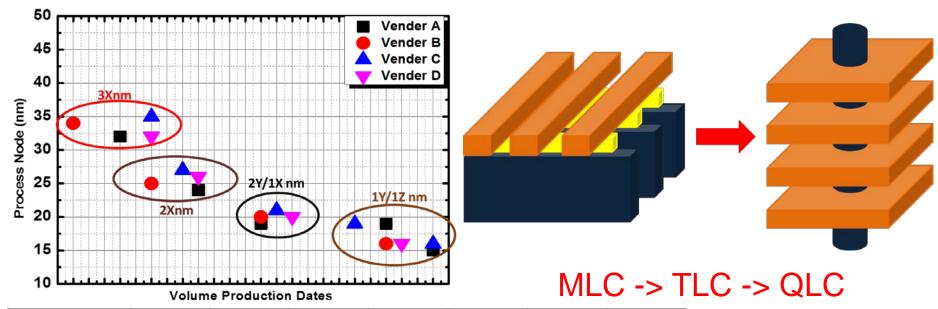

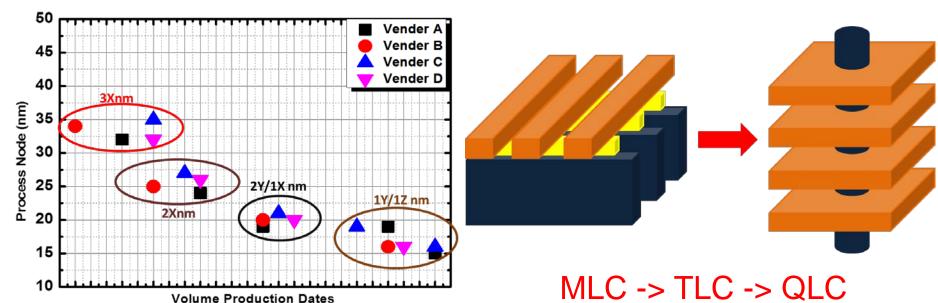

2012 2013 2015 2009 2010 2011 2014 Technology (nm) 3x 3x 3x/2x2x/1x1x/1y1y/1z 1z ECC/Signal BCH/Retry/L BCH/Retry/L Advanced Advanced **BCH BCH** BCH/Retry Processing **DPC DPC DSP DSP**

### Migration of ECC Technologies

|                          | 2009 | 2010 | 2011      | 2012               | 2013               | 2014            | 2015            |

|--------------------------|------|------|-----------|--------------------|--------------------|-----------------|-----------------|

| Technology (nm)          | 3x   | 3x   | 3x/2x     | 2x/1x              | 1x/1y              | 1y/1z           | 1z              |

| ECC/Signal<br>Processing | всн  | всн  | BCH/Retry | BCH/Retry/L<br>DPC | BCH/Retry/L<br>DPC | Advanced<br>DSP | Advanced<br>DSP |

### Migration of ECC Technologies

|                       | 2009 | 2010 | 2011      | 2012               | 2013               | 2014            | 2015            |

|-----------------------|------|------|-----------|--------------------|--------------------|-----------------|-----------------|

| Technology (nm)       | 3x   | 3x   | 3x/2x     | 2x/1x              | 1x/1y              | 1y/1z           | 1z              |

| ECC/Signal Processing | всн  | всн  | BCH/Retry | BCH/Retry/L<br>DPC | BCH/Retry/L<br>DPC | Advanced<br>DSP | Advanced<br>DSP |

- Larger chip size.

- Huge power consumption.

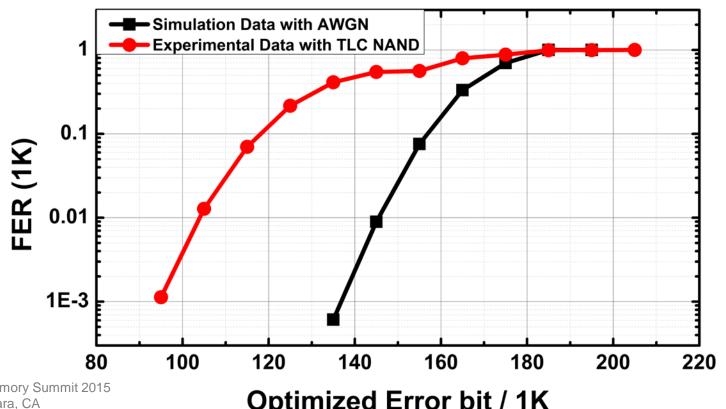

- A Gap between simulation and real NAND channel on Correction capability.

- Weak immunity to HRE.

- Complex decoding flow.

- Larger chip size.

- Huge power consumption.

- A Gap between simulation and real NAND channel on Correction capability.

- Weak immunity to HRE.

- Complex decoding flow.

### Flash Memory The Gap between NAND and Theory

**Optimized Error bit / 1K**

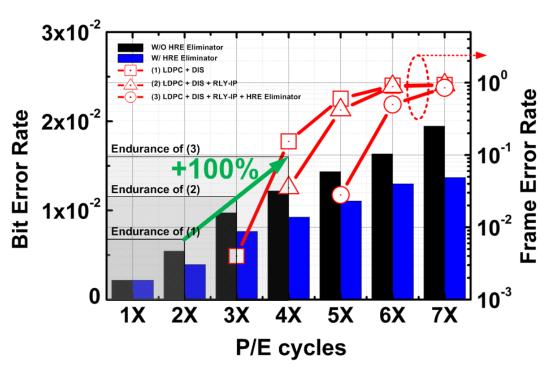

## PHISON Even We Changed to LDPC...

- Larger chip size.

- Huge power consumption.

- A Gap between simulation and real NAND channel on Correction capability.

- Weak immunity to HRE.

- Complex decoding flow.

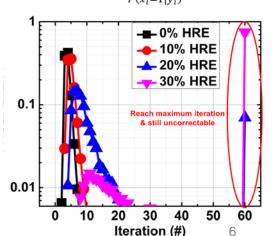

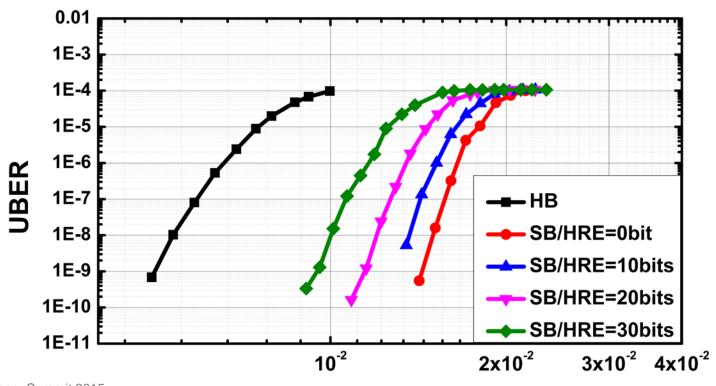

#### Weak Immunity to HRE

## Even We Changed to LDPC...

- Larger chip size.

- Huge power consumption.

- A Gap between simulation and real NAND channel on Correction capability.

- Weak immunity to HRE.

- Complex decoding flow.

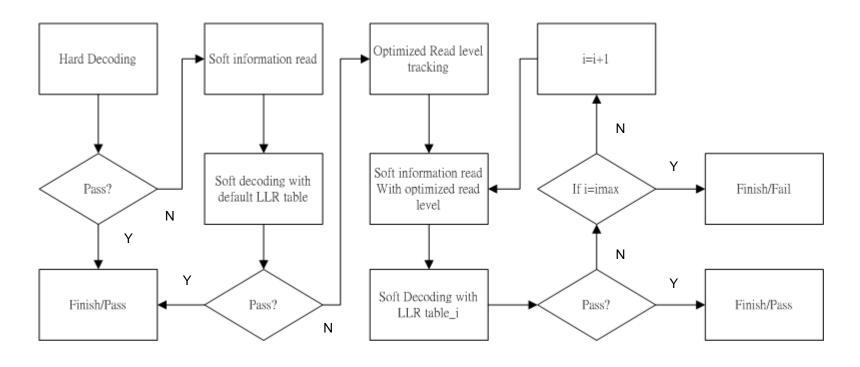

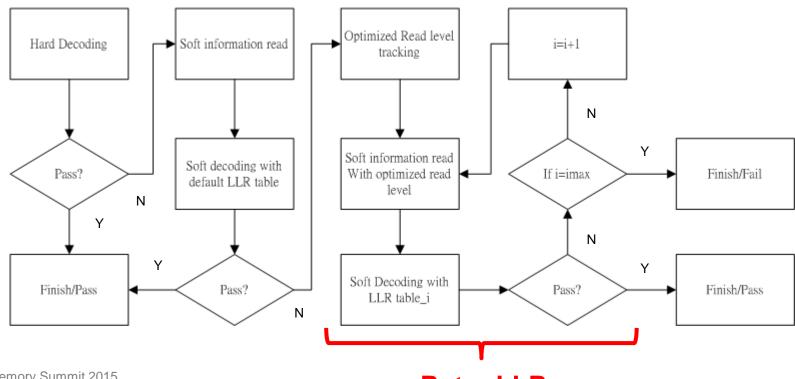

### **Complex Decoding Flow**

#### **Complex Decoding Flow**

#### Memory A Novel ECC is Proposed

- Superior correction capability then BCH and the HB of LDPC.

- Support soft decoding.

- 1/3 power consumption than BCH.

- Same gate count as BCH.

- Simple decoding flow.

- No need to use soft bit information.

- Excellent HRE immunity.

#### Summary

- A Novel ECC engine with superior correction capability is proposed for next generation NAND Flash memory.

- Digital signal processors are proposed to improve the system performance and reliability.

- Adaptive controlling technology is implemented to control the DSP/ECC/NAND/Data structure for superior reliability.