# Validation and Testing Challenges of NVMe Subsystems

Eric Lanning

Hardware Engineering Manager, SerialTek

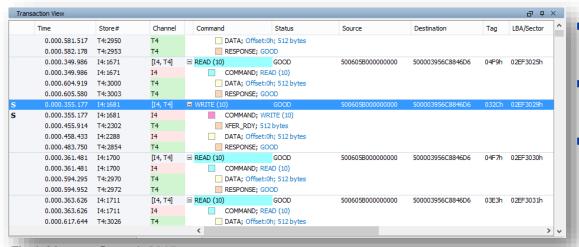

## Memory SAS/SATA Analysis

- SAS/SATA is a well-understood protocol

- Analyzers can interpret SAS/SATA protocols with relative ease

- Each frame has a type (i.e. Command, Response, Data ...)

- It is straight forward grouping frames into "transactions"

- Command frames start a transaction

- Response frames end the transaction

- Data frames are transmitted in between

Flash Memory Summit 2015 Santa Clara, CA

#### **NVMe Advantages**

- Scalable performance with low latency

- No need to convert native PCIe to SAS or SATA

- Efficient and streamlined command set

- Support for up to 64K I/O queues, with each I/O queue supporting 64K commands

- Priority associated with each I/O queue with a well-defined arbitration mechanism

- All information to complete a 4KB read request is included in the 64 byte command itself

- Support for multiple namespaces

- These features give us lower latency and higher performance, but makes it more difficult to analyze

# NVMe Validation/Testing Challenges

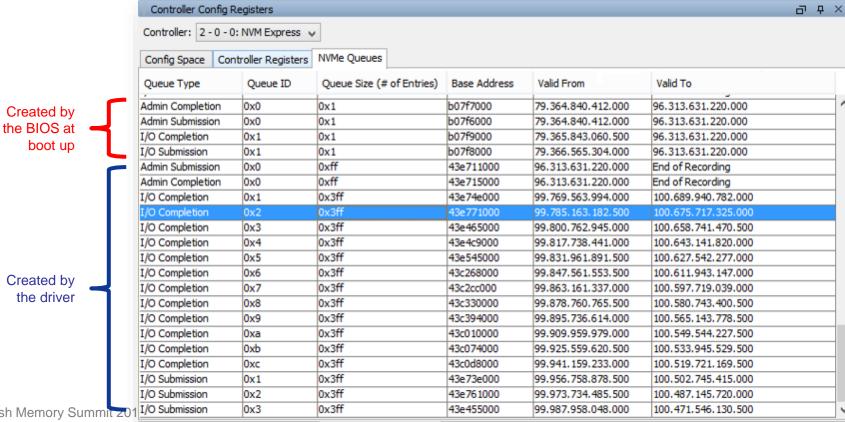

- Validating and analyzing NVMe designs is challenging

- Controller registers are addresses that are an offset of the device's BAR0/BAR1

- Commands and completions are stored in queues which occupy a range of addresses

- BIOS and driver can create and destroy queues as needed

- In order to decode, filter and trigger, analyzers need to know the BAR address, queue addresses and sizes

- This information can be entered manually, but this method can be error prone and difficult if queues are created and destroyed multiple times in the same trace

- If the initialization was captured, it can be extrapolated from the trace

- The analyzer can monitor the traffic and archive all necessary information in hardware

- The physical memory locations for data transfers are specified through pointers

#### Queue Archive Example

Flash Memory Summit 201 Santa Clara, CA

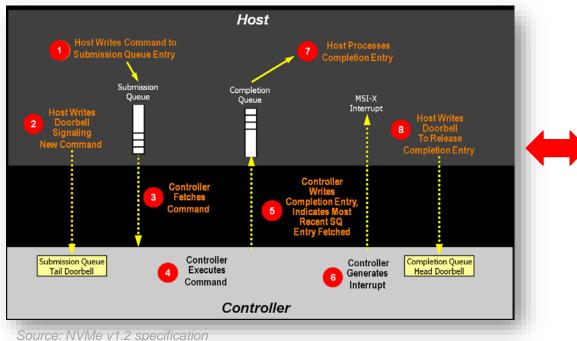

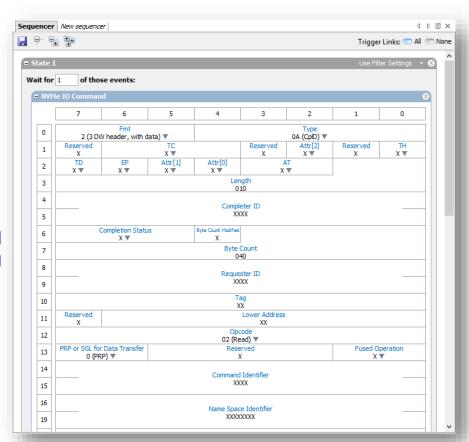

#### **NVMe Command Processing / Analyzer Decoding of Command Processing**

Flash Memory Summit 2015 Santa Clara, CA

## Filtering/Triggering Challenges

- Decoding NVMe traffic does not require the BAR0/1 address and queue address ranges real-time

- Decoding can take the information after the capture is complete and decode all of the Doorbell, Admin and I/O Commands and Completions

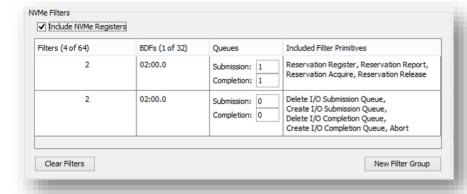

- In order to trigger and filter on commands, the BAR0/1 address and the queue address ranges need to be stored in hardware so the analyzer can act on the traffic in real-time

- Triggering on data transfers is difficult because the pointers specifying the physical memory address are dynamic and are probably not known ahead of time

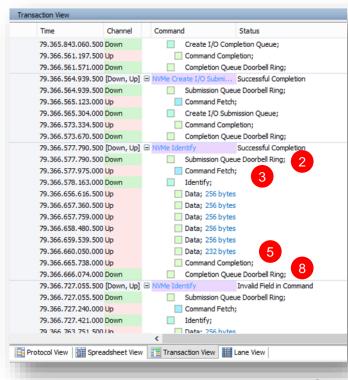

#### Filtering Example

- Filtering is also an important analyzer capability used to prevent the capturing of information that is unimportant to the user

- At 8 GT/s and multiple lanes wide the analyzer will fill its buffer in a second or two

- By using the BAR0/1 addresses and the queue address ranges, the analyzer can compare the address of Memory Write and know whether the data being fetched is command or completion

- Once it is known that the data is a command or completion, the analyzer can filter those packets depending on the command opcode

### Memory Triggering

- Triggering is a standard and important analyzer capability used to stop the capturing of a trace because of a certain event or condition (e.g. error)

- To trigger on NVMe events, analyzers have to first determine whether a TLP contains NVMe events/information

- If the address of the TLP packet is not compared against the queue address ranges, then knowing whether the data being transferred is part of an NVMe command or some other data transfer becomes a "guess"

- There is no way to distinguish between Admin and IO commands

- The size and type of the TLP are used to try and trigger on the command or completion

- This can lead to false positives

### Summary and Key Take-Aways

- Without accurate and current admin/IO queue address ranges and BAR0/1 addresses, PCIe/NVMe protocol analysis is extremely challenging

- Key analyzer filtering and triggering functions work less reliably

- This Impacts development and testing cycle and often results in product release delays

- Manual input of queue information into analyzer software can alleviate some issues but process is tedious and error-prone

- Automated discovery and capture of this information is what is required to overcome these challenges unique to NVMe protocol analysis