Hughes Metras VP Strategic Partnerships, North America Hughes.Metras@cea.fr

Luca Perniola Head of Memory Lab Luca.Perniola@cea.fr

http://www.cea.fr/cea-tech

## New Advanced Non Volatile Memory Prototyping Services

#### **Ceatech** IN A FEW PICTURES AND FIGURES

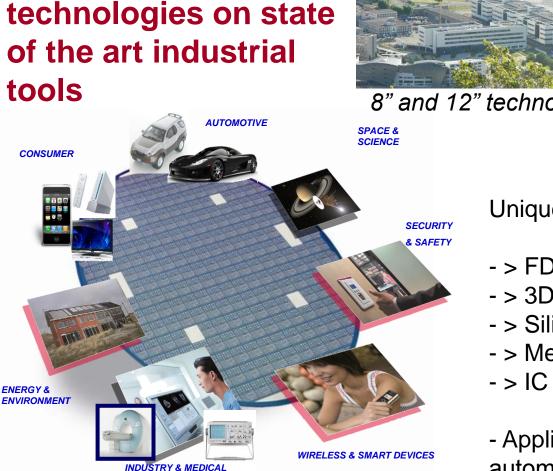

### R&D in Micro & Nano technologies on state of the art industrial tools

HEALTHCARE

1 800 researchers 1 300 on LETI payroll 300 M€ budget ~ 40 M€ CapEx 8" and 12" technology platforms ~300 patents / year Portfolio > 2,200 patents 40 start-ups

Unique capabilities for prototyping :

- > FDSOI CMOS (beyond <28 nm node)

- > 3D Integration & chip stacking

- > Silicon Photonics

- > Mems

- > IC Design

- Applications (medical devices, telco/loT, automotive, security, ....)

## A proven record of international successful partnerships

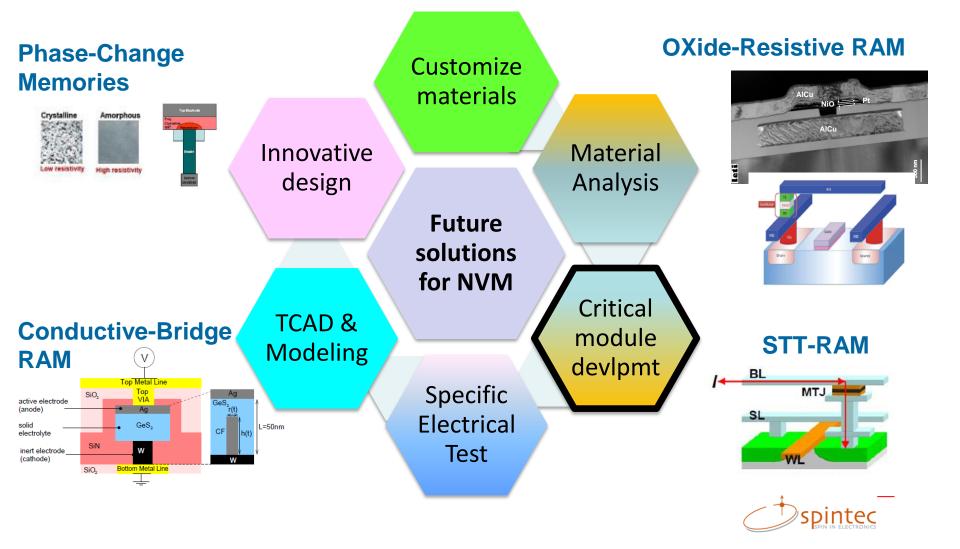

### NON VOLATILE MEMORIES VALUE CHAIN INSIDE LETI

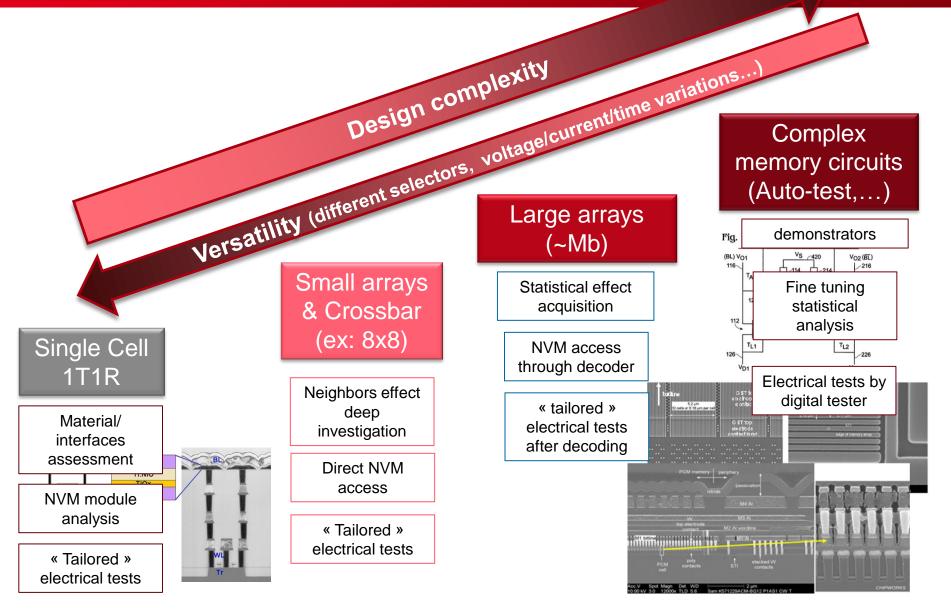

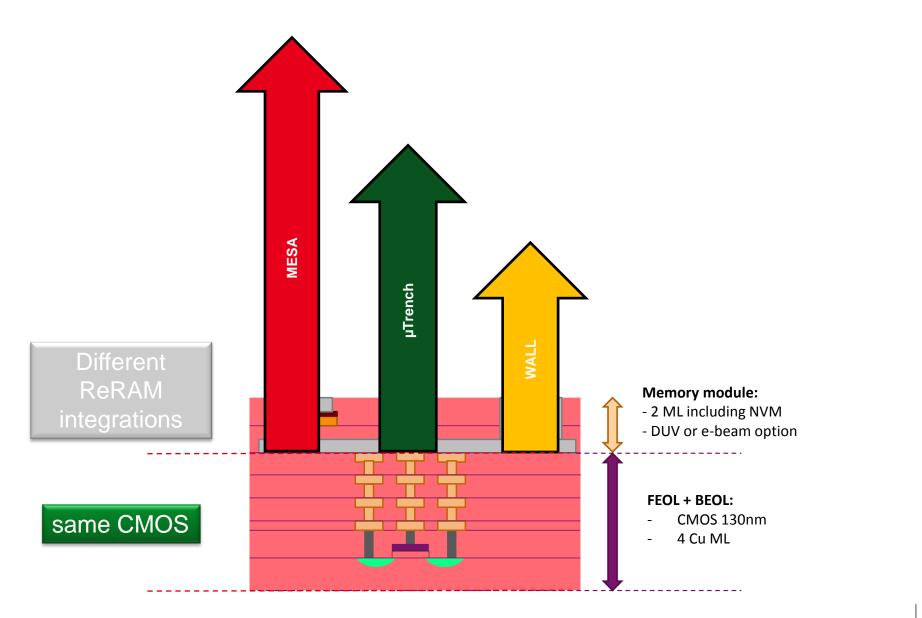

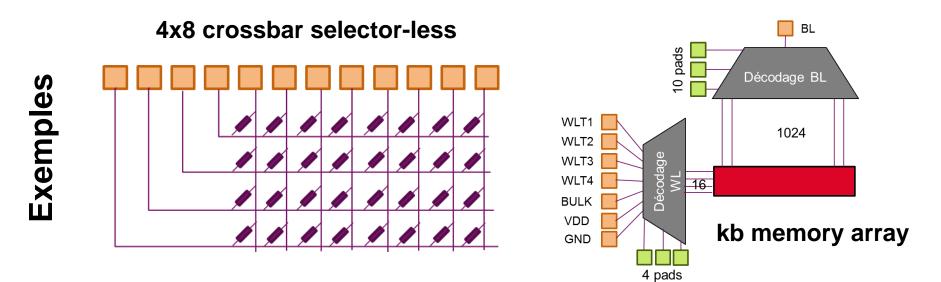

A wide tool box which enables a **customized** research with **our partners** and a **benchmark** between different technological solutions

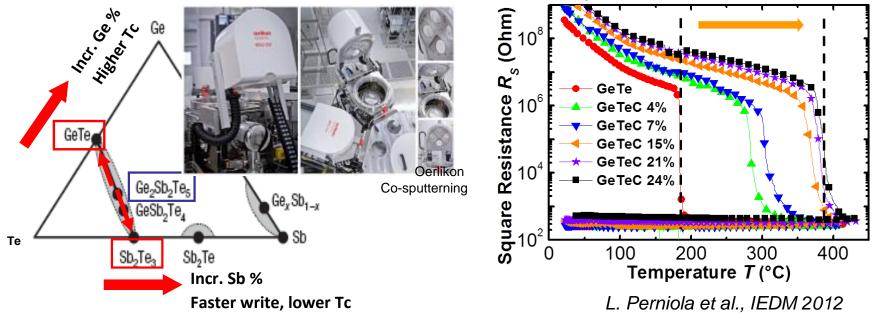

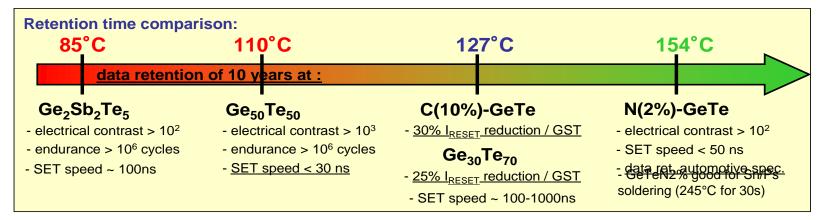

### **PCM: Memory stack Engineering**

#### for High-Temperature specs

Improving Data-retention @ High Temperature → soldering reflow & automotive specs (LETI/ST-Microelectronics collaboration)

G. Navarro et al., IEDM 2013

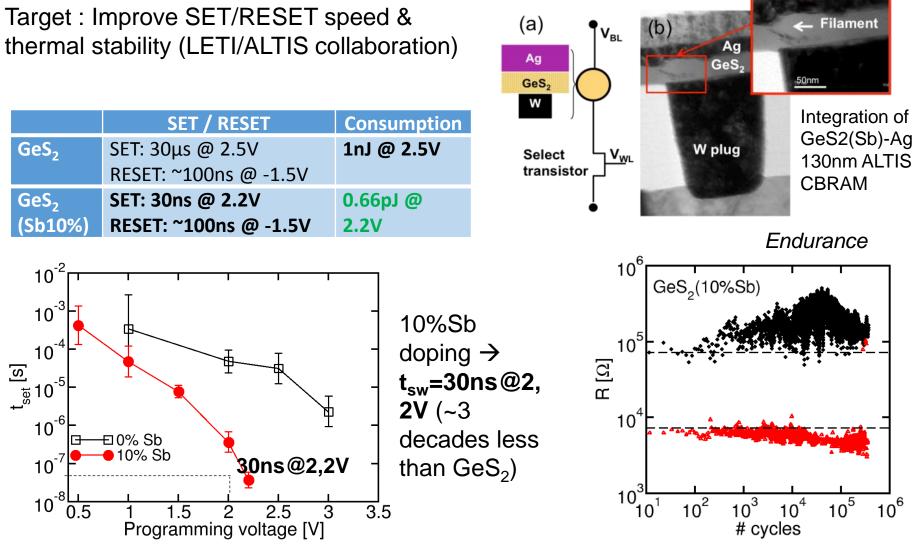

### **CBRAM: Memory stack Engineering**

### for low-power applications

E. Vianello et al., IEDM 2012

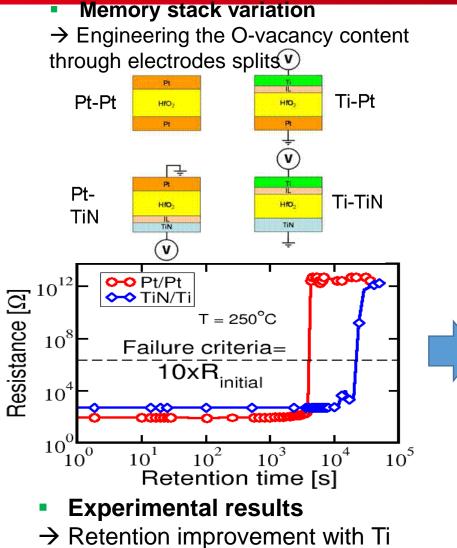

### **OxRAM: Memory stack Engineering**

# Ceatech

### for variability reduction

HfO<sub>2</sub> with an O<sub>i</sub> interstitial Ti with an O<sub>i</sub> interstitial  $\begin{array}{c}

& O_{1} \\

& O_{2} \\

& HfO_{2} \\

& HfO_{2} \\

& + tO_{2} \\

& + tO_{$

Ab initio calculations

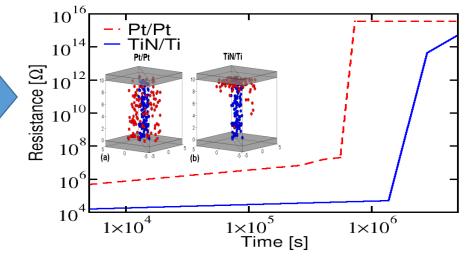

$\rightarrow$  Ti acts as an O gettering layer during filament formation. Lower concentration of V(O) around the filament

Physical device modeling

$\rightarrow$  Improved filament stability and retention due to lower V(O) concentration in the HfO2 resistive layer

*B. Traore et al., IRPS 2013 C. Cagli et al, IEDM 2011*

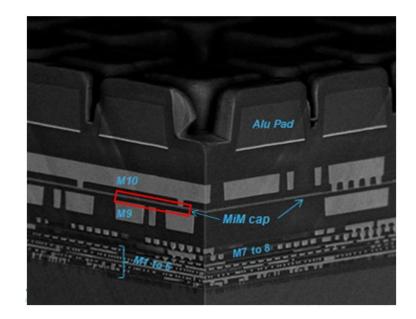

#### **OxRAM** last achievement

### → 16 kbit in ST 28 nm node test vehicle

- Back end integration (MIM 2 masks).

- Low number of process steps.

- 16 CUTs of 1kb/28 nm each are integrated into a digital testchip designed by ST

### Wafer exchange:

- Basewafers with CMOS 28 nm fabricated in ST

- LETI deposition of HfO2/Ti/TiN stack

- ST finishes BEOL up to pads

Courtesy of P. Candelier, Leti Memory Workshop 2014

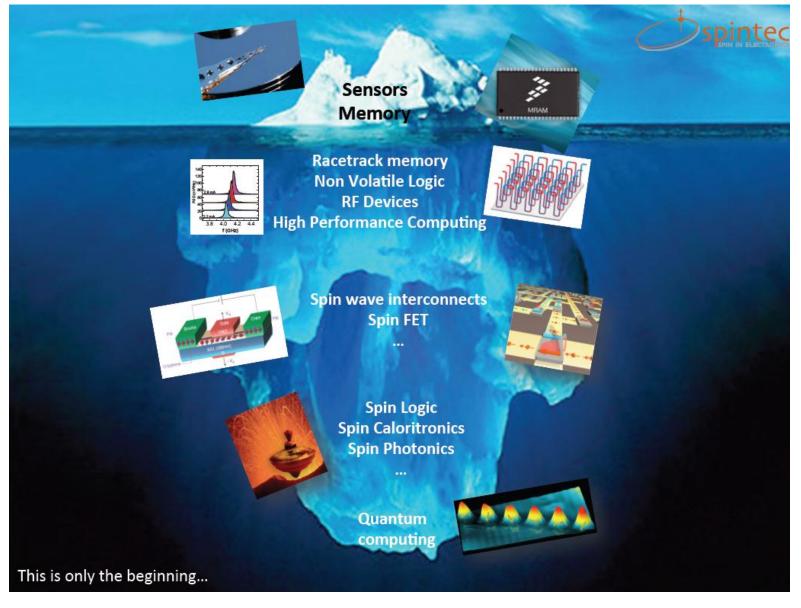

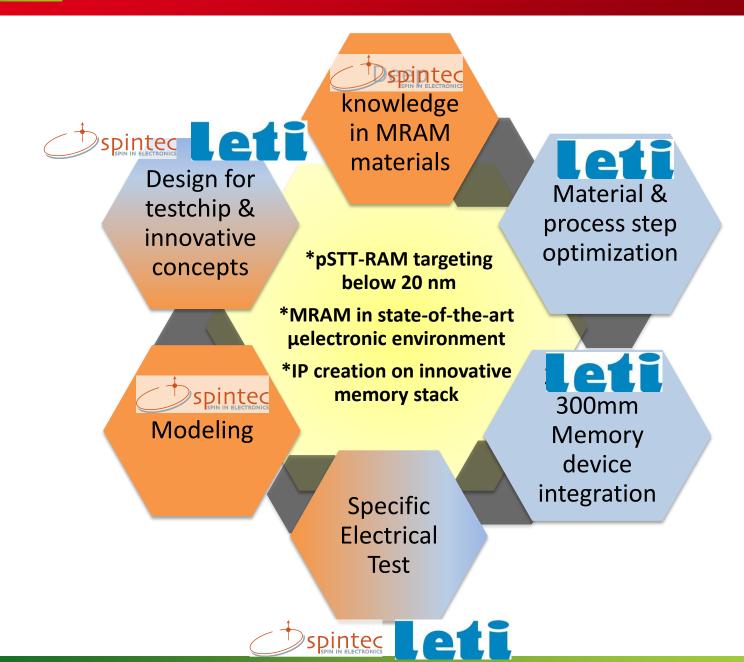

## **COOPERATION WITH SPINTEC**

## **LETI SPINTEC PARTNERSHIP**

### « MEMORY ADVANCED DEMONSTRATORS » → MAD

####

Reliable test vehicle for fast material screening for all major RRAM families (CB-OxRAM, MRAM, PCRAM)

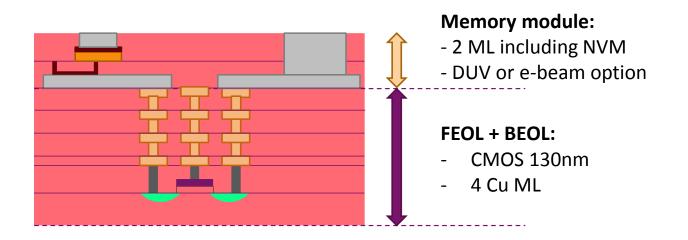

- ✓ 4 copper interconnects: possibility to make complex routing for complex design Possibility to have Mb memory arrays to accumulate statistics

- ✓ FEOL features NMOS and PMOS with high yield

- ✓ Cycle time depending on priority: down to ~9 weeks in P1

MAD integration flows tailored for OxRAM, CBRAM, MRAM and PCRAM

leti

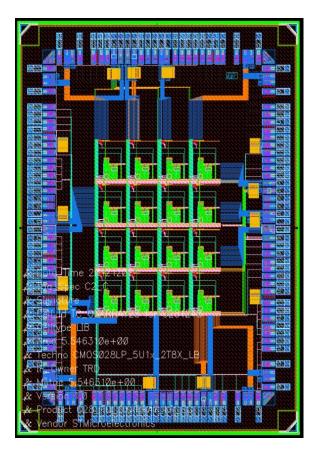

## Ceatech MAD exemples & specifications

| TECHNOLOGY:             | CMOS 130nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spec. process<br>char.: | Gate length : 130nm (drawn), 130nm (effective)Triple WellPower supply : 1. 2V for Digital, 4.6V for Analog applicationMultiple Vt transistor offering (Low Power, Analog)Threshold voltages (for 2 families above) : VTN = 700/697mV, VTP = 590/626mVIsat (for 2 families above) : TN : 280/658uA/um; TP : 104/333uA/um4 Copper metal layers in standardFluorinated SiO2 Inter Metal dielectrics2 specific implant levels : NDRIFT & PDRIFTDouble gate oxide for analog features |

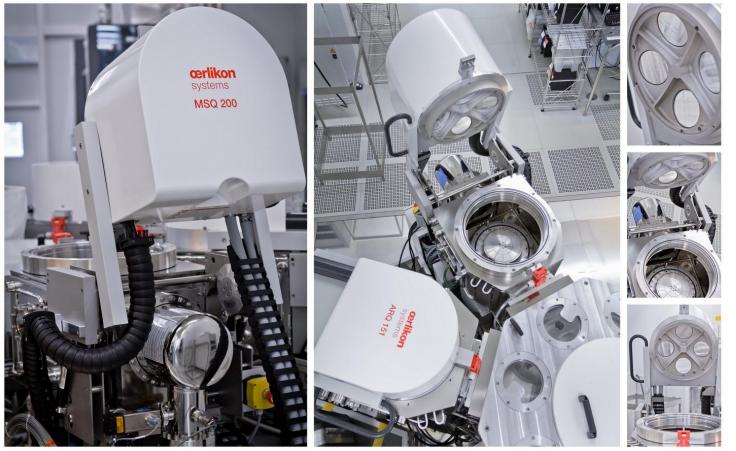

# Ceatech Oerlikon Cluster Line 200mm (CLN200)

- Tool delivered & qualified end of october '11 @LETI Courtesy of V.Baret LETI

- Material engineering for memories applications (CBRAM, PCRAM, OXRAM)

- Co-sputerring capability

- Standard planar PVD module for capping, electrodes …

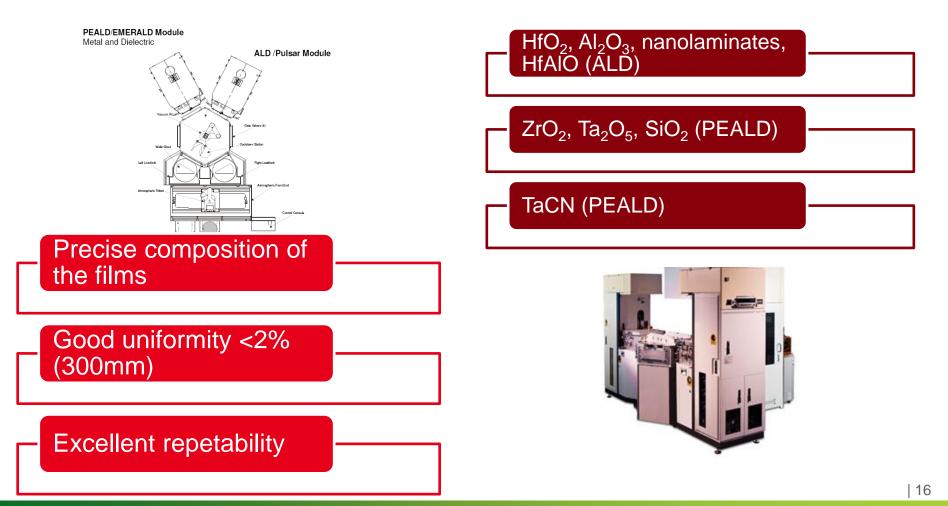

Ceatech 300 mm ALD & PEALD tools for OxRAM

#### • Equipment cluster ASM POLYGON1 – 2 deposition reactors

- ALD reactor (Atomic Layer Deposition)

- PEALD reactor (Plasma Enhanced Atomic Layer Deposition)

- Capability 300mm wafers wafers 200mm : samples on adaptors

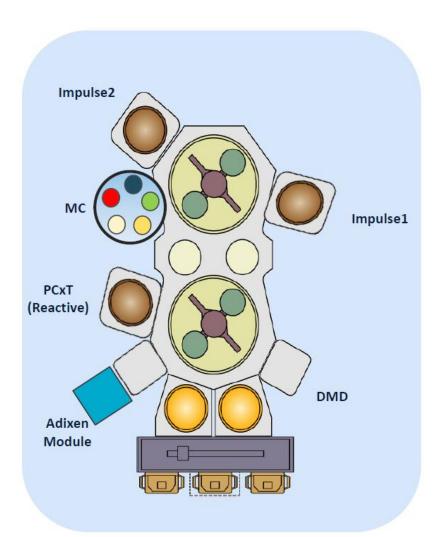

## **300 mm PVD Endura platform**

leatech

### Tool configuration

- ✓ 1 Degassing module (DMD) up to 400°C

- ✓ 1 Preclean system (ICP soft etch)

- ✓ 1 Multi-Cathode chamber (5 cathodes with RF, DC, pDC generators) – O2, N2 reactive processes. Up to 3 target co-PVD

- ✓ 2 pDC chambers (Impulse) O2, N2 reactive processes

- Vacuum transfer module for plugging the Adixen vacuum carrier

### <u>Objectives</u>

Conventional Impulse PVD chambers  $\rightarrow$  electrodes & fixed composition memory element.

300mm CoSputtering chamber for memory material engineering and flexibility

- → Composition fine tuning, material screening

- → Cost Of Ownership : smaller targets (easier to manufacture), longer life time for desired targeted compo, etc.

THANKS! QUESTIONS?

www.cea.fr