# Building a Controller That Can Handle Any Type of Flash

### Brent Przybus – Sr. Director eASIC Corporation

Flash Memory Summit 2015 Santa Clara, CA

# A Changing Flash Enabled Landscape

- Flash Is Needed for Enterprise Storage

- Flash is Evolving Rapidly Due to Demand

- The Controller Architecture Must Evolve

# Expanding Role of Flash in Enterprise Storage

- Application and Data Velocity is Increasing Exponentially

- Flash based storage is faster than disk

- But this speed is not needed across the spectrum

- Flash is More Reliable Than Ever

- Suitable for broad use in the data center

- Provided you are using the right controller

- Transitioning to Scale-out Architecture

- Better suited for data centers

- Better support for different data types

- Opportunity to Redefine the Controller

- Support flexible hardware / software partitioning

- Support for virtualization

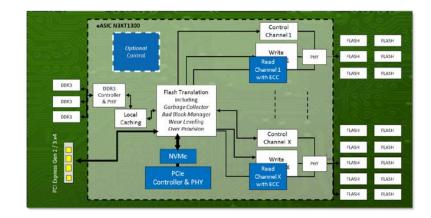

- Low Power

- <5 Watts</li>

- Flash Memory Interface Speed

- ONFI 4 800MT/s, Multiple instances

- Host side Flexibility

- PCIe Gen3 x8/16 or SAS/SATA or Ethernet...

- Fast, Flexible FTL Memory

- DDR4, DDR3, LPDDR, etc.

- Flexible Processor Support

- FTL Control and Management

- Efficient ECC

- Multiple Instances of BCH or LDPC

- Independent Channel Support

- Flexible Multiple Channel DMA Support

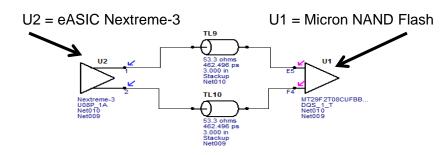

### eASIC Nextreme-3 ONFI Support

| Capability                | ONFI Requirement | eASIC Nextreme-3<br>eIO Spec |

|---------------------------|------------------|------------------------------|

| Signaling Standard        | 1.2V/1.8V SSTL   | $\checkmark$                 |

| Data rates (MT/s)         |                  |                              |

| ONFI 3.0/3.2              | 400, 533         | $\checkmark$                 |

| ONFI 4.0                  | 667, 800         | ✓                            |

| ZQ Calibration            |                  |                              |

| Driver impedance (ohms)   | 25, 35, 50       | ✓                            |

| ODT (ohms)                | 50, 75, 100, 150 | ✓                            |

| I/O Leakage Currents (uA) | +/- 10           | $\checkmark$                 |

| Data Rate | Load Count | Operation    |

|-----------|------------|--------------|

| 533 MT/s  | 16         | Read/Write 🗸 |

| 667 MT/s  | 8          | Read/Write 🗸 |

| 800 MT/s  | 8          | Read/Write ✓ |

eASIC Nextreme-3 eIO NV-DDR3 Load Analysis

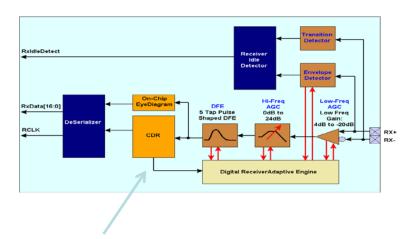

## eASIC MGIO PCIe with SRIS

| Requirement                      | SRIS Requirement              | MGIO Spec                     |

|----------------------------------|-------------------------------|-------------------------------|

| Clock tolerance capability (ppm) | 5600                          | 5600                          |

| RX-CDR PLL (Type; BW)            |                               |                               |

| Gen-2                            | 2 <sup>nd</sup> order; 5 MHz  | 2 <sup>nd</sup> order; 5 MHz  |

| Gen-3                            | 2 <sup>nd</sup> order; 10 MHz | 2 <sup>nd</sup> order; 10 MHz |

| PCS (Elastic Buffer) Req.        |                               |                               |

| Gen-2                            | 1 SO-set* / 154 symbols       | Supported                     |

| Gen-3                            | 1 SO-set* / 38 symbols        | Supported                     |

- RX-CDR implemented with fully independent PLL (2nd order high-pass function)

- Allows much faster tracking of phase variation on incoming data

- Meets the 5600 ppm SRIS-required spread-spectrum tracking capability

#### NAND Flash Process Roadmaps (for Volume Production)

|                 | 2011 2012 | 2013 2014 | 2015 2016 202 | 17       |

|-----------------|-----------|-----------|---------------|----------|

| IM Flash        | 20nm      | 16nm      | 10-12nm       | 2D       |

|                 | 201111    | Tour      | Gen 1 Gen 2   | 3D       |

| Samsung         | 21nm      | 16nm      | 10-12nm       |          |

|                 | 2100      | 24L 32L   | Gen 3 (48L)   | 3D       |

| SK Hynix        | 20nm      | 16nm      | 10-12nm       | 2D       |

|                 | 201111    | TOUL      | Gen 1 Gen 2   | 3D       |

| Toshiba/SanDisk | 19nm      | 15nm      | 10-12nm       |          |

|                 | 1900      | 1500      | Gen 1 G       | ien 2 3D |

#### **DRAM Process Roadmaps (for Volume Production)**

|          | 2011 2012 2013 | 2014 2015 2016 2017 |

|----------|----------------|---------------------|

| Micron   | <30nm          | <20nm               |

| Samsung  | <30nm          | <20nm               |

| SK Hynix | <30nm          | <20nm               |

Note: What defines a process "generation" and the start of "volume" production varies from company to company, and may be influenced by marketing embelishments, so these points of transition should be used only as very general guidelines.

Sources: Companies, conference reports, IC Insights

http://evertiq.com/design/35204

Flash Memory Summit 2015 Santa Clara, CA

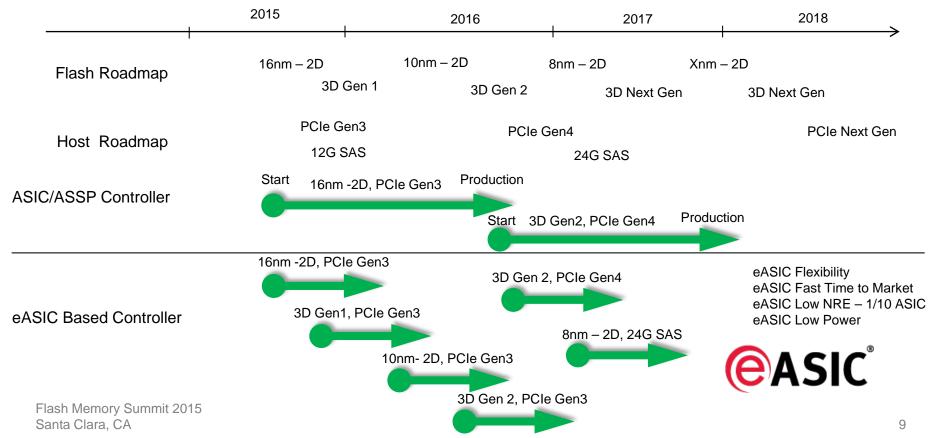

### • Flash Controller Trend

- Constant Change

- Faster/Lower Latency

- Faster, Denser, Cheaper

## **Avoiding Obsolescence**

# Flash Memory Comparing Controller Options

| Requirements          | FPGA                      | ASIC/ASSP       | eASIC Platform               |

|-----------------------|---------------------------|-----------------|------------------------------|

| Host Side Flexibility | Any Host                  | Fixed Interface | Any Host                     |

| Flash Interface       | Flexible                  | Fixed           | ONFI 4 at 800MT/s            |

| Power Consumption     | 12 Watts                  | 2 Watts         | 5 Watts                      |

| Ability to Customize  | Yes                       | No              | Yes                          |

| Time to Market        | RTL to Proto – Very Short | 12 + Months     | RTL to Proto – 7 weeks       |

| DDR Memory Speeds     | DDR4 2.6Gbps              | Fixed           | DDR4 2.1Gbps<br>DDR3 2.1Gbps |

| Development Cost      | No NRE                    | Millions in NRE | 1/10 ASIC NRE                |

| Unit Price            | Highest                   | Lowest          | Low                          |

# Top 5 Things to Ask About Your Controller Architecture

- 1. Does it support the latest Flash technology.... Will it keep up?

- 2. Are your competitors using the same controller?

- 3. Does it deliver the performance per watt you need?

- 4. Does the same controller multiple host interfaces?

- 5. How fast is the Flash interface?

- Flash is Changing Storage

- Flash is Evolving Fast to Deliver More

- You Need a Flexible Controller that Keeps Up