3D XP: What the Hell?!!

Dave Eggleston

# Making Sense of 3D XP

- WHY are you surprised?

- WHAT is it (really)?

- XP Array Limitations: <u>The Litho Problem</u>

- HOW will it be used?

- 3D XP <u>strengths & weaknesses</u>

## **Leading-Edge Technology Status**

|                             |                       | Source: S. DeBoer; Micron Analyst Day, Feb 2015                                                                                                                                                          |

|-----------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM                        | 1Xnm DRAM             | <ul> <li>Continued strong progress for 20nm yield at<br/>Hiroshima and Inotera facilities</li> <li>1Xnm development underway in Hiroshima and<br/>1Y/1Znm in Boise</li> </ul>                            |

| NAND                        | 3D NAND               | <ul> <li>16nm TLC NAND now ramping in Singapore</li> <li>Micron 1st generation 3D NAND on track for production in Singapore mid 2015</li> <li>Second generation under development in Boise</li> </ul>    |

| Package<br>Technology       | Hybrid<br>Memory Cube | <ul> <li>3D NAND package technology continues to mature, currently manufacturing HMC generation 2</li> <li>R&amp;D focus on HMC generation 3 enablement for even higher density and bandwidth</li> </ul> |

| New<br>Memory<br>Technology | Cross-point memory    | <ul> <li>Multiple paths under active development for storage class memory enablement</li> <li>Targeting 2015 and 2017 for manufacturing introductions of next new memory technologies</li> </ul>         |

Flash Memory Summit 2015 Santa Clara, CA 12 Images are not to scale

February 11, 2015

©2015 Micron Technology, Inc.

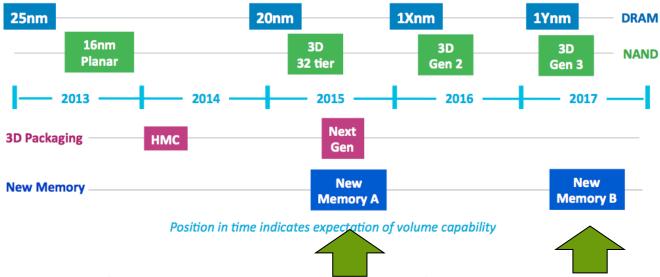

#### **Innovation Roadmap**

Source: S. DeBoer; Micron Analyst Day, Feb 2015

- Increased focus on DRAM technology position driving faster introduction cadence

- Enable volume 3D NAND manufacturing capability through 2015

- 3D NAND packaging technology enablement for multiple differentiated opportunities

- Establish disruptive new memory technology and position for ramp in 2016

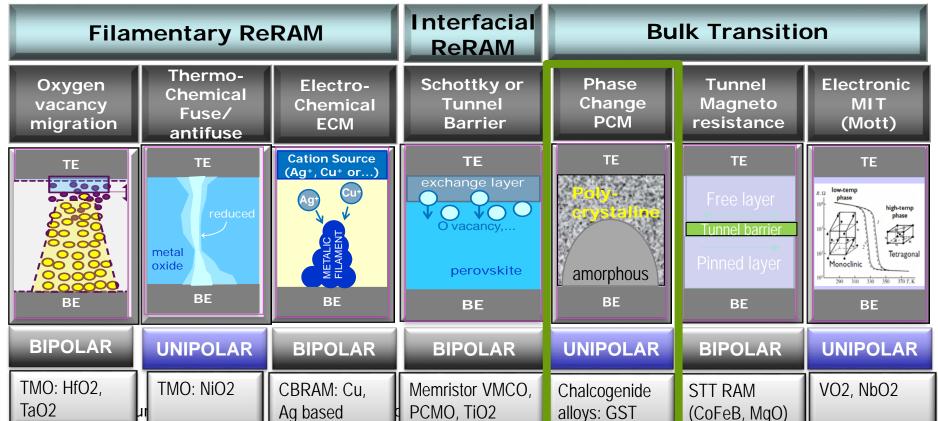

# **Switching Mechanisms**

Source: M. Jurczak, imec, ISSCC 2015 Memory Forum

## What is 3D XP?

Source: Intuitive Cognition Consulting estimates

### **ST-MRAM**

## <u>PCMS</u>

### ReRAM

## 3D XP is *NOT* ST-MRAM because:

**DRAM**

- Can't build ST-MRAM in a XP array (1T-1R)

- Can't achieve 128Gb with ST-MRAM (30F²)

- ST-MRAM more expensive than DRAM

Santa Clara, CA

Flash Memory Summit 2015

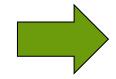

### Fast Latency Slow

Long Endurance Short

Big/\$\$\$\$ Cell Size/Cost Small/\$

## 3D XP is *probably NOT* ReRAM because:

- ReRAM Latency is too slow for application

- ReRAM endurance may be too short for the application

- ReRAM is much more likely New Memory B (Cost focused)

# Crosspoint resistive memory

Source: R. Shenoy, IBM, IMW May 2013

Ref: D. Eggleston, Flash Memory Summit 2011

Unity Semiconductor 2 layer Conductive Metal Oxide RRAM

PCMS

Ref: D. Kau, IEDM 2009

Intel/Numonyx 64Mb PCM+OTS selector

Ref: T-Y. Liu, ISSCC 2013

Sandisk/Toshiba 32Gb 2 layer MeOx ReRAM crosspoint in 24nm technology

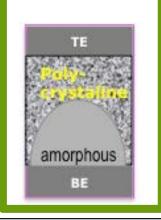

3D multilayer stacked crosspoint arrays → path to low cost memory

WRONG!

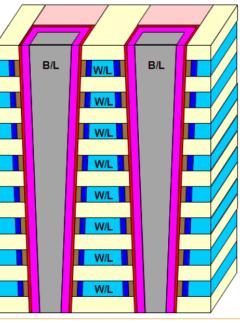

# XP Arrays: The Litho Problem

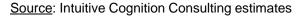

N = 4 XP layers N+1 = 5 masking steps

Cell size of 4F<sup>2</sup> Effective cell size 1F<sup>2</sup>

- XP array with shared layers requires multiple masking steps:

- N+1 masking steps to form WL/BL

- i.e. 4 XP layers requires a minimum of 5 masking steps

- □ XP cell size 4F² determined by WL/BL lithography:

- To achieve sub 20nm F requires triple or quad critical layer patterning

- i.e. 4 XP layers →5 critical masking steps → x4 quad patterning → 20 times through the stepper at sub 20nm!!!

- □XP arrays will <u>never</u> be the lowest cost memory solution!

Flash Memory Summit 2015 Santa Clara, CA

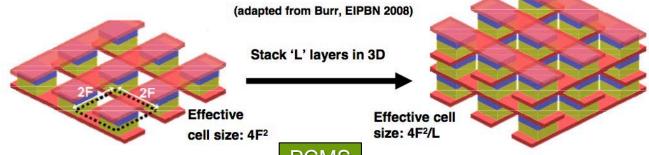

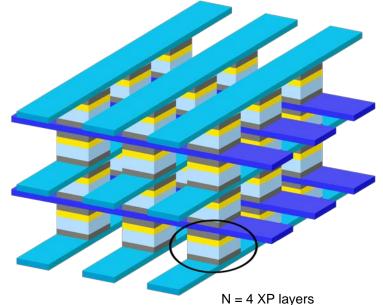

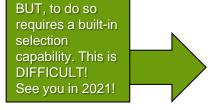

#### Planar CMOx™

**Bit Line**

#### Vertical CMOx™

Reuse of the 3D NAND architecture and processing is the way forward for lowest cost RRAM.

Flash Memory Summit 2015 Santa Clara, CA

#### **Current Major Costs of Planar CMOx™:**

- · Multiple immersion patterning or EUV lithography

- Fine line interconnect very challenging

#### Vertical CMOx™ (VXPA):

- Extension of vertical NAND

- Low cost lithography

- Fine line interconnect not required

- Earlier, Cost effective option

(NO EUV Required)

**Vertical ReRAM (VRRAM)**

Source: T. Liu, Sandisk, IMW May 2013

- No. of critical masks is not increasing with added memory layers

- Multiple layers are formed at the same time

- Challenging to integrate the selector self-rectifying cell needed

#### Reference:

S. Kim, LETI Memory Workshop 2012

I. G. Baek et al., IEDM 2011

H. S. Yoon et al., VLSI 2009

# But WHAT 3D XP is doesn't really matter...

...HOW will 3D XP be used?

Flash Memory Summit 2015 Santa Clara, CA

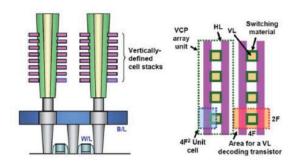

## How 3D XP will be used

Source: The Platform, "Intel Lets Slip Broadwell, Skylake Xeon Chip Specs", May 2015

## Purley: Biggest Platform Advancement Since Nehalem

PERFORMANCE FOR RANGE OF WORKLOADS

- · Better performance/Watt

- · 1.5X memory bandwidth

- AVX-512 new instructions

- · Up To 4X capacity & lower cost than DRAM

- 500X faster than NAND

- Persistent data

memory in Purley server platform.

- 1/10G Ethernet

- 100G OmniPath™

- QuickAssist™ encryption and compression offloads

- Skylake + FPGA

- · Cannonlake graphics & media transcode

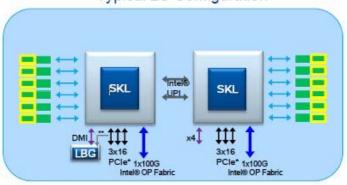

## How 3D XP will be used

### 2S Purley Platform Configuration Example

#### Typical 2S Configuration

Platform Ingredient Options

Fabric: Storm Lake Integrated, Storm Lake PCIe\* card

Storage: SATA: Downieville, SATA: Youngsville, PCIe\*: Coldstream, PCIe\* Cliffdale

Software: Analytics, Efficiency, Performance, Secure Access, Tools

Networking: Lewisburg as 4x10GbE Integrated Network Solution with PHY, Fortville 4x10/2x40GbE (Controller), Sageville 2x10GBASE-T (Controller), Springville (1x1GBASE-T), Powerville (4x1GBASE-T)

Core Ingredients: Coppervale 10GBASE-T, Jacksonville GbE PHY

Accelerators: Intel® QuickAssist Accelerator Technology with Compression and Encryption, Lewisburg can also be used as PCIe\* add-in card in end point mode

Intel® Xeon Phi™ Product Family: Knights Corner/Landing Coprocessors and Processors

FW/Bios: Manageability, Node Manager, Intel® RSTe, ME11, Intel® Trusted Execution Technology and Intel® Platform Protection Technology with Boot Guard

"Apache Pass" DDR4 **DIMMs** supported in Purley.

**DDR4 DIMMs** DDR4/Apache Pass

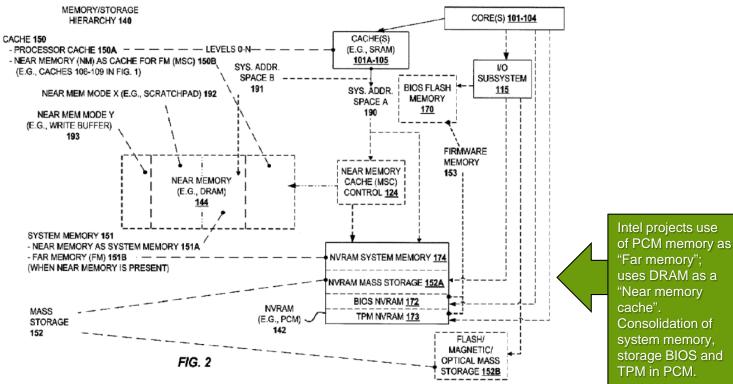

# Intel Near/Far Memory Hierarchy

uses DRAM as a "Near memory Consolidation of system memory, storage BIOS and TPM in PCM.

Source: Intel US patent, R. Ramanujan et al, "Dynamic partial power down of memory-side cache in a 2-level memory hierarchy" US 20140304475 A1

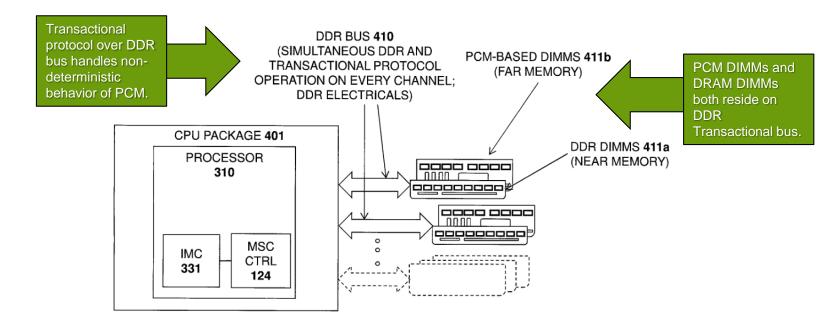

## Intel PCM-Based DIMMs

Fig. 4G

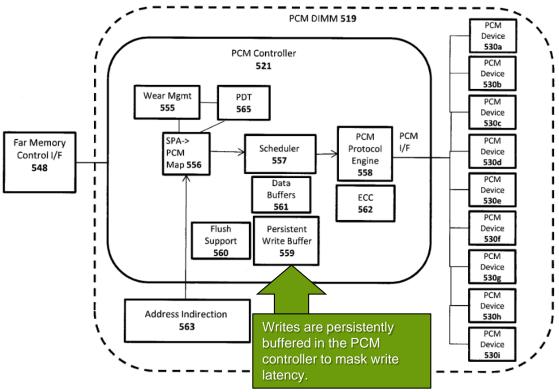

# Intel PCM-Based DIMM Controller

FIG. 5E

<u>Source:</u> Intel US patent, R. Ramanujan et al, "Dynamic partial power down of memory-side cache in a 2-level memory hierarchy" US 20140304475 A1

# Speculation on Intel usage of 3D XP

Source: Intuitive Cognition Consulting estimates

# Server memory DIMMs:

- In-memory compute, Real time analytics applications

- Coincide with Purley platform launch in 2017

- DDR4 bus with transactional protocol (non-JEDEC)

- Read is PCM native latency (50-200ns)

- Write is buffered in PCM controller (latency hidden)

- 100's of GBs per DIMM (3x-4x DRAM capacity/DIMM)

- Trouble meeting 12W power window (PCM energy)

# Strengths/Weaknesses 3D XP

Source: Intuitive Cognition Consulting estimates

## Strengths

- Brand new memory type brings new capabilities

- Semi-Persistent memory arrives!

- Server memory target competes with DRAM cost

- Read/write performance near full DRAM speed

- Full system approach

## Weaknesses

- 3D XP cost will be high:

- DRAM \$8/GB, 3D XP \$4/GB, 3D NAND \$0.2/GB

- Sole sourced from Intel/Micron

- Requires major hardware and software changes

- >12W Power requires server thermal re-design

- Non-JEDEC standardized DDR4 transactional interface

# Making Sense of 3D XP

- WHY are you surprised?

- WHAT is it (really)?

- XP Array Limitations: <u>The Litho Problem</u>

- HOW will it be used?

- 3D XP strengths & weaknesses