# Scalable Flash Architectures Meet "Instant On"

Jackson Huang Vice President Segment and Ecosystem Marketing Cypress Aug 13, 2015

Flash Memory Summit 2015 Santa Clara, CA

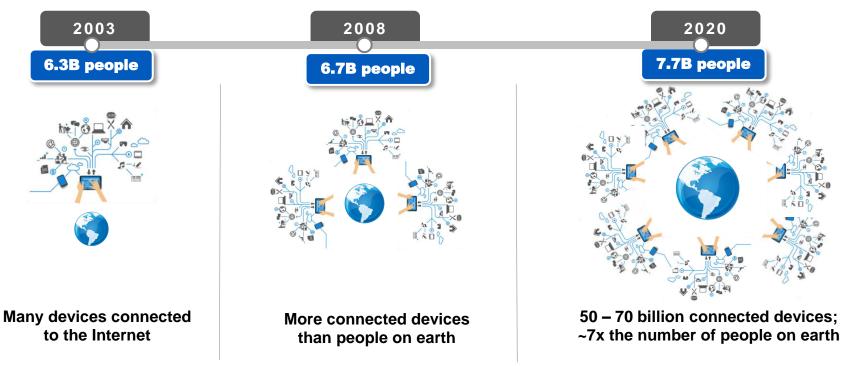

### Explosion of More Intelligent and Connected Devices

**Flash** Memory

In 2013, there were 23M connected cars. In 2015, 20% of vehicles sold will be connected.

By 2020, there will be 152M connected cars sold globally. Source: IHS

### **Explosion of Connected Autos**

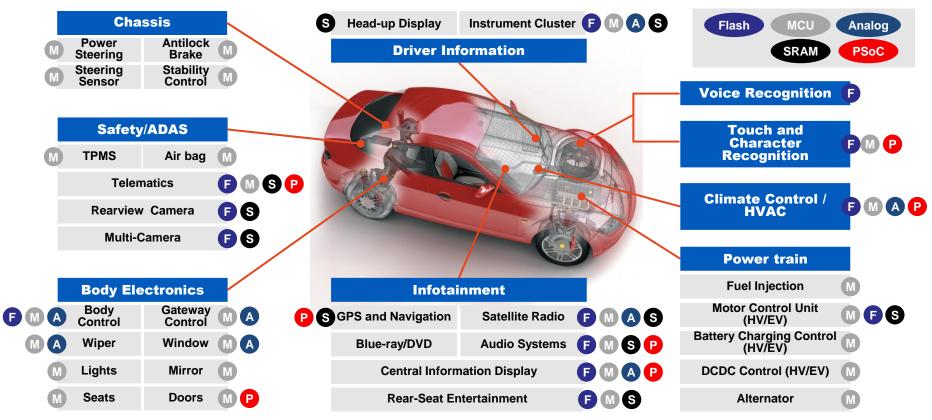

Cypress + Spansion = No. 3 in Automotive Memory & MCUs

**Flash** Memory

SUMMIT

### **High Performance Automotive Requirements**

**Auto-Cluster**

TFT replacing mechanical Instant on

Traditional architecture insufficient Fast boot Graphics recall

Infotainment

Larger screen and higher resolution Complex graphics Motion graphics More instant on functionality

Flash NOR Flash for Boot, Code, and Graphics

Flash Memory Summit 2015 Santa Clara, CA

## **Cypress HyperBus™: A Better Solution**

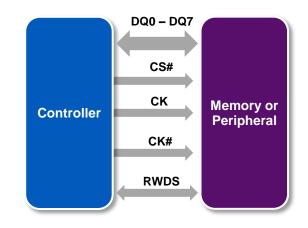

#### HyperBus<sup>™</sup> Interface

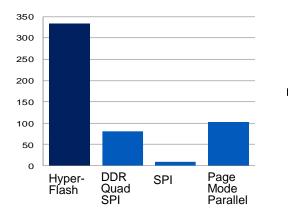

A high-bandwidth, 12-signal interface that transfers information over 8 I/O signals at double data rate (DDR), delivering up to 333 MBps

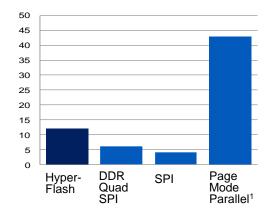

HyperFlash<sup>™</sup> NOR Flash Memory combines the industry's **highest Read Bandwidth...**

With one of the lowest-pin-counts available...

HyperBus<sup>™</sup> Interface (12 pins)

#### Read Bandwidth (MBps)

#### Pins for Data Transfer (# of Pins)

range of -40°C to +125°C

Industry's fastest NOR Flash Memory for the highest-performance systems

| Problems<br>Designers Face                                                | HyperFlash <sup>™</sup> Solves These By:                                                                               |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| The highest-performance<br>systems for fast boot with<br>graphics display | A DDR mode with up to 166-MHz<br>with 333-MBps Read Bandwidth                                                          |

| Low-pin-count interfaces to reduce system cost                            | A standard 24-ball package sharing<br>a common footprint with Quad SPI<br>and Dual Quad SPI simplifies board<br>layout |

| They must have high system reliability                                    | On-chip ECC to provide a FIT rate <0.1 FIT per device                                                                  |

| High temperature ranges                                                   | An extended operating temperature                                                                                      |

To enable demanding highperformance systems

#### Example: Automotive Instrument Cluster

## HyperFlash<sup>™</sup> vs. Traditional Flash

| Feature                                | S26KS Family    | 2 x S25FS Family | S25FS Family         | SPI                       |

|----------------------------------------|-----------------|------------------|----------------------|---------------------------|

| Interface                              | HyperBus        | 2 x Quad SPI     | Quad SPI             | Quad SPI                  |

| I/O Pin Count                          | 8               | 8                | 4                    | 4                         |

| Clock Rate (DDR)                       | 166 MHz         | 80 MHz           | 80 MHz               | 54 -66MHz                 |

| Read DDR Bandwidth (max)               | 333 MBps        | 160 MBps         | 80 MBps <sup>1</sup> | 54 - 66 MBps <sup>1</sup> |

| Program Time (512B) <sup>2</sup>       | 0.475 ms        | 0.475 ms         | 0.475 ms             | 1.0 ms <sup>3</sup>       |

| Sector Erase Time (256KB) <sup>2</sup> | 930 ms          | 930 ms           | 930 ms               | 1400 ms <sup>4</sup>      |

| Chip Erase Time <sup>2</sup>           | 110 s           | 120 s            | 120 s                | 240 s                     |

| Temperature Range                      | -40°C to +125°C | -40°C to +105°C  | -40°C to +105°C      | -40°C to +85°C            |

|                                        | Best            | Better           | Good                 | Ok                        |

Faster Boot, Bigger Display, Higher Resolution, Fancier Graphics, Smoother Motion

<sup>1</sup> Calculated using DDR clock rate

h Memory

Fla

$^2$  Conditions: 25°C and V  $_{CC}$  3.0 V, 100k minimum endurance

<sup>3</sup> Parts do not support 512B Programming. Program time is calculated using two 256B Program operations.

<sup>4</sup> Parts do not support 256KB Sector Erase. Erase time is calculated using four 64KB Sector Erase operations.