## Fully Integrated SSD-NAND Characterization Flow

### R. Micheloni, A. Marelli, L. Crippa, A. Aldarese PMC-Sierra L. Zuolo, C. Zambelli, P. Olivo Università di Ferrara

# NAND reliability & read oversampling

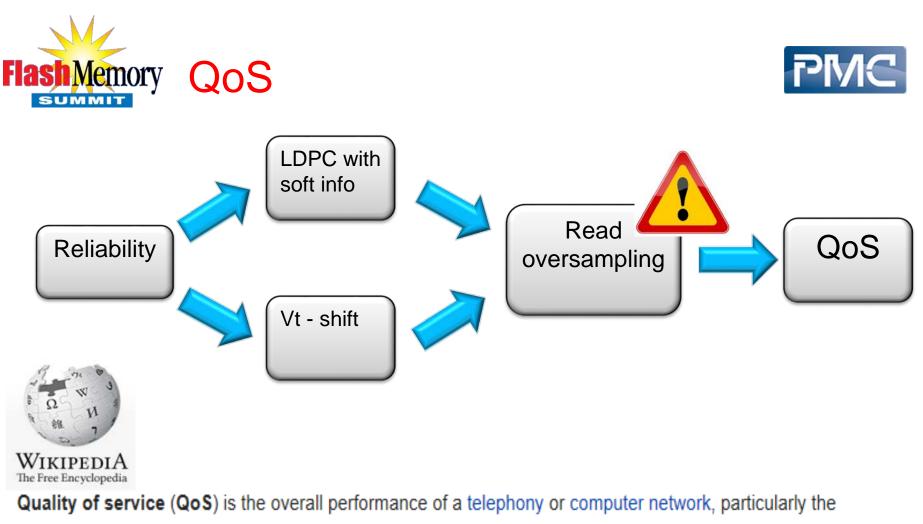

- NAND process technology shrink and multi-bit per cell storage reduce \$/GB but increase NAND raw BER

- Vt-shift (Read Retry) techniques and LDPC ECC are well known ways to limit BER growth

- Vt-shift and soft LDPC require read oversampling and they may impact SSD's QoS

- NAND silicon characterization data can be coupled to an SSD simulator to predict QoS

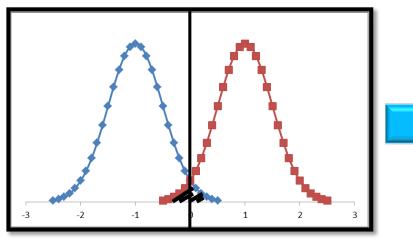

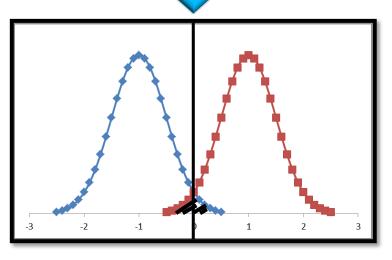

### Flash Memory Vt-shift Technique

- During life, Vt distributions move

- Vt-shift is used to re-center the read reference voltage

- Number of Vt-shift combinations is huge

- Finding the right combination can take a long long time -> QoS degradation

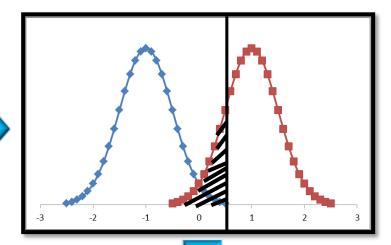

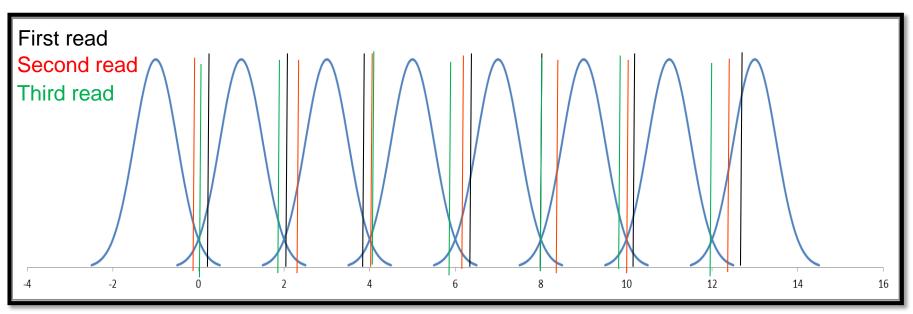

• Soft information is used to move the Shannon limit of a specific channel

[1] Wang Jiadong et al., "Enhanced Precision through multiple reads for LDPC Decoding in Flash Memories" in *IEEE Journal on Selected Areas in Communications,* May 2014

Flash Memory Summit 2015 Santa Clara, CA

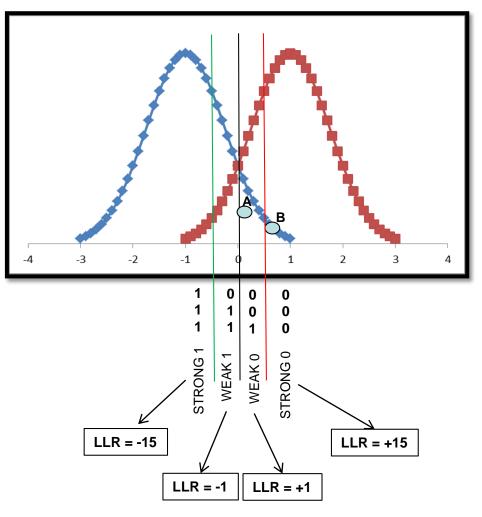

- Point A is more likely to be in error than point B

- Soft LDPC uses LLRs to measure reliability

- The overlap region between Vt distributions is scanned by using additional reads

performance seen by the users of the network.

To quantitatively measure quality of service, several related aspects of the network service are often considered, such as error rates, bandwidth, throughput, transmission delay, availability, jitter, etc.

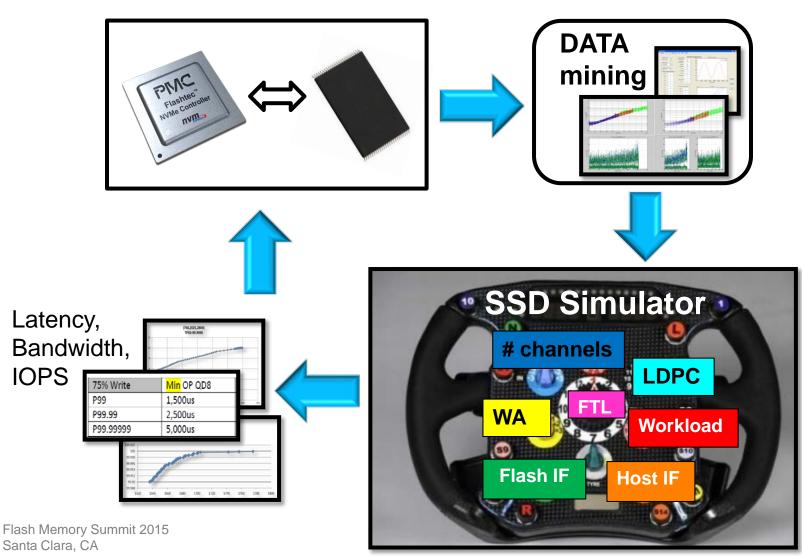

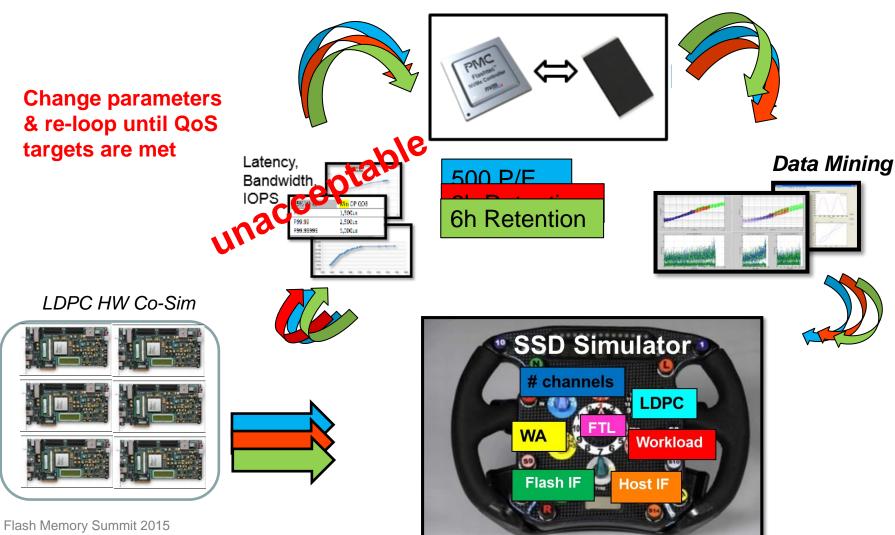

### Fully Integrated SSD-NAND Characterization Flow

# Read Oversampling: Mitigation Techniques

- "ShiftDesigner" is a custom developed tool that minimizes NAND BER by applying the shortest sequence of Vt-shifts

- LDPC: an FPGA network is used to identify the best trade-off between hard decoding and 1-bit or 2-bit soft decoding

### **ShiftDesigner**

- Shortest sequence

- minimum BER

- Shortest latency

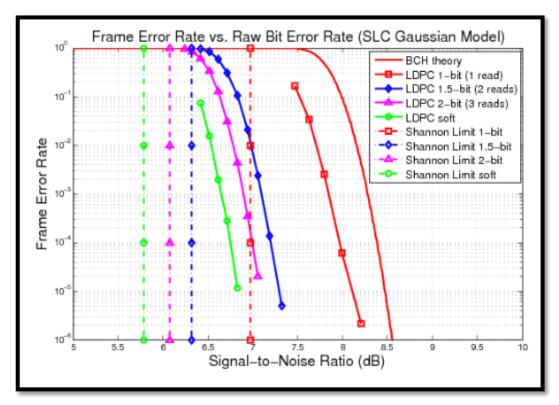

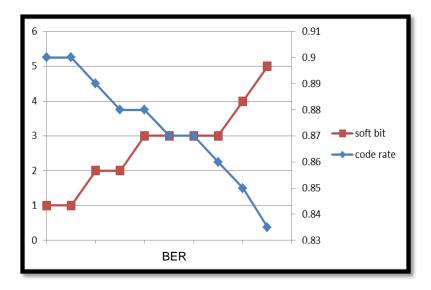

- Code Rate and the number of soft bits can be used to reduce FER

- Lower Code Rate means cheaper

- Higher number of soft bits translates into longer read latency

- LDPC HW/SW cosimulation can find the best compromise between latency and cost

R. Micheloni, P. Graumann, "Hardware/Software co-simulation for Error Floor detection in LDPC" - *Flash Memory Summit* 2014

### SSD-NAND: lifetime simulations

Santa Clara, CA

- Live Demo of the "Fully Integrated SSD-NAND Characterization Flow" can be seen at PMC Booth # 213

- The simulation engine of this demo is SSDExplorer

- <u>ssdexplorer.azurewebsites.net</u>

- More details about this tool in Forum F-21, "SSDExplorer: a virtual platform for SSD simulation"

- Vt-shift and soft information LDPC can be used to decrease NAND raw BER

- Both techniques impact QoS, because of the additional reads

- NAND silicon characterization can be coupled to an SSD simulator to predict and optimize SSD's QoS

- "ShiftDesigner" is a custom developed tool that minimizes NAND BER by applying the shortest sequence of Vt-shifts

- LDPC HW/SW co-simulations are used to find the best compromise between Hard and Soft decoding

# Thank You!Image: Descent of the second second

### blog.pmcs.com @pmcsierra