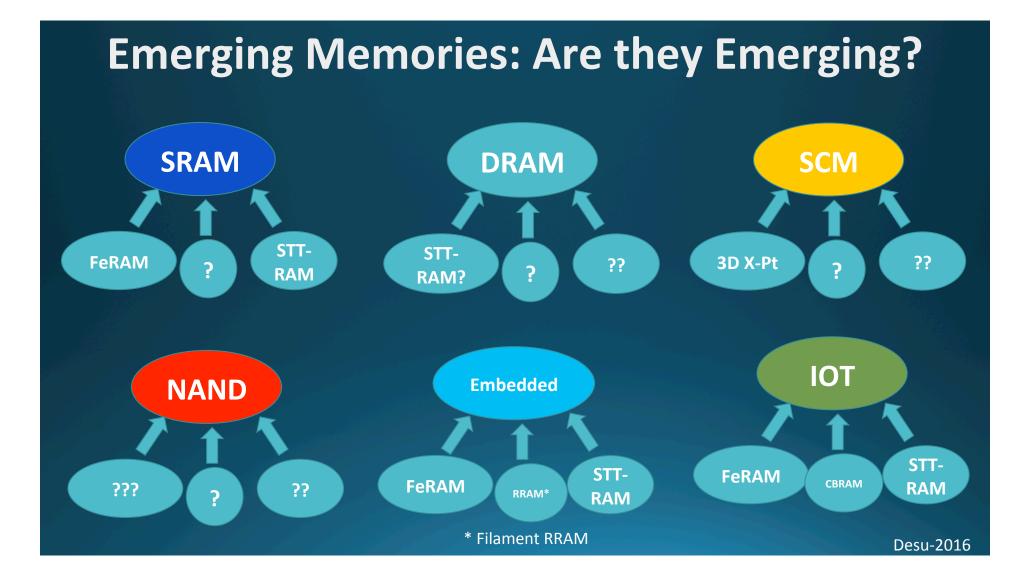

## Emerging

Dr. Seshubabu Desu Cheffechiology Office CS 4DS Memory Limited

Fremont, CA sbdesu@gmail.com

FMS-August 2016

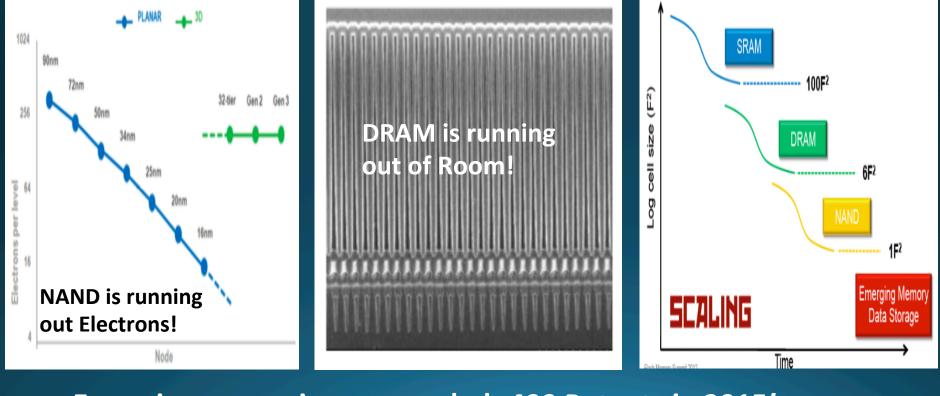

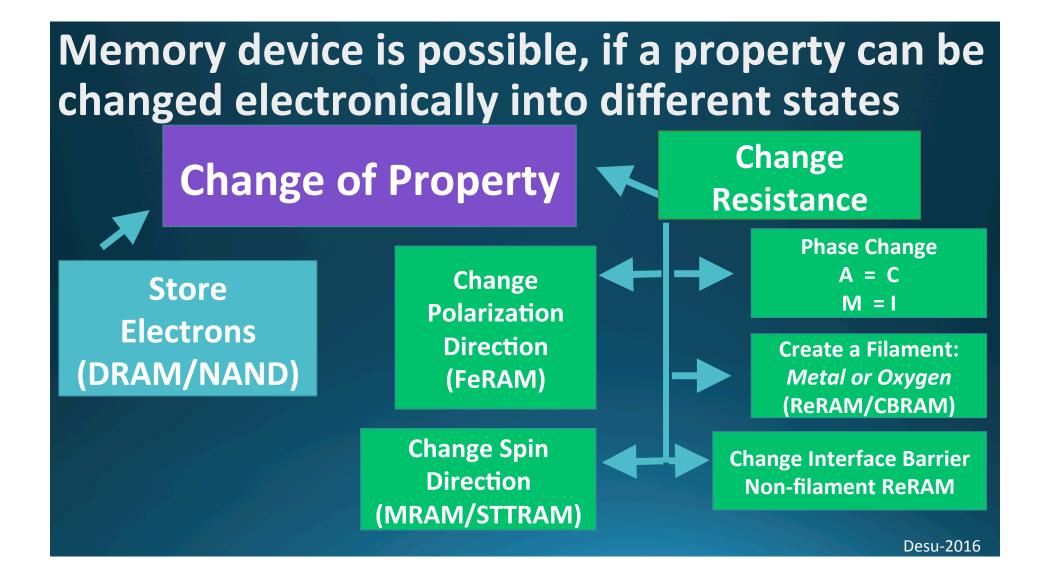

# Main stream memories are charge based and are loosing momentum!

**Emerging memories are needed;** 400 Patents in 2015!

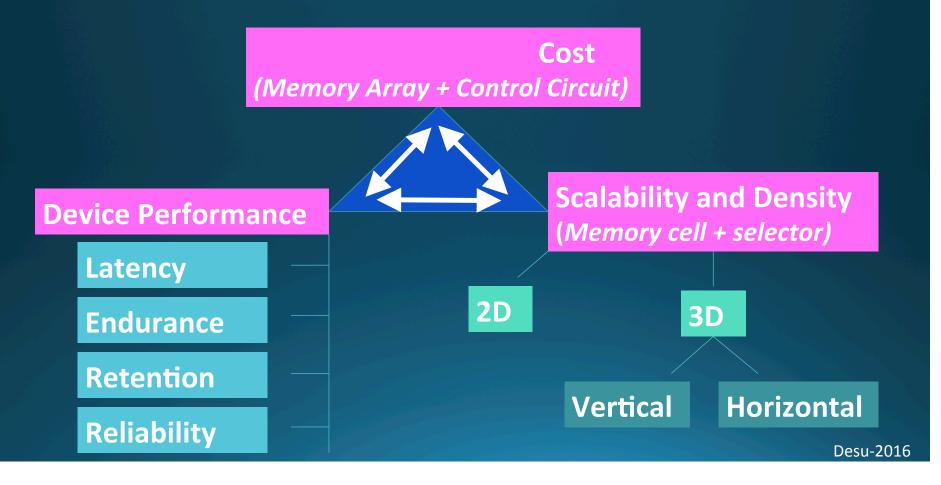

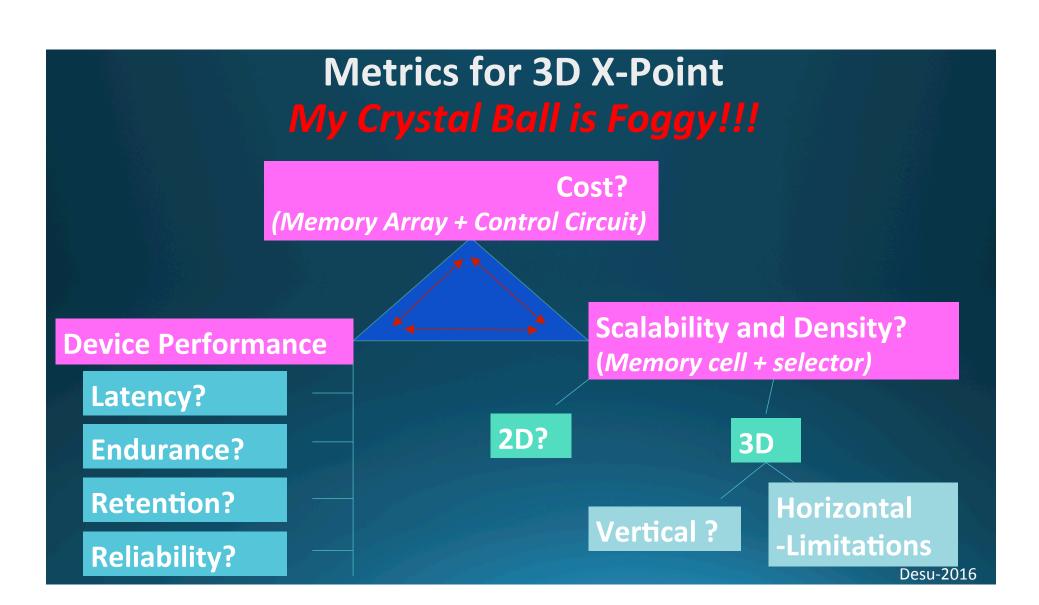

#### **Most Important Metrics for Emerging Memories**

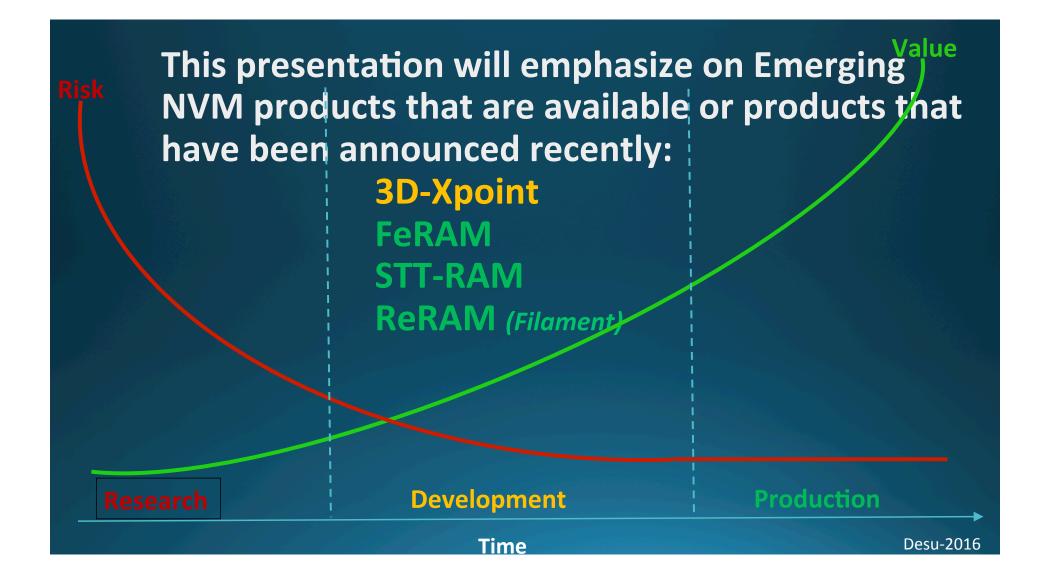

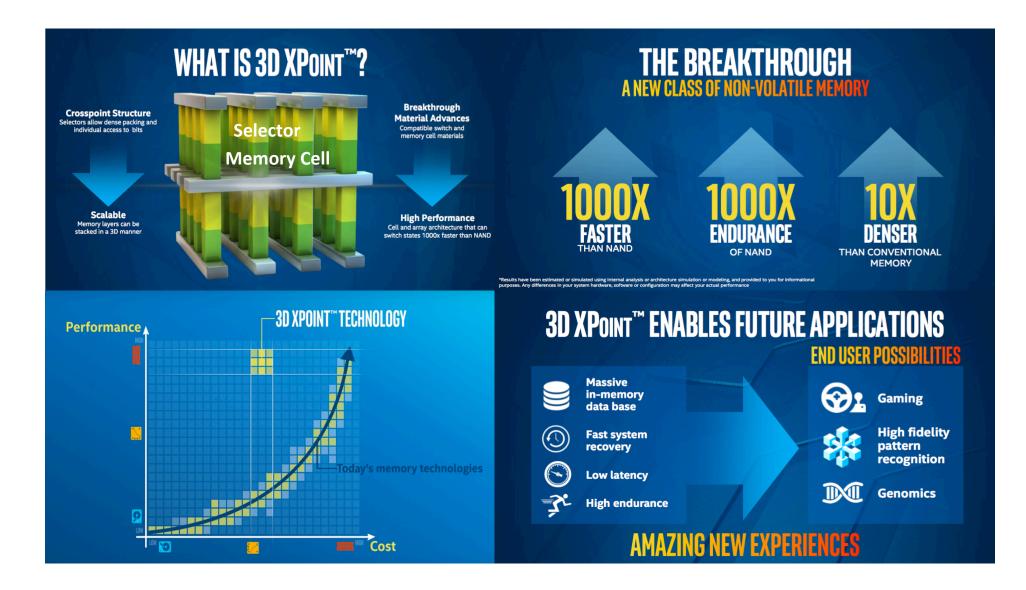

### **3D X-Point by Intel and Micron**

#### What did they reveal about 3D X-Point?

- Non-volatile memory is NOT based on a filament

- Non-Volatile memory is based on bulk-resistance change

- The memory material is a chalcogenide

- They also insist it is not a Phase Change Memory!

- Ovonic Threshold Switch (OTS) is the Selector

- It could take 12-18 months to get into mass production (Jan 2016)

- Uses ~100 new materials (raising supply chain issues)

- Lots of process steps to control the cross contamination

- 128 Gbit (in two planes) suggest ~19 nm feature size

- No retention numbers

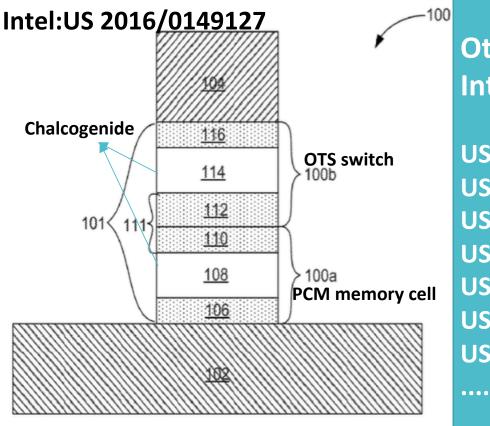

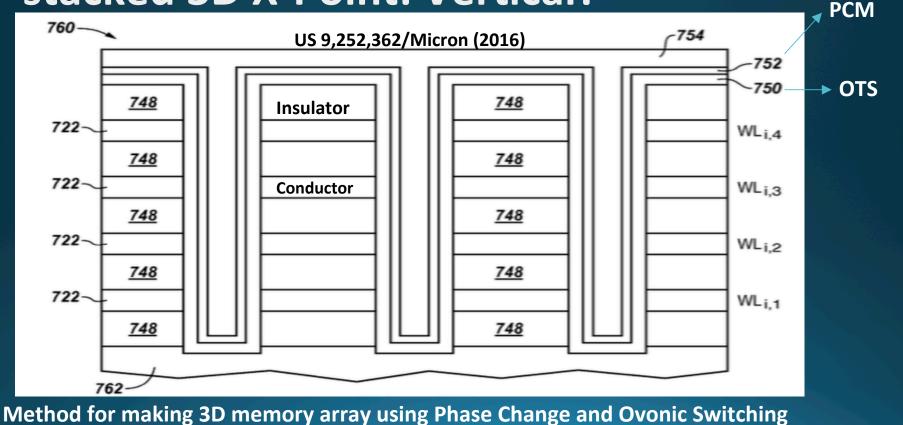

#### Patents assigned to Intel and Micron indicate that 3D X-Point is 'a flavor of PCM'

Other Similar Patents Assigned to Intel/Micron:

US 9,236,566 (2016)/Micron US 9,299,747 (2016)/Intel US 9,299,930 (2016)/Micron US 9,343,676 (2016)/Micron US 9,362,494 (2016)/Micron US 9,064,560 (2015)/Iintel US 8,953,387 (2013)/Micron

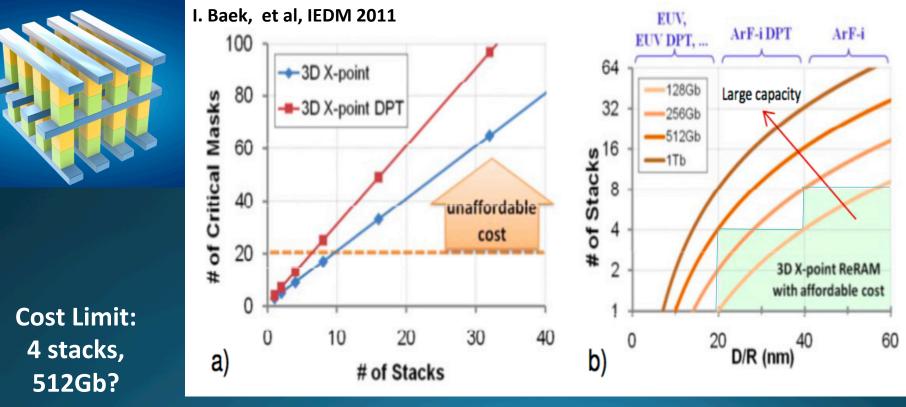

# Stacked 3D cross-point architecture is not cost effective if the number layers increase

# Solution for the density limitation of stacked 3D X-Point: Vertical?

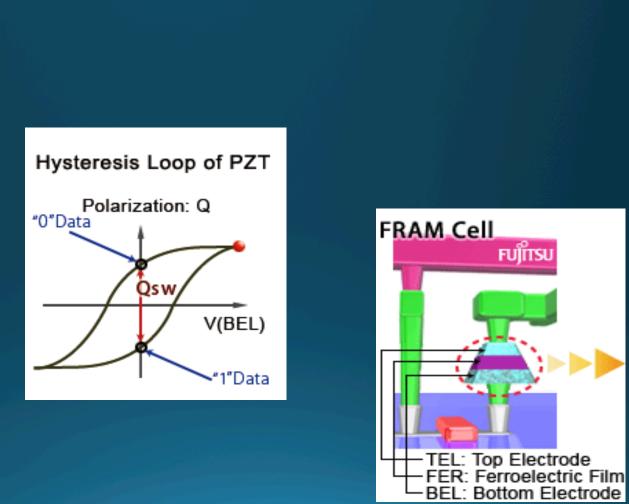

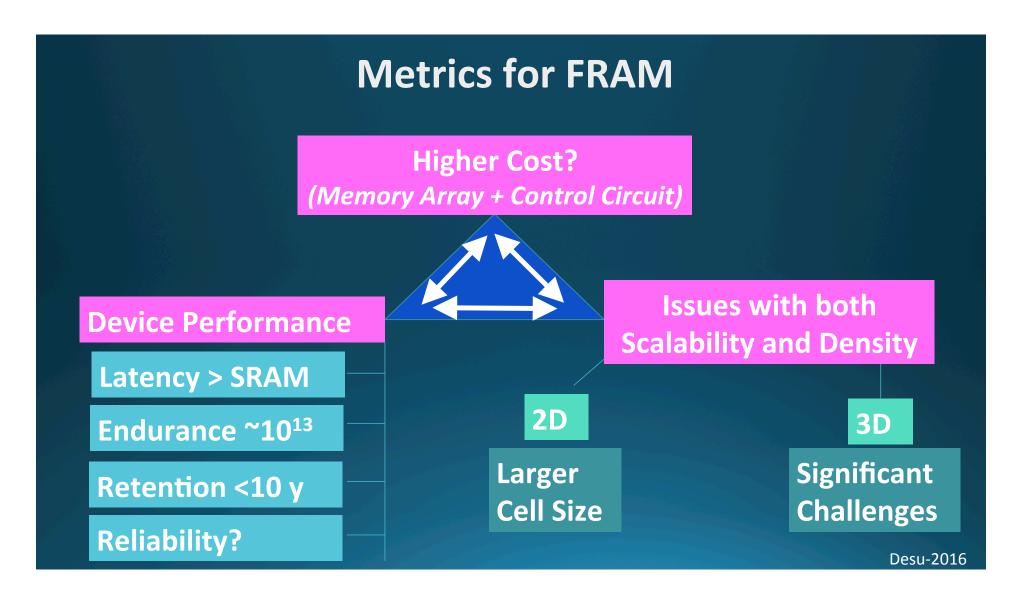

#### Ferroelectric Random Access Memory (FRAM)

## Crystal structure of PZT(FER) (Lead Zirconium Titanium/Pb(Zr,Ti)03) Electric Field ⊇:Zr/Ti ●:0 :Pb

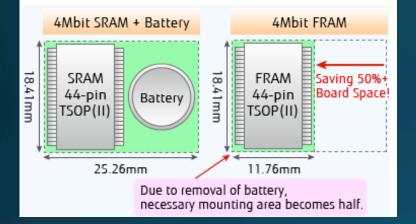

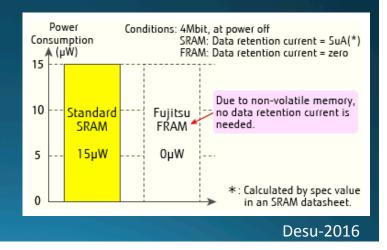

#### Fujitsu Develops 4 Mbit Quad SPI FRAM Capable of 54 MB/s Data Transfer (2/2016)

- Access Time 75 ns—150 ns

- Operating = 20 mA

- Standby = 150 μA

- Sleep = 20 μA

- 1.8V to 3.6 V

- -40°C to +85°C

- 10<sup>13</sup> Cycles of Endurance

- 10 Years of Retention

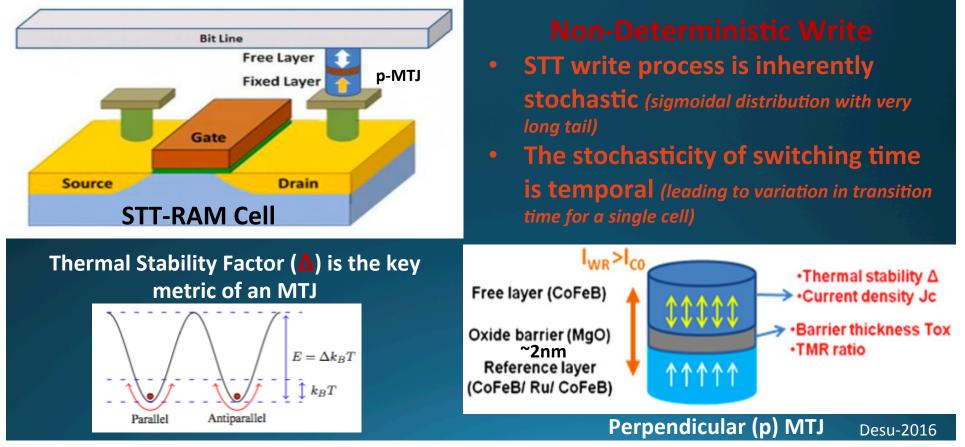

### MRAM/STT-RAM

#### The difference in resistance between Parallel and Anti-Parallel spin arrangements of MTJ is the key for MRAM

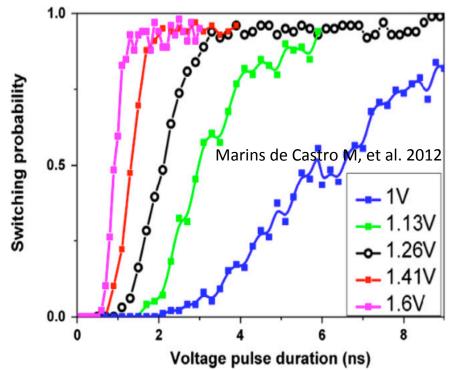

#### **STT stochastic switching behavior**

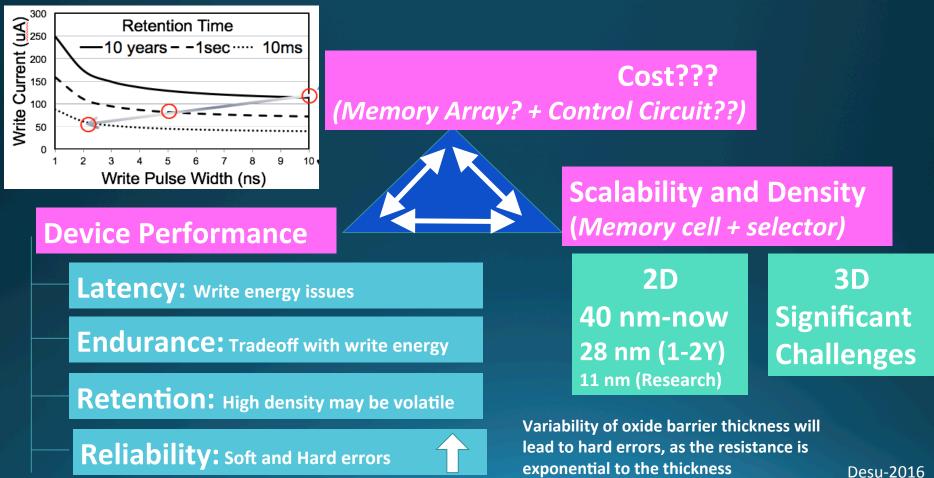

- Increasing the write current value I<sub>WR</sub> or driver pulse duration are the most efficient methods to avoid the writing failures

- But lead to significant power, speed, surface overhead storage, and could drive the breakdown or damage of oxide barrier

#### 1 Gbit STT-RAMs may be available

- Everspin is sampling 256 Mbit STT-RAM (p-MTJ) at 40 nm node and DDR interface and 100,000 X faster write time than NNAD

- Everspin 1 Gbit STT-RAM (28 nm) kit due by the end of the year!

- Avalanche Technology offers 32Mb SPSRAM<sup>™</sup>, which is a Quad SPI Non Volatile SRAM (pMTJ)

- Several companies offer embedded MRAM (40 nm and 28 nm)

IBM publishes a paper claiming 11 nm STT-RAM with write error rates of 7 X  $10^{-10}$  at 10 ns with a write current of 7.5  $\mu$ A corresponding to low switching energy below 100 fJ (June

#### Can STT-RAM replace SRAM and DRAM?

|                             | SRAM                    | DRAM                    | STT-RAM           |  |

|-----------------------------|-------------------------|-------------------------|-------------------|--|

| Туре                        | Volatile                | Volatile                | Non-Volatile?     |  |

| Scalability                 | <20 nm?                 | <1x nm?                 | 11 nm*            |  |

| Cell Size (F <sup>2</sup> ) | 120~200                 | 4~6                     | 15~50             |  |

| Multi-level                 | No                      | No                      | Yes*              |  |

| Read Speed                  | Very fast               | Fast                    | Fast              |  |

| Read Energy                 | Low                     | Medium                  | Medium            |  |

| Write Speed                 | Very fast               | Slow                    | Slow              |  |

| Write Energy                | Low                     | Medium                  | High              |  |

| Leakage                     | High                    | Medium                  | Low               |  |

| Endurance                   | <b>10</b> <sup>16</sup> | <b>10</b> <sup>16</sup> | >10 <sup>12</sup> |  |

| <b>Refresh Power</b>        | NA                      | High                    | Medium?           |  |

| *IBM (2016) R&D stage       |                         |                         |                   |  |

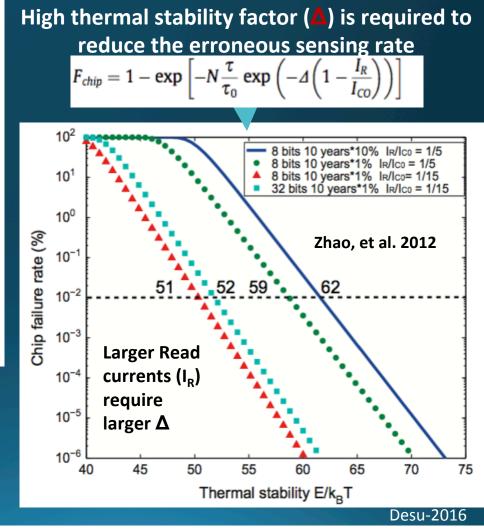

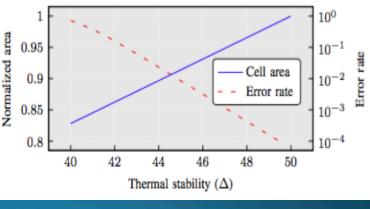

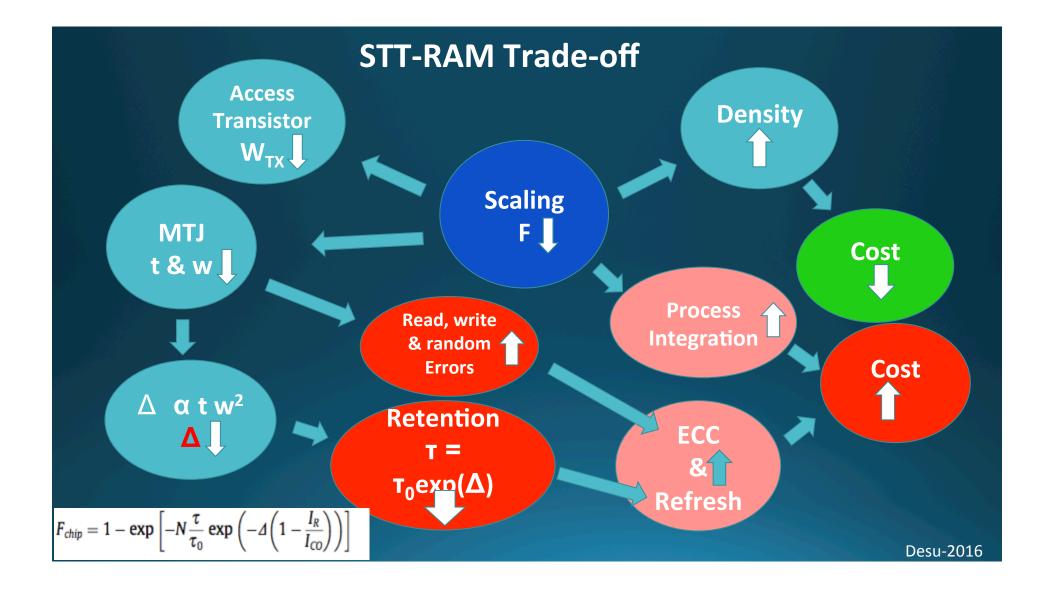

- Relax retention time to scale STT-RAM and lower write energy

- STT-RAM errors are stochastic

- DRAM has deterministic errors

- DRAM-like refresh cannot be used in STT-RAM (bit could flip)

- In STT-RAM refresh operation must be accompanied by ECC

Desu-2016

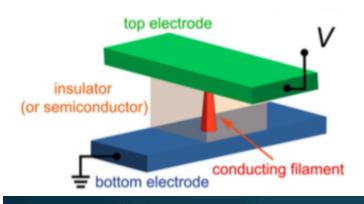

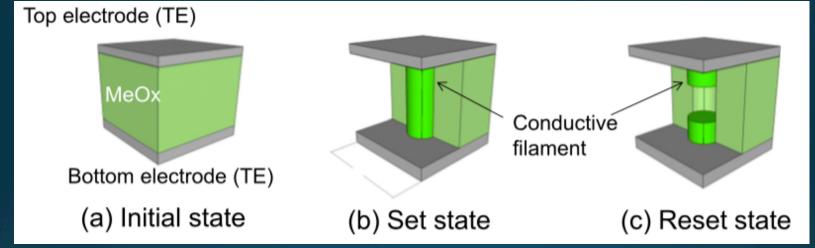

#### **Filament ReRAM**

**Oxy-ReRAM**

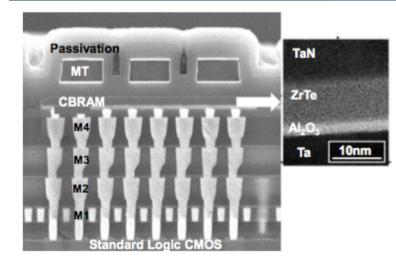

**CBRAM**

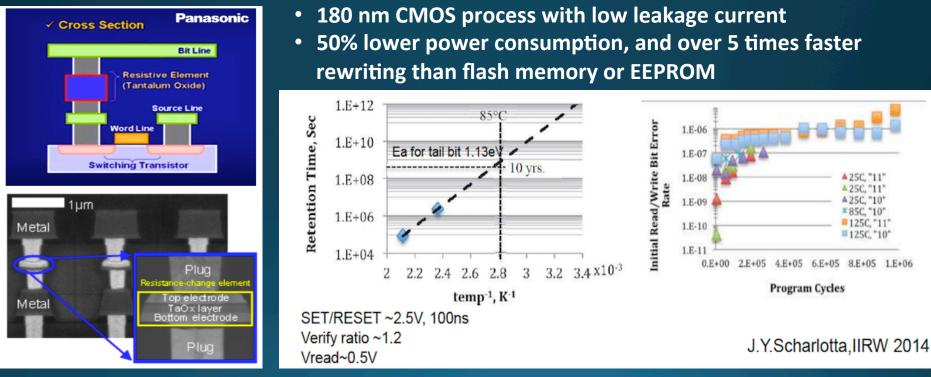

#### Panasonic MN101L, 64 kbytes Oxy-ReRAM (1T-1R) Embedded 8-bit MCUs

\*2Mbit ReRAM test memory array, claims 100K endurance cycling and 10 years of memory retention at 85°C at 28 nm node (Panasonic & IMEC, paper, 2015)

#### Adesto 512 Kbit EEPROM-compatible CBRAM

| Parameter              | Adesto Moneta  | Standard EEPROM |

|------------------------|----------------|-----------------|

| Core Supply Voltage    | 0.97-1.03V     | Not Applicable  |

| I/O Supply Voltage     | 1.65-2.75V     | Not Applicable  |

| Single Supply Voltage  | Not Applicable | 1.7-5.5V        |

| Read Power (500Kb/s)   | 10µW           | 1250µW          |

| Lowest Power-Down Mode | .05µW          | .25µW           |

| Clock Frequency (Max)  | 1MHz           | 20MHz           |

| Operating Temp Range   | -40 to +85°C   | -40 to +85°C    |

| Write Supply Voltage   | 3.6-4.4V       | 1.7-5.5V        |

| Write Power (10Kb/s)   | 7.5µW          | 375µW           |

- Single supply voltage: 1.65V 3.6V

- 1.6 MHz maximum clock rate for normal read

- 20 MHz maximum clock rate for fast read

- Byte Write consuming 50 nJ

- 0.25 mA Read current; 1 mA Write current

- Byte Write within 25 μs

- Data Retention: 10 years

- Endurance: 10,000 Write Cycles

- Unlimited Read Cycles

#### **Te---Metalloid Filament!!**

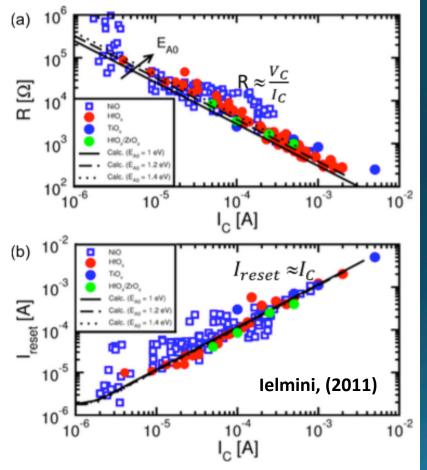

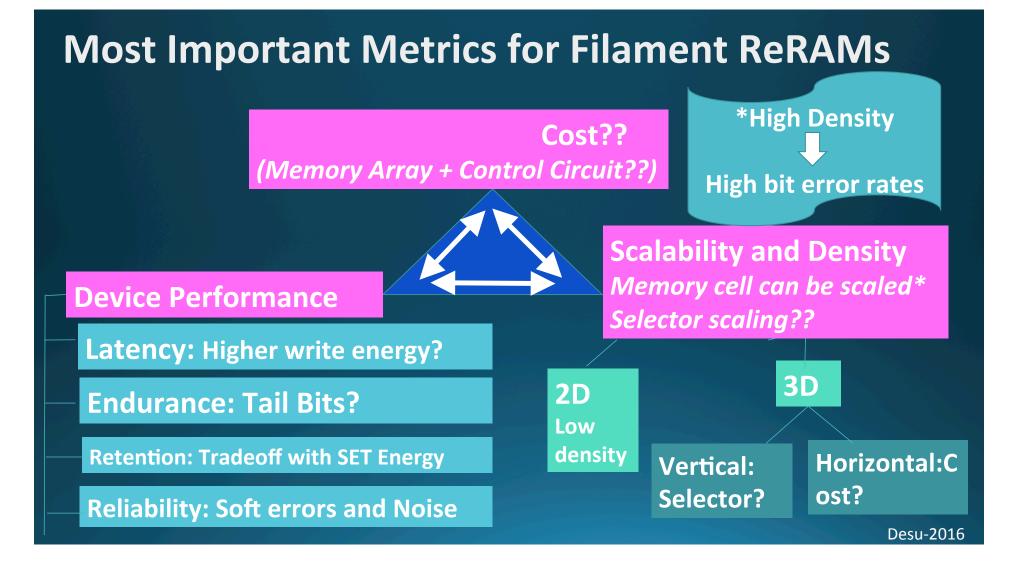

#### **Universal Characteristics of Filament ReRAM**

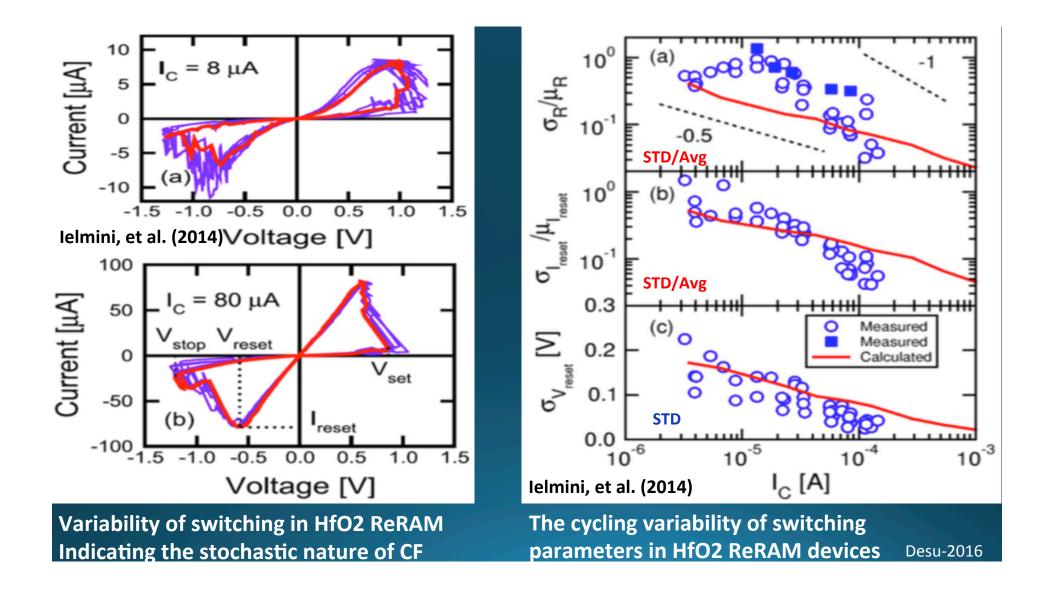

- The measured and calculated LRS Resistance (a) and I<sub>reset</sub> (b) as a function of compliance current (I<sub>c</sub>).

- I<sub>c</sub> controls the Conducting Filament size and resistance

- Negligible dependence on the switching mode (unipolar, bipolar) and stack composition or structure.

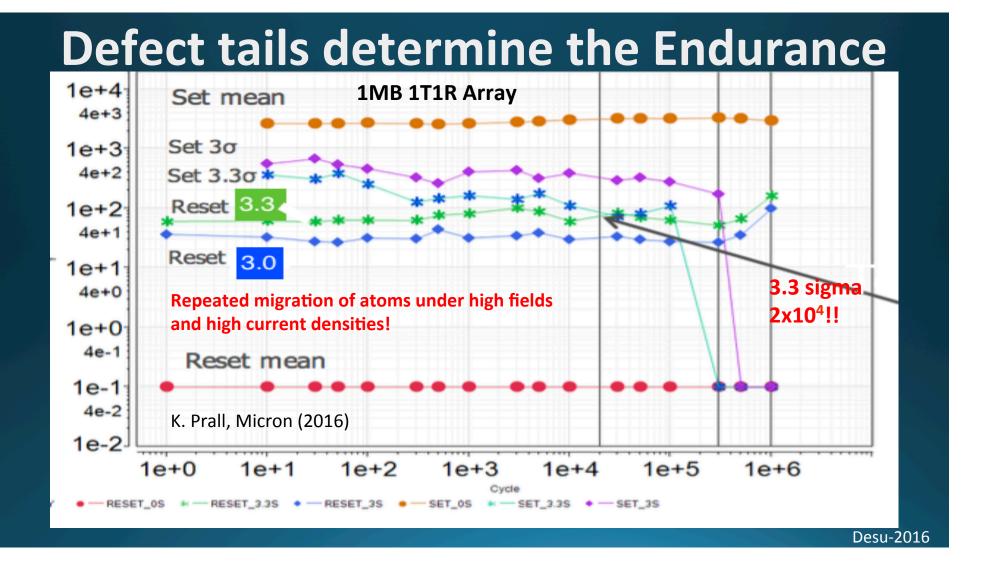

#### In addition to the process variations, Filament formation, rupture and regrowth are stochastic processes!!

Local high fields can change due to change in nature of defects and their concentrations (> 1 MV/cm)

Desu-2016

- Local power dissipation can alter the local temperatures (~ 1 TW/cm<sup>3</sup>)

- Local electronic current densities can vary (> 10<sup>6</sup> A/cm<sup>2</sup>)

- Significant local variations in ionic current densities

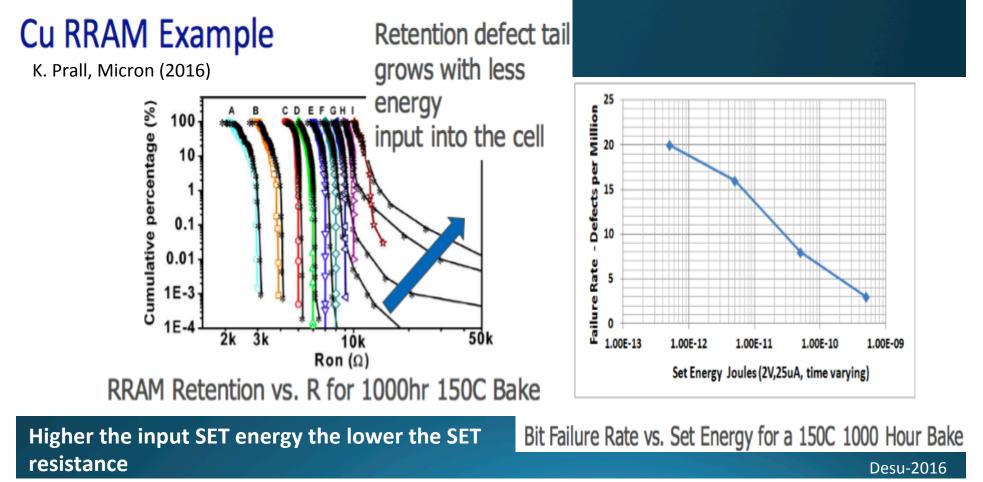

#### **Extensive optimization needed to engineer the tail bits**

#### **Retention is a strong function of SET energy!**

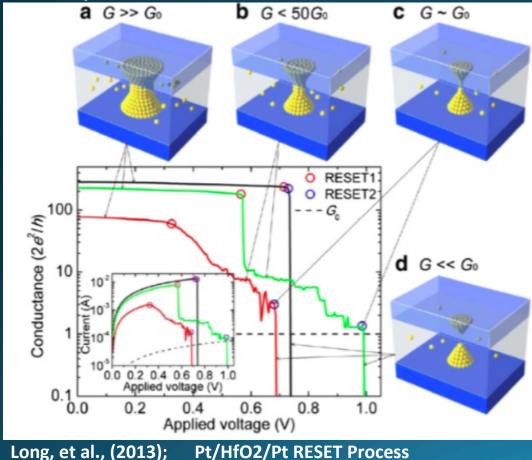

### **Quantization of Filament Resistance!**

- When the electron mean free path is close to the diameter of the CF, ballistic transport is possible

- Conductance of CF is quantized

- G<sub>0</sub> = 2 e<sup>2</sup>/h (R<sub>0</sub> = 12.9 k Ohms)

- 76 µA at 1V

- Independent of the nature of the filament and material composition!

- Would MLC possible??

- What about the statistical variability of CF with small dimensions?

## Thanks

## **Questions and/or Comments**