## Controller IC Evaluation of High Radix Parity Check Code

Oliver Hambrey Siglead Europe Limited

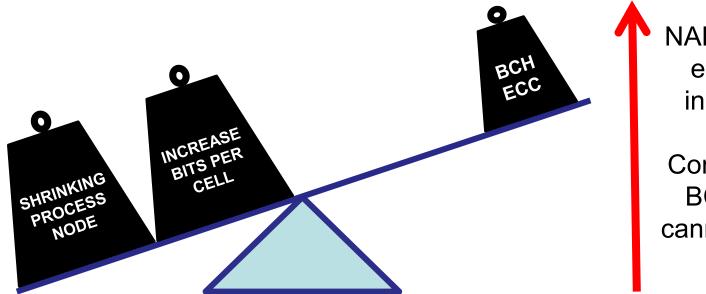

NAND raw bit error rate increases.

Conventional BCH ECC cannot protect data.

# NAND vs Error Correction (2)

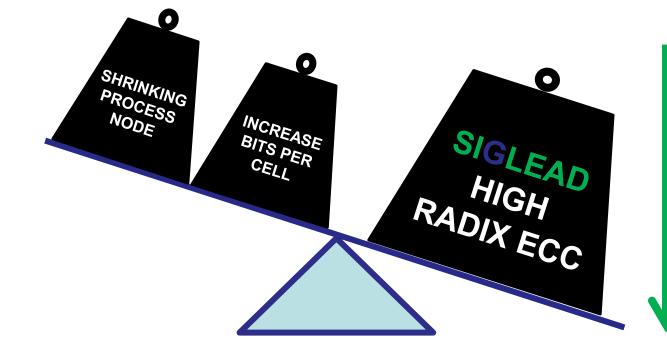

A stronger ECC will protect the data.

The balance is tipped in our favor!

Santa Clara, CA

## Siglead's High Radix ECC

- High Radix ECC is in our SATAIII

Controller IC

- Significantly stronger than BCH ECC

- typically delivering at least 2x improvement in SSD endurance even on sub 20nm TLC nodes

- No significant compromise in power consumption and throughput

n TLC nodes promise in n and

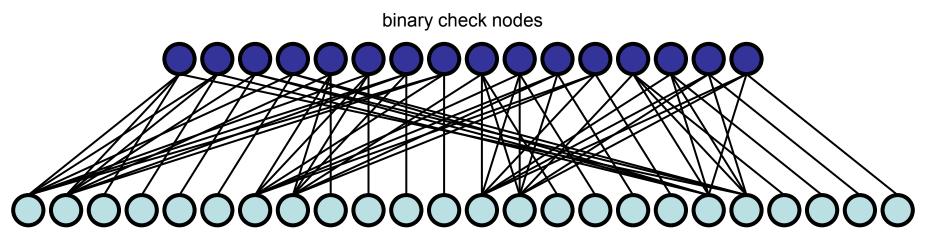

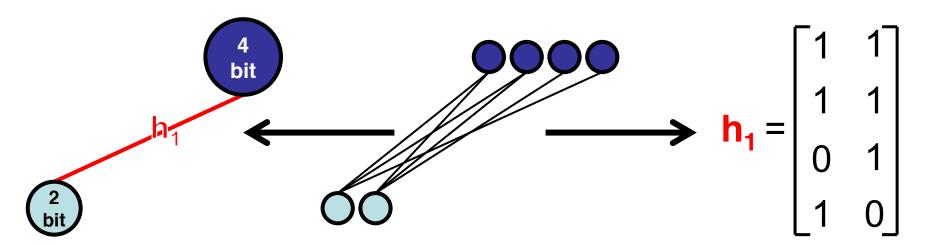

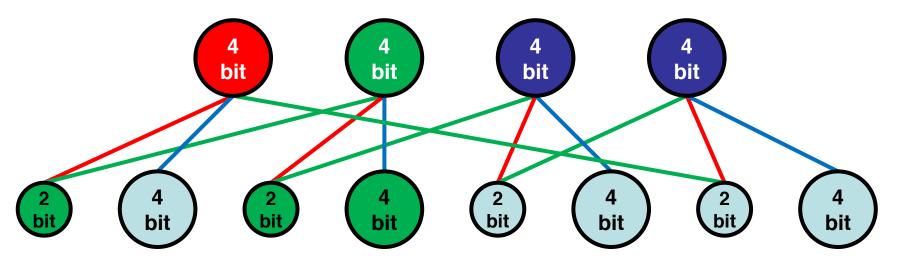

Merge binary variable/check nodes of a binary ECC

binary variable nodes

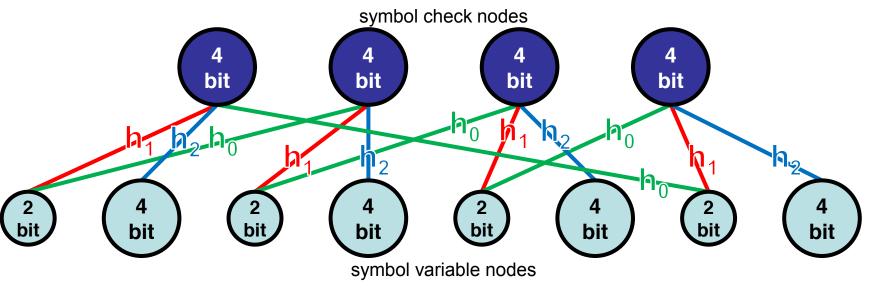

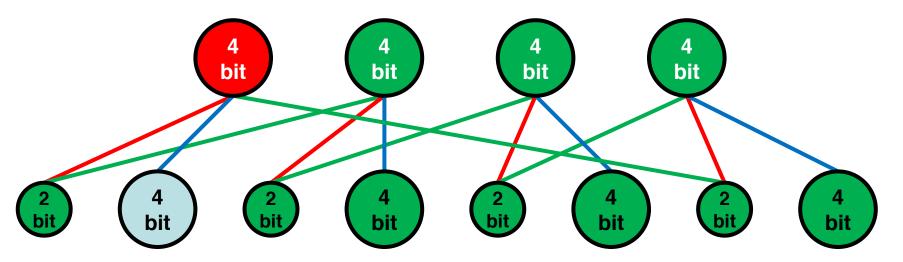

• Merge binary variable/check nodes of a binary ECC...

#### ...to get variable/check node SYMBOLS + EDGE LABELS

Edge label is matrix representation of merged edges of binary ECC

High Radix ECC parity check matrix is a matrix of submatrices

$$\mathbf{H} = \begin{bmatrix} \mathbf{h}_{1} & \mathbf{h}_{2} & \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{h}_{0} & \mathbf{0} \\ \mathbf{h}_{0} & \mathbf{0} & \mathbf{h}_{1} & \mathbf{h}_{2} & \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} & \mathbf{h}_{0} & \mathbf{0} & \mathbf{h}_{1} & \mathbf{h}_{2} & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{h}_{0} & \mathbf{0} & \mathbf{h}_{1} & \mathbf{h}_{2} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{0} & \mathbf{h}_{0} & \mathbf{0} & \mathbf{h}_{1} & \mathbf{h}_{2} \end{bmatrix}$$

where  $\mathbf{h}_{0} = \begin{bmatrix} \mathbf{0} & \mathbf{1} \\ \mathbf{1} & \mathbf{0} \\ \mathbf{1} & \mathbf{1} \\ \mathbf{1} & \mathbf{1} \end{bmatrix}$ ,  $\mathbf{h}_{1} = \begin{bmatrix} \mathbf{1} & \mathbf{1} \\ \mathbf{1} & \mathbf{0} \\ \mathbf{0} & \mathbf{1} \\ \mathbf{0} & \mathbf{1} \end{bmatrix}$  and  $\mathbf{h}_{2} = \begin{bmatrix} \mathbf{1} & \mathbf{0} & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{1} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} & \mathbf{1} \end{bmatrix}$

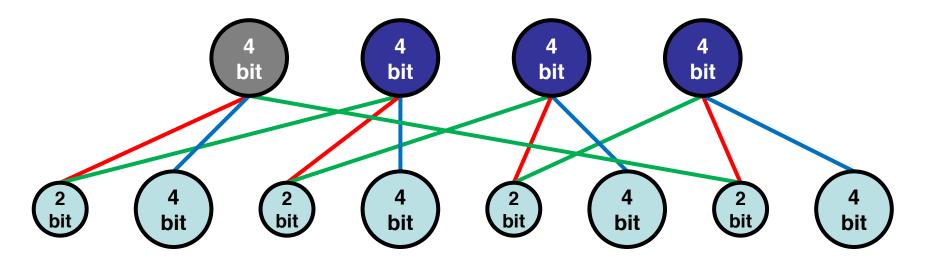

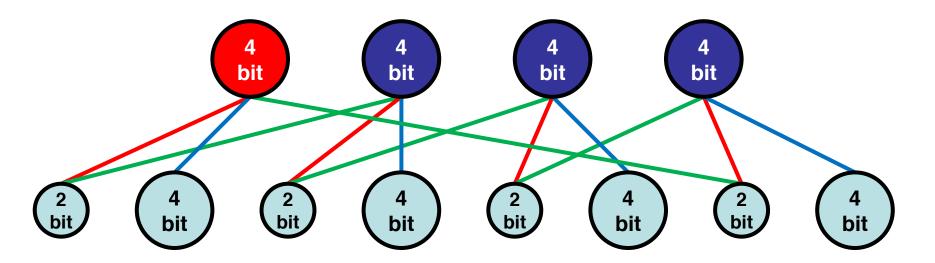

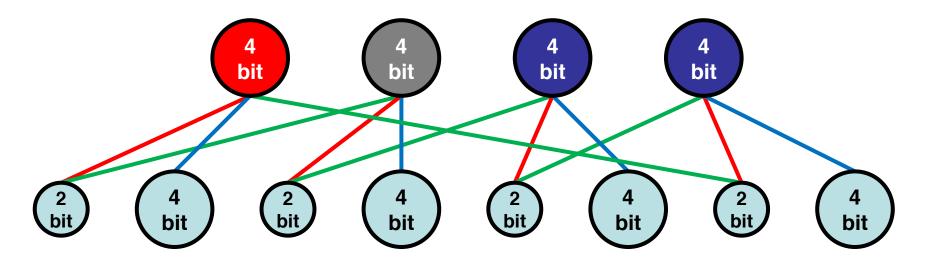

• Start with 1<sup>st</sup> check node (highlighted grey)

• 1<sup>st</sup> check node ECC uncorrectable (highlight red)

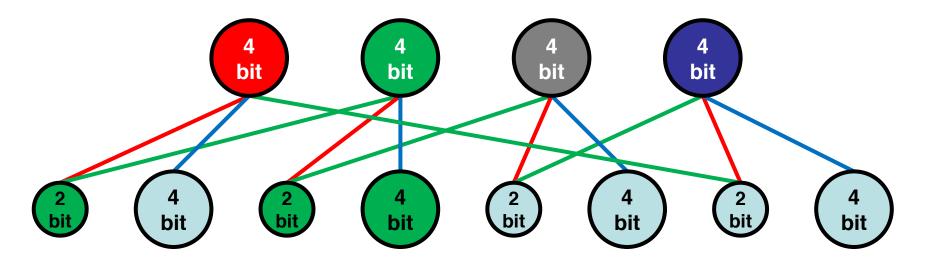

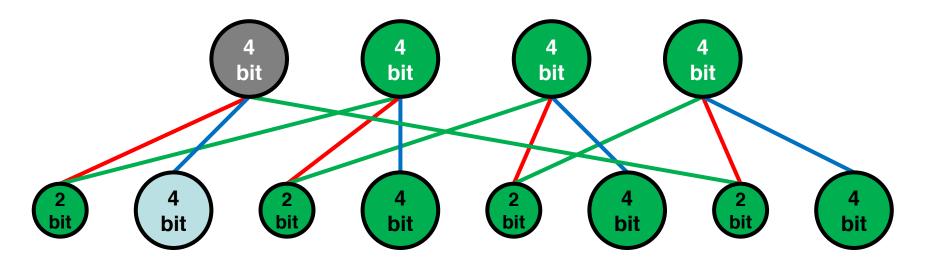

• Move to 2<sup>nd</sup> check node (highlighted grey)

- 2<sup>nd</sup> check node ECC correctable (highlight green)

- Attached variable nodes are corrected (highlighted green)

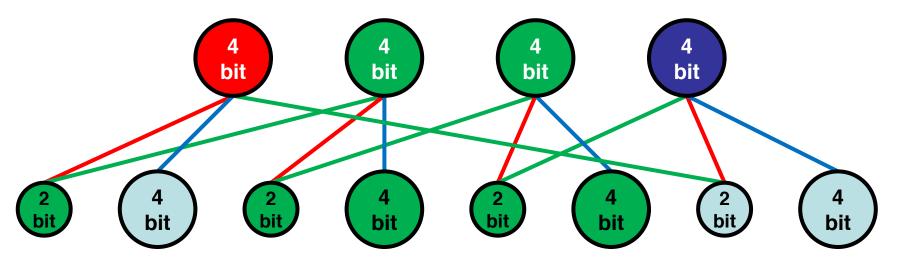

• Move to 3<sup>rd</sup> check node (highlighted grey)

- 3<sup>rd</sup> check node ECC correctable (highlight green)

- Attached variable nodes are corrected (highlighted green)

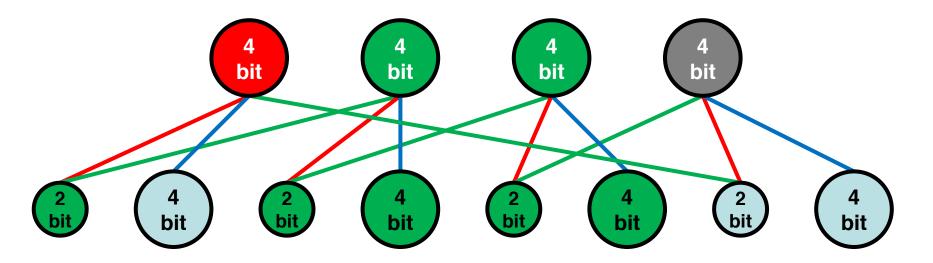

• Move to 4<sup>th</sup> check node (highlighted grey)

- 4<sup>th</sup> check node ECC correctable (highlight green)

- Attached variable nodes are corrected (highlighted green)

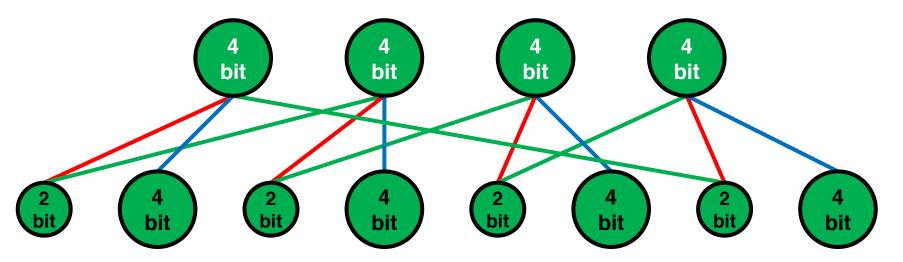

• Return to 1<sup>st</sup> check node (highlighted grey)

- 1<sup>st</sup> check node ECC is now correctable (highlight green)

- Attached variable nodes are corrected (highlighted green)

#### High Radix ECC in SSD Controller IC

**Outline of High Radix ECC parity** check matrix in SL2007D 1()4 h<sub>0</sub>  $\mathbf{H} =$ 16  $h_{191}$ edge matrix:16x104 containing 192 nonzero sub matrices

#### Highly programmable

- variety of code rates are possible to suit different NAND processes/vendors/bits per cell

- many different configurations of High Radix ECC parity check matrix are possible

#### Typical Example for 16kB NAND page:

- 16 High Radix check nodes

- encodes a least 1kB of user data per check node

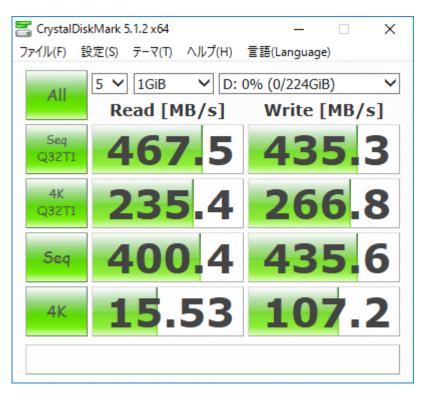

#### Controller IC Throughput Performance

- Throughput performance of Siglead's controller IC with High Radix ECC enabled

- INTERFACE: SATAIII

- No significant drop down in performance when using High Radix ECC

## Controller ECC Performance on Sub 20nm TLC NAND

- Controller IC evaluation of High Radix ECC

- NAND: sub 20nm TLC

- ENDURANCE: 300P/E cycles using "LDPC achieving RBER=10<sup>-2</sup>"

- High Radix ECC achieves endurance of up to 600P/E cycles

#### SIGLEAD'S High Radix ECC achieved 2x ENDURANCE on sub 20nm TLC node

#### SUB 20nm TLC NAND SIGLEAD BCH P/E HIGH CODE **CYCLES** RADIX ONLY ECC FAIL 150 PASS FAIL 300 PASS FAIL PASS 450 FAIL 600 PASS 750 FAIL FAIL

#### VISIT SIGLEAD'S BOOTH @ FMS2016

Live demo of SL2007D – our SSD controller IC

Live Demo of our NAND analyzer platforms SigNASII and SigNAS3

# **BOOTH 900**