#### Advanced Controller Technology for 3D NAND Flash Wei Lin

#### Senior Architect, Phison wei\_lin@phison.com

PHISON's presentation contains forward-looking statements subject to significant risks and uncertainties. Actual results may differ materially from those contained in the forward-looking statements. Information as to those factors that could cause actual results to vary can be found in PHISON's annual reports and other documents filed from time-to-time with the TWSE. Except as required by law, we undertake no obligation to update any forward-looking statement, whether as a result of new information, future events, or otherwise.

- The Reliability Issues of 3D NAND Flash

- The Architecture of Error Handling Technology

- Error Correction Technology

- Comparison between ECC engines

- Reliability of SSD with 3D NAND Flash memory

- Conclusion

- The Reliability Issues of 3D NAND Flash

- The Architecture of Error Handling Technology

- Error Correction Technology

- Comparison between ECC engines

- Reliability of SSD with 3D NAND Flash memory

- Conclusion

### mory The Reliability Issues of 3D NAND

- Fast de-trapping of programmed electron

- Layer Dependency

- Different erase mechanism from 2D NAND

- Different retention behavior from 2D NAND

- Weak read disturb immunity

- Weak program disturb immunity

#### • The Reliability Issues of 3D NAND Flash

- The Architecture of Error Handling Technology

- Error Correction Technology

- Comparison between ECC engines

- Reliability of SSD with 3D NAND Flash memory

- Conclusion

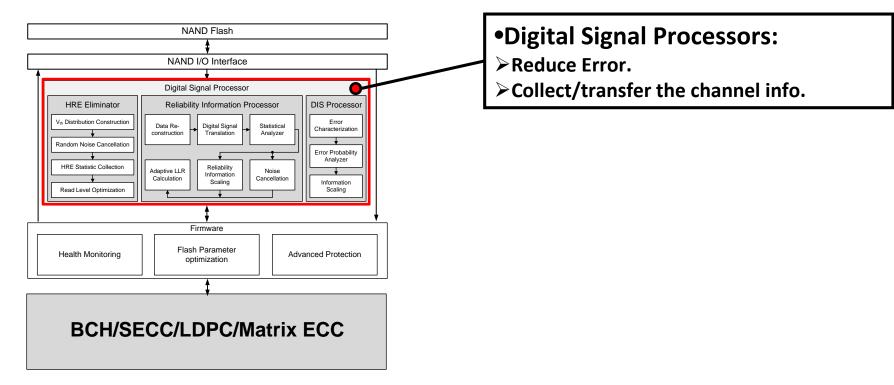

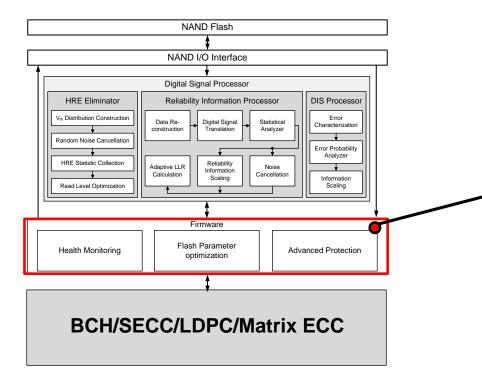

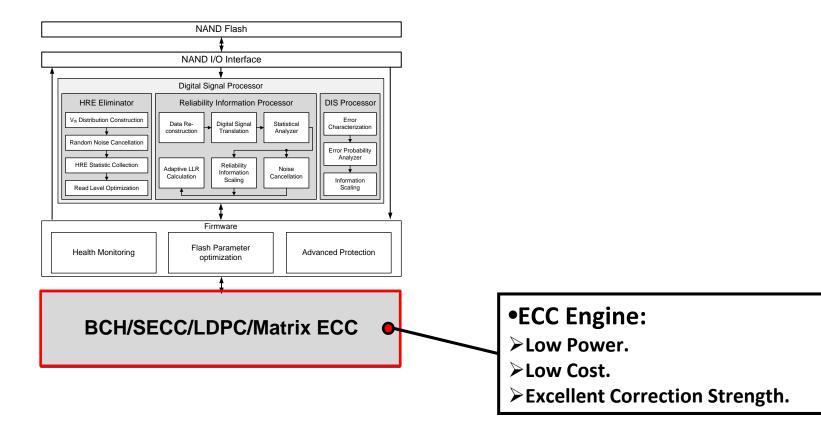

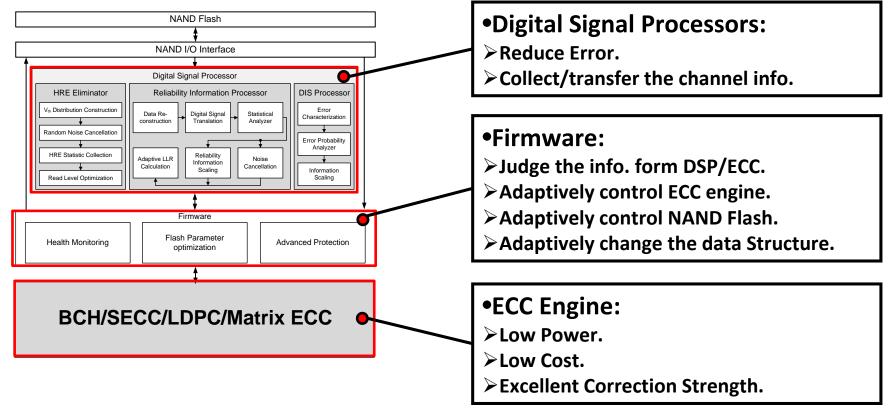

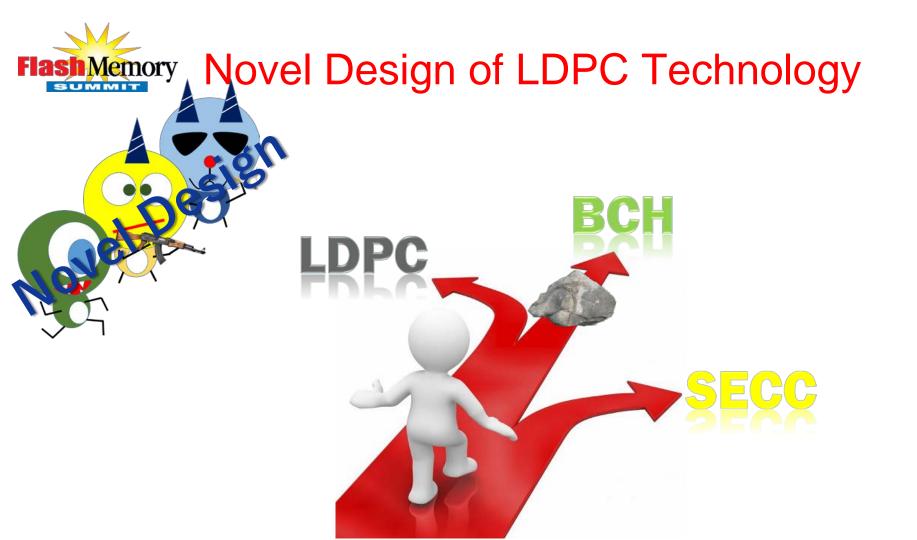

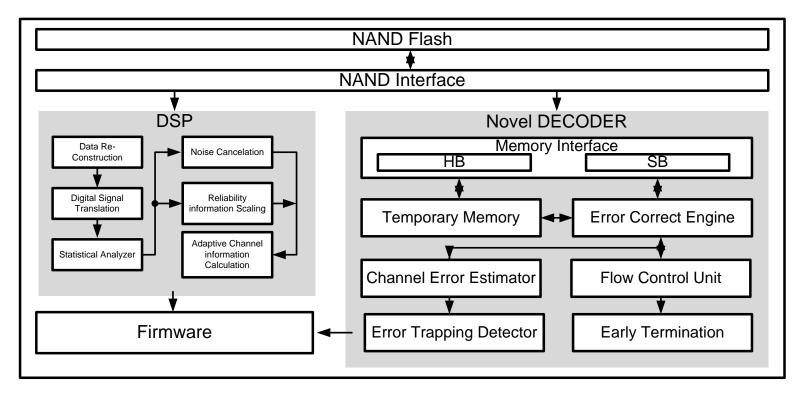

## Flash Memory Error Handling Tech. in Controller

# Firmware: Judge the info. form DSP/ECC. Adaptively control ECC engine. Adaptively control NAND Flash. Adaptively change the data Structure.

- The Reliability Issues of 3D NAND Flash

- The Architecture of Error Handling Technology

- Error Correction Technology

- Comparison between ECC engines

- Reliability of SSD with 3D NAND Flash memory

- Conclusion

- The Reliability Issues of 3D NAND Flash

- The Architecture of Error Handling Technology

- Error Correction Technology

- Comparison between ECC engines

- Reliability of SSD with 3D NAND Flash memory

- Conclusion

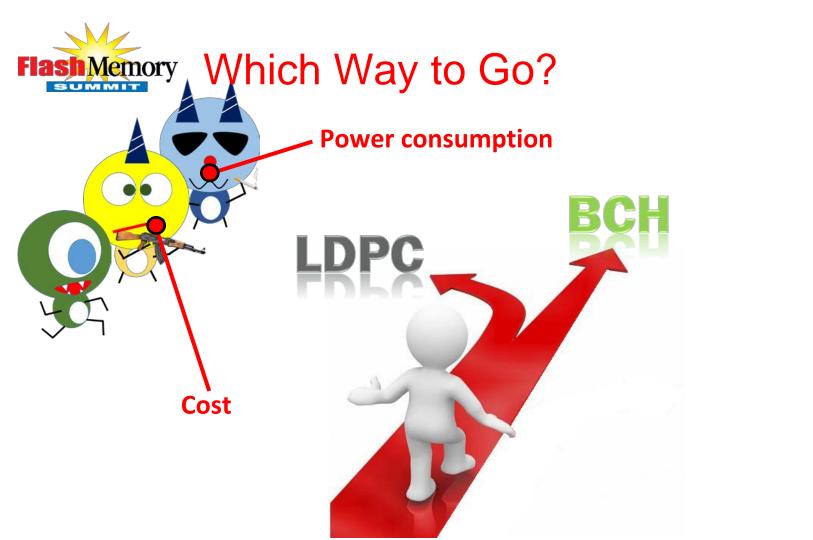

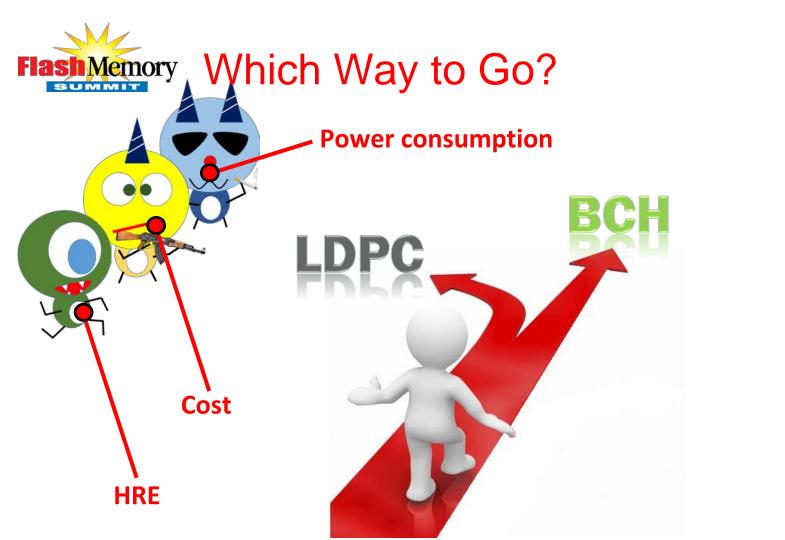

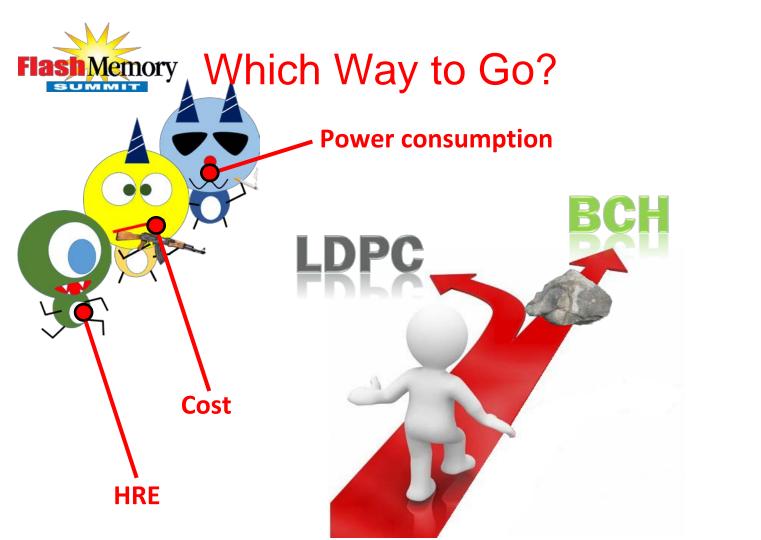

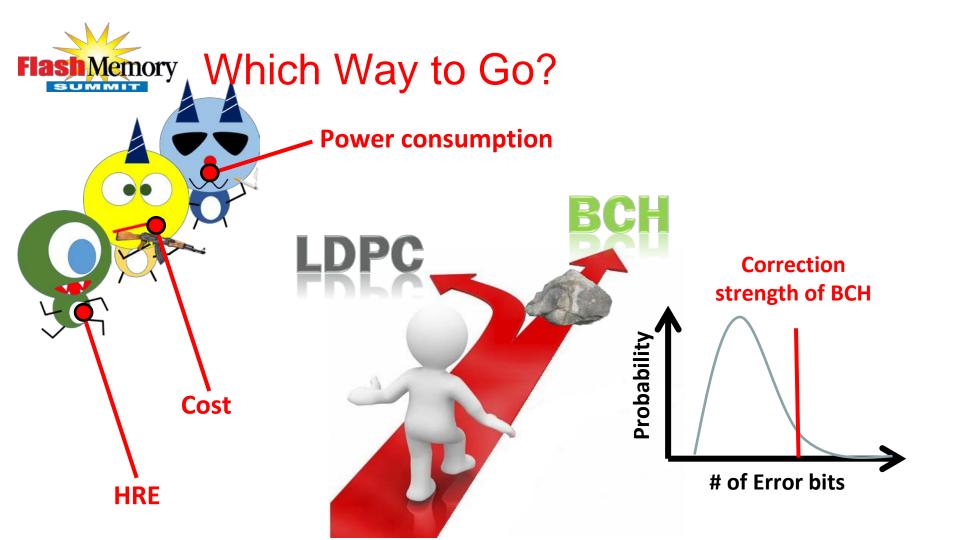

#### Flash Memory Comparison between ECC tech

|                                | Conventional LDPC | ВСН                                              |

|--------------------------------|-------------------|--------------------------------------------------|

| Decoding Algorithm             | Probability Based | Algebraic Based                                  |

| Guaranteed Correction Strength | No                | Yes                                              |

| Soft Bit Decoding              | Easy              | Hard                                             |

| Performance of Hard Decoding   | Similar to BCH    | Code Length * (1-code rate) Degree of polynomial |

| Performance of Soft Decoding   | 2X than BCH       | -                                                |

| Decoding Complexity            | High              | Low                                              |

| Power consumption              | High              | Mid                                              |

| Cost                           | High              | Low                                              |

Flash Memory Summit 2016 Santa Clara, CA

### Flash Memory Comparison between ECC of Phison

|                                   | 4K LDPC           | 4K LDPC Lite      | SECC              | ВСН                                                 |

|-----------------------------------|-------------------|-------------------|-------------------|-----------------------------------------------------|

| Decoding Algorithm                | Probability Based | Probability Based | Probability Based | Algebraic Based                                     |

| Guaranteed Correction<br>Strength | No                | No                | No                | Yes                                                 |

| Soft Bit Decoding                 | Easy              | Easy              | Easy              | Hard                                                |

| Performance of Hard<br>Decoding   | 1.3X BCH          | Similar to BCH    | 1.3X than BCH     | Code Length * (1-code rate)<br>Degree of polynomial |

| Performance of Soft<br>Decoding   | 2X-3X than HB     | 2X than BCH       | 1.7X than BCH     | -                                                   |

| Decoding Complexity               | Mid               | Mid               | Low               | Low                                                 |

| Power consumption                 | Low               | Low               | Low               | Mid                                                 |

| Cost                              | High              | Mid               | Low               | Low                                                 |

## Flash Memory ECC Technology of Phison

|              | Correction<br>Strength | Gate<br>Count | Technology<br>node (nm) | Support NAND         | Q3' 2016                    | Q4' 2016         | 2017    |

|--------------|------------------------|---------------|-------------------------|----------------------|-----------------------------|------------------|---------|

| 1K BCH       | 72/1K                  | 260K          | 55/40/28                | 2D/3D<br>MLC/TLC     | Applied                     | d for USB/SD/eMM | IC/SSD  |

| 2К ВСН       | 120/2К                 | 540K          | 55                      | 2D/3D<br>MLC/TLC     | Applied for SSD             |                  |         |

| SECC         | 95&135/1K              | 300K          | 40                      | 2D/3D<br>MLC/TLC/QLC | Applied for SD/eMMC/UFS/SSD |                  | FS/SSD  |

| 4K LDPC Lite | 72&150/1K              | 0.7M          | 40                      | 2D/3D<br>MLC/TLC/QLC | Applied for SSD             |                  |         |

| 4K LDPC      | 85&200/1K              | 1M            | 28                      | 2D/3D<br>MLC/TLC/QLC |                             | Applied          | for SSD |

| Matrix ECC   | -                      | 300K          | 55/40/28                | 2D/3D<br>MLC/TLC/QLC | Applied for SSD/UFS         |                  |         |

#### Flash Memory Comparison between ECC of Phison

|                                   | 4K LDPC           | 4K LDPC Lite      | SECC              | ВСН                                                 |

|-----------------------------------|-------------------|-------------------|-------------------|-----------------------------------------------------|

| Decoding Algorithm                | Probability Based | Probability Based | Probability Based | Algebraic Based                                     |

| Guaranteed Correction<br>Strength | No                | No                | No                | Yes                                                 |

| Soft Bit Decoding                 | Easy              | Easy              | Easy              | Hard                                                |

| Performance of Hard<br>Decoding   | 1.3X BCH          | Similar to BCH    | 1.3X than BCH     | Code Length * (1-code rate)<br>Degree of polynomial |

| Performance of Soft<br>Decoding   | 2X-3X than HB     | 2X than BCH       | 1.7X than BCH     | -                                                   |

| Decoding Complexity               | Mid               | Mid               | Low               | Low                                                 |

| Power consumption                 | Low               | Low               | Low               | Mid                                                 |

| Cost                              | High              | Mid               | Low               | Low                                                 |

#### Comparison between ECC of Phison **Flash** Memory

SUMMIT

#### Flash Memory Comparison between ECC of Phison

|                                   | 4K LDPC           | 4K LDPC Lite      | SECC              | ВСН                                                 |

|-----------------------------------|-------------------|-------------------|-------------------|-----------------------------------------------------|

| Decoding Algorithm                | Probability Based | Probability Based | Probability Based | Algebraic Based                                     |

| Guaranteed Correction<br>Strength | No                | No                | No                | Yes                                                 |

| Soft Bit Decoding                 | Easy              | Easy              | Easy              | Hard                                                |

| Performance of Hard<br>Decoding   | 1.3X BCH          | Similar to BCH    | 1.3X than BCH     | Code Length * (1-code rate)<br>Degree of polynomial |

| Performance of Soft<br>Decoding   | 2X-3X than HB     | 2X than BCH       | 1.7X than BCH     | -                                                   |

| Decoding Complexity               | Mid               | Mid               | Low               | Low                                                 |

| Power consumption                 | Low               | Low               | Low               | Mid                                                 |

| Cost                              | High              | Mid               | Low               | Low                                                 |

### Flash Memory Comparison between ECC of Phison

| Decoding Algorithm<br>Guaranteed Correction<br>Strength | Prob |           | ed | Algebraic Based                                     |

|---------------------------------------------------------|------|-----------|----|-----------------------------------------------------|

| Strength                                                |      |           |    |                                                     |

|                                                         |      | DUIDONI   |    | Yes                                                 |

| Soft Bit Decoding                                       |      | PHISON    |    | Hard                                                |

| Performance of Hard<br>Decoding                         |      |           | н  | Code Length * (1-code rate)<br>Degree of polynomial |

| Performance of Soft<br>Decoding                         | 2X-  | PS5008-F8 | н  | -                                                   |

| Decoding Complexity                                     |      |           |    | Low                                                 |

| Power consumption                                       |      |           |    | Mid                                                 |

| Cost                                                    |      |           |    | Low                                                 |

#### Flash Memory Correction Capability of SECC

- The Reliability Issues of 3D NAND Flash

- The Architecture of Error Handling Technology

- Error Correction Technology

- Comparison between ECC engines

- Reliability of SSD with 3D NAND Flash memory

- Conclusion

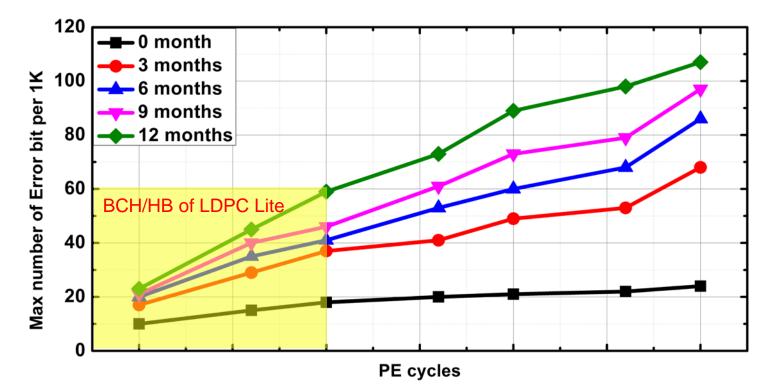

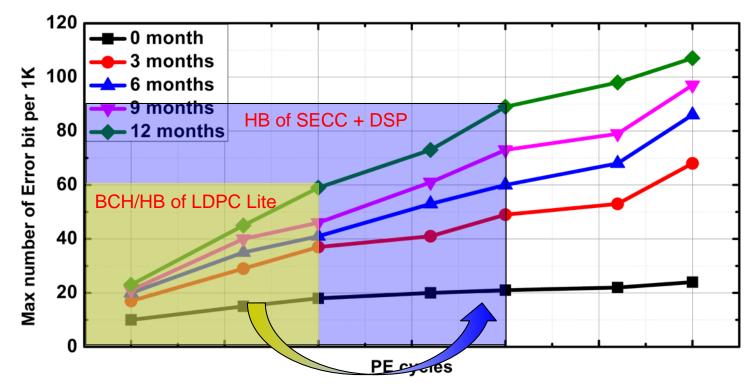

2X Extended

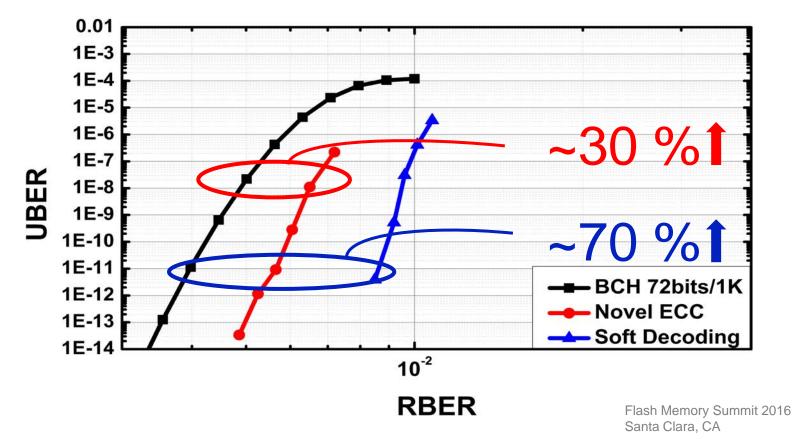

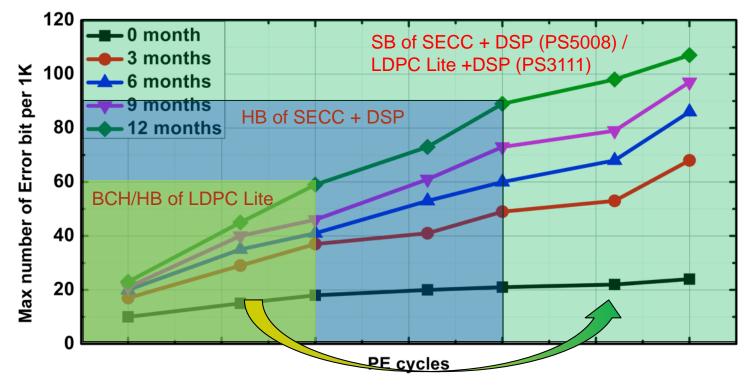

#### **Reliability Improvement of 3D NAND**

>3X Extended

- The Reliability Issues of 3D NAND Flash

- The Architecture of Error Handling Technology

- Error Correction Technology

- Comparison between ECC engines

- Reliability of SSD with 3D NAND Flash memory

- Conclusion

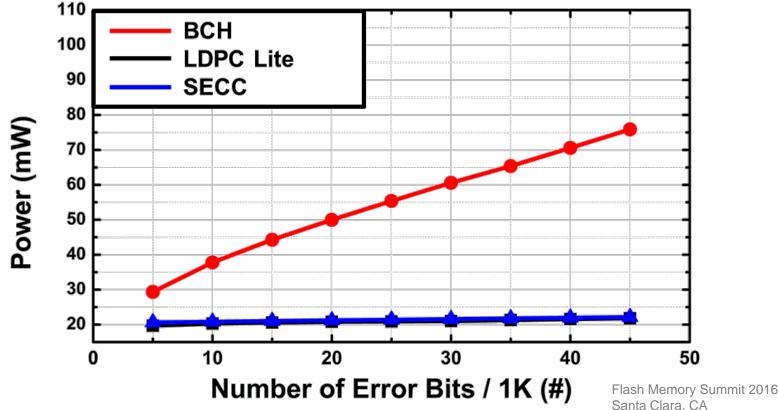

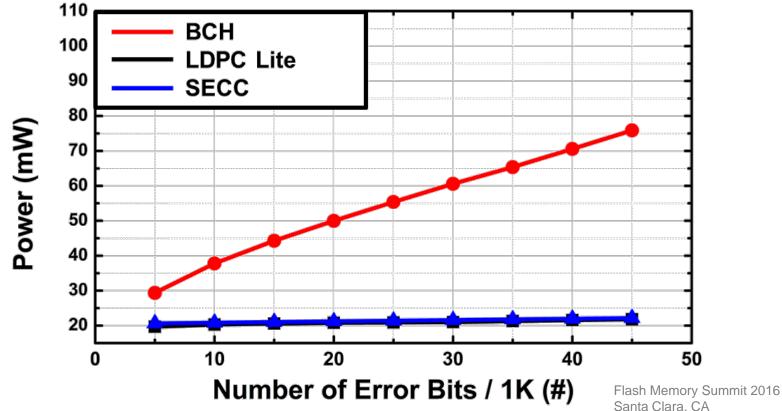

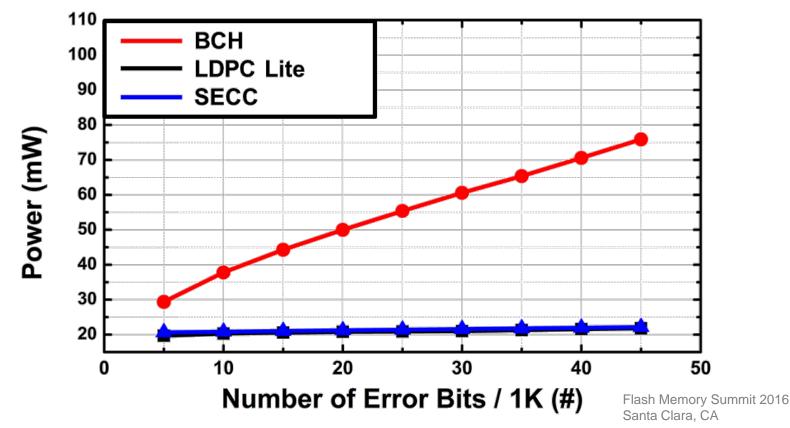

- The power consumption of the LDPC lite and SECC engine are only 1/3 than the convention BCH.

- With the novel design of decoding algorithm, the cost of LDPC can be reduced effectively.

- The endurance of 3D NAND Flash can be 3X more extended by SECC and LDPC lite with DSP engine.

# Flash Memory Meet us at booth 714 & 716

Media Contact: Leo Huang Director of Product Marketing <u>leo\_j\_huang@phison.com</u>

Sales & Marketing Contact: Michael Wu GM, Phison American Business Div. michael\_wu@phison.com

Investor Contact: Hawk Kuan Chief of Staff, IR and Strategy hawk\_kuan@phison.com