# Can Next-Generation 3D TLC NAND Extend Enterprise Applications?

\*Thomas J Griffin, \*Patrick Breen, \*Gary Tressler, \*\*Nikolaos Papandreou \*IBM Systems – Poughkeepsie, NY, USA \*\*IBM Research – Zurich, Switzerland

## Can Next-Gen 3D TLC NAND Extend Enterprise Applications?

The First Generation of commercially available 3D TLC NAND:

- Demonstrated viable solution for Enterprise use

- Enabled higher monolithic density and lower Cost/GB than 2D MLC

- Exhibited excellent Program-Erase cycling endurance

- However, also exhibited higher Data Retention error rates relative to 2D MLC

- Enterprise controller must adapt to manage new mechanism

Can the Next Generation of commercially available 3D TLC NAND improve on First Generation?

- In 2D MLC NAND, newer generations exhibited lower cycling endurance

- 2D NAND scaling relies on shrinking ground rules (increased CCI)

- 3D NAND scaling relies on increased word layers

#### Scope of Sampling

- First Gen 3D TLC NAND: best commercially available NAND flash at CS level (32-48 Layer)

- Next Gen 3D TLC NAND: best commercially available NAND flash at ES level (64-72 Layer)

#### Parameters of Testing

- Arrhenius-based acceleration of PE Cycling and Data Retention bake

- (use of Activation Energy E<sub>a</sub>)

- Target use case @40C

- All voltage read offsets moved simultaneously during characterization

- Quick 1<sup>st</sup> order approximation of Optimal V<sub>READ</sub> shift

- Independent V<sub>READ</sub> level shifting required for true optimal

#### Value Proposition

• There is value to common methodology employment across manufacturers/technologies

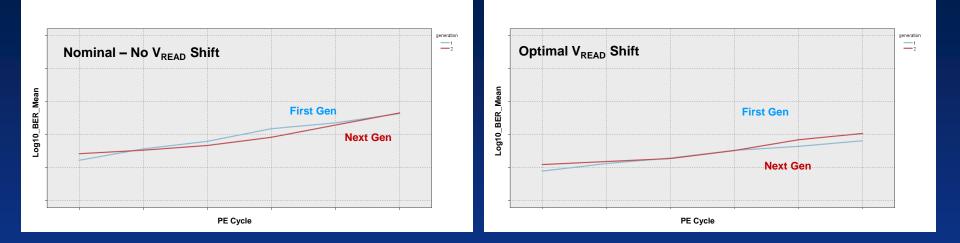

# 3D TLC NAND: First Gen v Next Gen – PE Cycling

Next Gen ES Shows Similar PE Cycling Endurance as First Gen CS

- Next Gen showing some indication of higher BER trajectory with increased PE cycling

- Next Gen CS should maintain or improve cycling endurance over ES

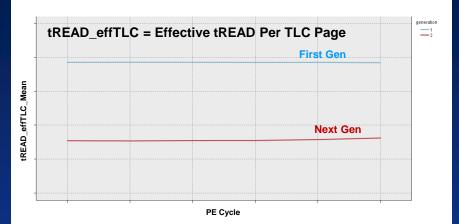

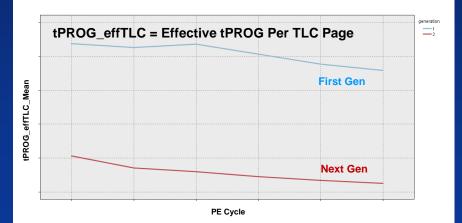

### 3D TLC NAND: First Gen v Next Gen – tREAD, tPROG

## Significant (~25%) improvement in both tREAD and tPROG for Next Gen

Next Gen CS tREAD/tPROG may increase over ES in trade-off for increased endurance

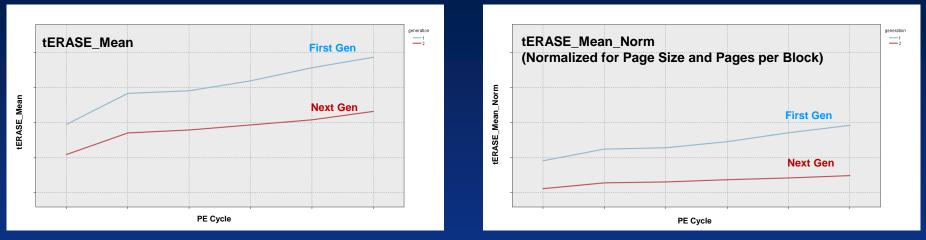

Significant (33-50%) improvement in tERASE for Next Gen

Next Gen CS tERASE likely similar to ES

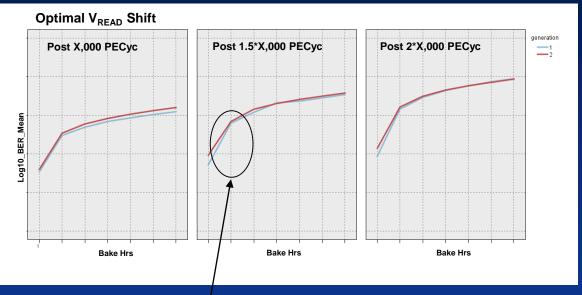

Next Gen ES shows similar post cycle Data Retention BER as First Gen CS

Consistently observe spike in BER at beginning of retention

- Spike in BER due to rapid shift in optimal V<sub>READ</sub> thresholds

- Fast V<sub>READ</sub> threshold shifts must be accommodated in Enterprise applications

Santa Clara, CA August 2017

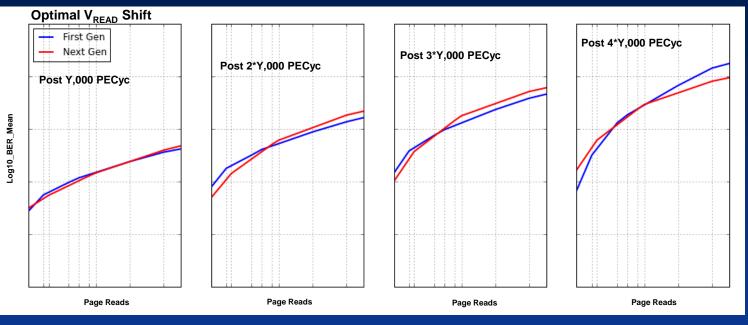

Next Gen ES shows similar post cycle Read Cycling BER as First Gen CS

Santa Clara, CA August 2017

Next-generation 3D TLC NAND continues to be viable solution for Enterprise use

- Comparable PE Cycling endurance, post cycle DR, post cycle Read Cycling to First Gen

- Short-term Data Retention continues to be a challenge

- Significantly improved array timings over First Gen

Initial conclusions based on Next Gen ES performance

• Final Next Gen CS performance may vary based on endurance/timing trade-offs

<u>Contact:</u> Thomas J Griffin tgriff@us.ibm.com

Santa Clara, CA August 2017