### ReRAM Technology, Versatility, and Readiness

Hagop Nazarian VP of Engineering & Cofounder

- Introduction to ReRAM

- ReRAM Technology Attributes

- Scalability

- Ease of integration with CMOS

- Architectural Flexibility

- Energy reduction

- 40nm ReRAM Product results

- Performance

- Endurance

- Retention

- Status & Conclusion

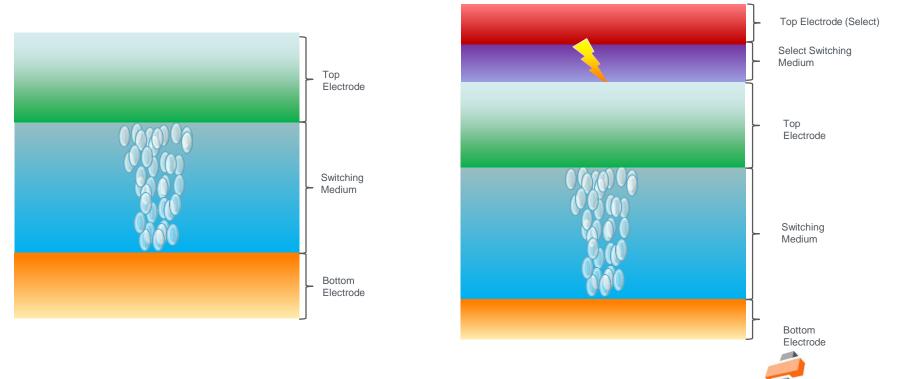

## Filamentary ReRAM technologies leads to a simple yet powerful non-volatile technology

Flash Memory Summit 2017 Santa Clara, CA CROSSBAR

Santa Clara, CA

#### Wide range of applications with ReRAM

Crossbar ReRAM Cell

#### Crossbar Selector

#### Crossbar SR Cell

## **ReRAM Technology Attributes**

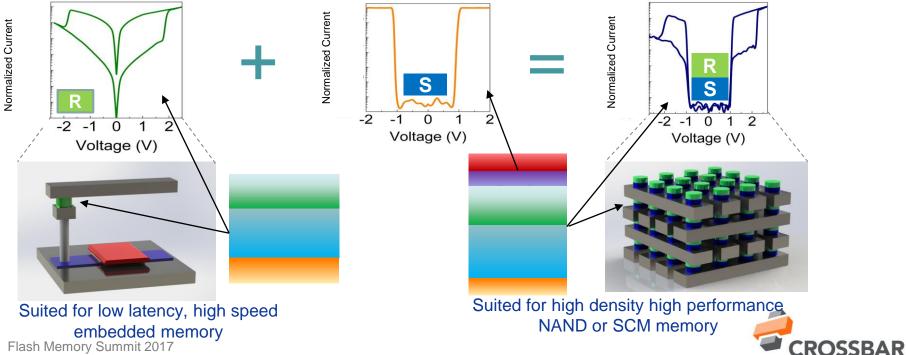

#### ReRAM performance improves with scaling

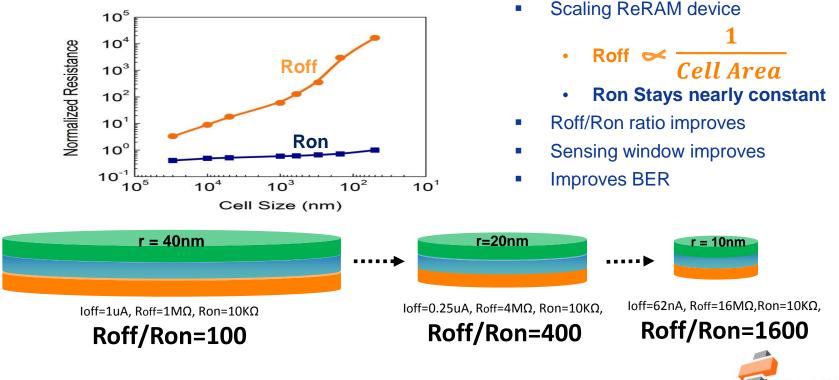

### Ease of integration with CMOS

- Back-end process No impact to CMOS transistors

- ReRAM located between metal layers

- Adds only 1 to 2 masks & 8 processing steps

- 32% lower cost

- Smaller die size

# ReRAM enabling scalability, performance, monolithic integration

| <b>Conventional Flash</b>              | ReRAM                                     | Architectural Advantages                                            |  |

|----------------------------------------|-------------------------------------------|---------------------------------------------------------------------|--|

| 4 terminal device<br>D/G/S/Substrate   | 2 terminal device                         | Smaller device<br>Simpler to operate                                |  |

| Common substrate                       | Has no common terminal                    | Allows Byte alterability<br>Byte Write                              |  |

| Front-end<br>Impacts CMOS transistors  | Back-end                                  | Area efficiency<br>No impact on CMOS transistors                    |  |

| Requires additional HV<br>transistors  | No HV transistors needed                  | Much easier to design and integrate with CMOS and uses 1 or 2 masks |  |

| Scaling Limitations or<br>Degradations | No Scaling limitations or<br>Degradations | Well Suited for advanced nodes<br>Monolithic integration with CMOS  |  |

#### Major system energy reduction with ReRam

| Energy consumption ratio NAND/ReRAM based on SSD & NVDIMM-P |            |           |           |              |           |           |  |

|-------------------------------------------------------------|------------|-----------|-----------|--------------|-----------|-----------|--|

|                                                             | SSD        |           |           | NVDIMM-P     |           |           |  |

|                                                             | 512B Write |           | 64B Write |              |           |           |  |

|                                                             |            |           | ReRAM     |              |           | ReRAM     |  |

| Write                                                       | NAND based |           | Energy    | NAND based   |           | Energy    |  |

| Amplification                                               |            | ReRAM(nJ) | Reduction | NVDIMM-P(nJ) | ReRAM(nJ) | Reduction |  |

| 1                                                           | 53056      | 21504     | 2X        | 53056        | 2688      | 20X       |  |

| 2                                                           | 70947      | 21504     | 3X        | 70947        | 2688      | 26X       |  |

| 3                                                           | 88838      | 21504     | 4X        | 88838        | 2688      | 33X       |  |

| 4                                                           | 106729     | 21504     | 5X        | 106729       | 2688      | 40X       |  |

- ReRAM based SSD provides 2X to 5X energy reduction

- ReRAM based NVDIMM provides 20X to 40X energy reduction

## **ReRAM Product Array Results**

Performance

Endurance

Retention

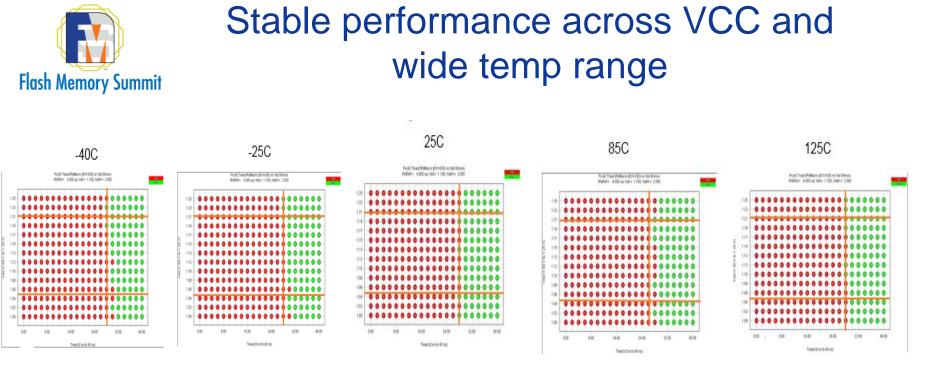

Superior Speed stability across temperature and VCC is established

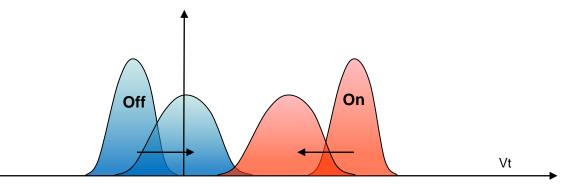

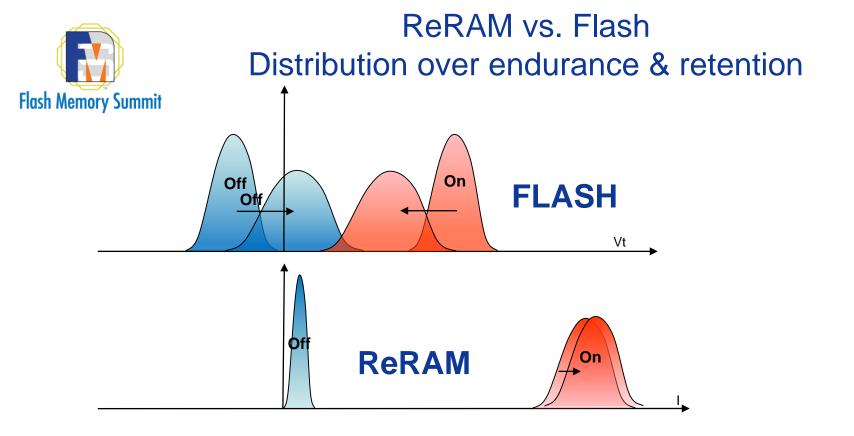

#### Problems with aging Flash technology

- Flash distributions widens

- Flash distribution gap closes increasing BER

### 300K endurance cycles with no degradation

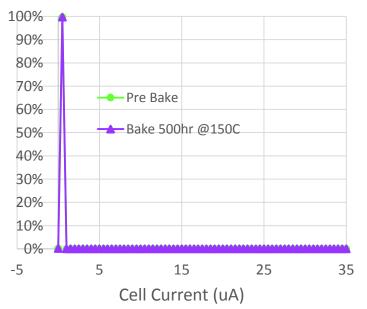

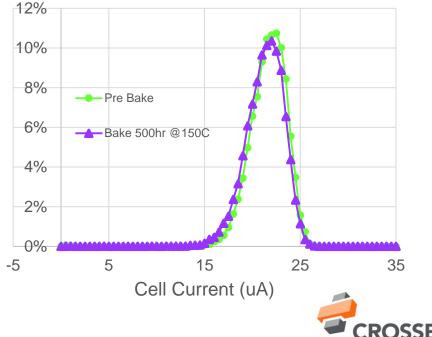

Flash Memory Summit 32Kb Endurance Cycling 32Kb Endurance Cycling 12% 100% Cycle 0 Cycle 0 90% Cycle 10 Cvcle 10 10% 80% -Cycle 100 -Cycle 100 NAND 70% -X-Cycle 1K 8% <mark>-Ж-</mark>Cycle 1K ₄ 60% Cvcle 10K 50% 6% NOR Flash Cycle 50K -Cvcle 50K 40% Cycle 100K 4% Cycle 100K 30% Cycle 200K Cycle 200K 20% 2% Cycle 300K Cycle 300K 10% -0% 0% -5 5 15 25 35 -5 15 25 35 5 Cell Current (uA) Cell Current (uA)

- ReRAM "On" and "Off" Distribution width stayed the same !!!

- ReRAM "On" and "Off" Distribution gap increased !!!

#### ReRAM Distribution gap & width does not close or widen!!

RO

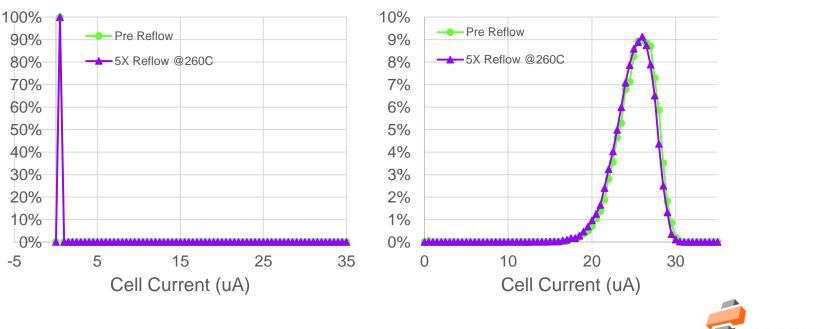

## ReRAM distribution is unchanged after 5X solder reflow retention test

**Reflow Retention**

BUCC

**Reflow Retention**

# ReRAM retention post 10K cycles is solid – No changes

32Kb Data Retention (Post 10K Cycle)

32Kb Data Retention (Post 10K Cycle)

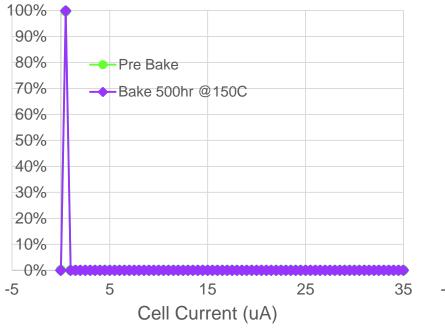

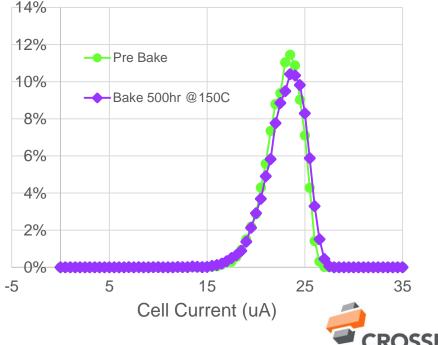

#### ReRAM retention post 300K cycles is solid – No changes

32Kb Data Retention (Post 300K Cycle)

32Kb Data Retention (Post 300K Cycle)

### ReRAM is here and ready for the future

- ✓ Impressive reliability with robust retention post 10K & 300K endurance cycles

- ✓ ReRAM distributions remain stable post 5X Solder reflow

- ✓ Consistent ReRAM array performance across temperature (-40, 125C) and VCC range

- ✓ Starting production with SMIC for ReRAM customer designs

- ✓ 2X node ReRAM integration in progress

- ✓ Already started 1X node ReRAM design with customer