#### Adapting Controllers for STT-MRAM Joe O'Hare Everspin Technologies, Inc. CTRL 301-1 Flash Controller Design Options Room: GAMR2 8:30 – 10:50AM August 9, 2018

### Adapting Controllers for STT-MRAM

- MRAM Overview

- Persistent SRAM and Persistent DRAM

- Choosing an Interface

- What's the same, what's not

- Controller Design Considerations

- Xilinx Memory Interface Generator (MIG) optimization

- Additional design tips to get full benefit of MRAM

- Summary

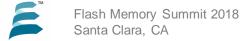

### MRAM – High Performance With Persistence

MRAM Combines Performance of Memory with Persistence of Storage

- High Performance: DRAM-class

write performance

- Non-Volatile: Maintains memory without power

- Fast Write Speeds: Similar to SRAM and DRAM

- Superior Durability: Survives memory workloads

- No Refresh: Data requires no charge

### Choosing an Interface for MRAM

- Familiar Standards for Toggle MRAM

- SRAM- asynchronous with standard parallel I/O

- Serial- SPI and multi variants (Single, Quad)

- Persistent DRAM with STT-MRAM

- JEDEC DDR3 > ST-DDR3

- DDR3 Controllers need to be adapted

# ST-DDR3 has some timings differences vs. the JEDEC standard

| Parameter                                     | Symbol |          | 3-1333<br>AM |          | R3-1333<br>//RAM |

|-----------------------------------------------|--------|----------|--------------|----------|------------------|

|                                               |        | ns (min) | ck (min)     | ns (min) | ck (min)         |

| ACTIVE to internal READ or WRITE delay time   | tRCD   | 15       | 10           | 95       | 64               |

| Precharge command period                      | tRP    | 15       | 10           | 66       | 44               |

| ACTIVE to ACTIVE command period               | tRC    | 51       | 34           | 170      | 114              |

| ACTIVE to Precharge command period            | tRAS   | 36       | 24           | 103      | 69               |

| Write Recovery, WRITE to Precharge delay time | tWR    | 15       | 10           | 15       | 10               |

| ACT to ACT Command Period, different banks    | tRRD   | 6        | 4            | 30       | 20               |

| Four ACTIVE Window                            | tFAW   | 30       | 20           | 120      | 80               |

| REFRESH to ACT command delay (1Gb to 8Gb)     | tRFC   |          | 74 – 234     |          | Not Used         |

- Row latency, tRCD, and Precharge, tRP, are longer typically outside the register range for these timings in most DDR3 controllers.

- Refresh is not required

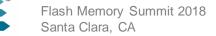

#### Page Size is Reduced for ST-DDR3

- DRAM Page sizes are optimized around REFRESH

- MRAM does not use REFRESH

- MRAM Page sizes are optimized to minimize power

#### Fewer Column Address bits

- DRAM Column Addr = 10b

- MRAM Column Addr = 6b

| Parameter (bits)              | JEDEC<br>DDR3   | 256Mb<br>ST-DDR3 |

|-------------------------------|-----------------|------------------|

| IO Width                      | x8              | x8               |

| Page size                     | 8,192           | 512              |

| tRASf                         | 3               | 6                |

| TXN_FIFO_DEPTH                | 4               | 8                |

| TXN_FIFO_PWIDTH               | 2               | 3                |

| CAS_FIFO_DEPTH                | 4               | 8                |

| CAS_FIFO_PWIDTH               | 2               | 3                |

| trcd_cntr/trcd_cntr_nxt       | 4               | 6                |

| trp_cntr                      | 5               | 7                |

| tras_cntr_rb/tras_cntr_rb_nxt | 4               | 6                |

| Column Address Width (bits)   | $A_0 - A_9(10)$ | $A_0 - A_5$ (6)  |

## Flash Memory Summit Power-up with Persistent Data

- DRAM Controllers will calibrate after power-up by writing to the memory. With persistent memory, care must be taken to not overwrite user data.

- Mode register 2, bit 8 MR2[8] on the ST-DDR3 MRAM is used to provide a way to write to the device without overwriting user data.

- 1. Mode Register 2 (MR2) 0x0110 MR2[8] = 1

- 2. Mode Register 3 (MR3) 0x0000

- 3. Mode Register 1 (MR1) 0x0044

- 4. Mode Register 0 (MR0) 0x0b60

- 5. After Calibration and before normal operation

- 6. Mode Register 2 (MR2) 0x0010 MR2[8] = 0

### **Power-down with Persistence**

## When power rail begins to: slump, over voltage, over current, over temperature

#### **SCRAM Routine**

- 1. Stop accepting any new commands

- 2. Process all pending commands

- 3. Complete all pending MRAM writes

- a) NOTE: To guarantee persistence, executing a Precharge (PRE) or Precharge All (PREA) command must be performed to move data in to the persistent memory array.

- 4. Communicate that ALL pending writes are complete (assert **SCRAM\_complete**)

- 5. It is now safe to power off MRAM without losing data.

### Summary of Changes to Xilinx MIG

| Category    | STT-MRAM Timing Parameter and<br>Performance Changes      | ddr3_0.sv | ddr3_0_ddr3.s<br>v | ddr3_0_ddr3_<br>mem_infc.sv | ddr3_v1_4_cal.<br>sv | ddr3_v1_4_mc.<br>sv | ddr3_v1_4_mc<br>_arb_mux_p.sv | ddr3_v1_4_mc<br>_group.sv | ddr3_v1_4_mc<br>_ref.sv | ddr3_v1_4_ui.s<br>v | ddr3_v1_4_ui_<br>rd_data.sv | ddr3_v1_4_ui_<br>wr_data.sv |

|-------------|-----------------------------------------------------------|-----------|--------------------|-----------------------------|----------------------|---------------------|-------------------------------|---------------------------|-------------------------|---------------------|-----------------------------|-----------------------------|

|             | File Number                                               | 1         | 2                  | 3                           | 4                    | 5                   | 6                             | 7                         | 8                       | 9                   | 10                          | 11                          |

| Timing      | Timing settings and counter width changes                 |           | x                  |                             |                      | x                   | x                             | x                         |                         |                     |                             |                             |

| Power-up    | Anti-scribbling changes (NOMEM mode)                      |           |                    |                             | x                    |                     |                               |                           |                         |                     |                             |                             |

| Power-down  | SCRAM input signal to drain writes with CAS page closes   | x         | x                  | x                           |                      | x                   |                               |                           | x                       |                     |                             |                             |

| Power-down  | Created SCRAM output status signals                       | x         | x                  | x                           |                      | x                   |                               | X                         |                         | X                   |                             |                             |

| Performance | Auto pre-charges on the 8 <sup>th</sup> BL8 of a CAS page |           | x                  |                             |                      | x                   |                               |                           |                         | x                   | x                           | x                           |

| Performance | FIFO-DEPTH doubled                                        |           |                    |                             |                      |                     |                               | x                         |                         |                     |                             |                             |

| Performance | Changed to emit requests faster                           |           |                    |                             |                      |                     |                               | x                         |                         |                     |                             |                             |

#### Performance

#### Note the Large gaps between bursts

| _                    | titled 1* | × ddr3          |                 |          |              |      |           |        |         |                   |          |             |                         |            |             |         |          | ? 🗆       |

|----------------------|-----------|-----------------|-----------------|----------|--------------|------|-----------|--------|---------|-------------------|----------|-------------|-------------------------|------------|-------------|---------|----------|-----------|

| Q 💾 🔍 Q 💥            | . ⇒[  ∢   | <b>▶</b>     10 | <u>e   er  </u> | +F   T+  | •   •        | [⊷]  |           |        |         |                   |          |             |                         |            |             |         |          |           |

|                      |           |                 |                 |          |              |      |           |        |         |                   |          |             |                         |            |             |         |          |           |

| Name                 | Value     | 1               | 9,400 ns        | 9        | ,600 ns      |      | 9,800 ns  |        | 10,000  | nș                | 10,200   | ,nș         | 10,400                  | nș         | 10,600 n    | s       | 10,800 r | nș 1      |

| 😼 sys_clk_i          | 1         | הההההה          | hinininin       | nininin  | ່າກ່າກກາກກ່າ | UUUU | ninininin | ininin | nininin | TTE AUT           | TTTT / T | ົບບົບບົບບໍ່ | hhhhh                   |            | າດກາດກາດກາດ | ininini | nininir  | ຫ່ວ່າກ່ານ |

| 谒 sys_rst            | 0         |                 |                 |          |              |      |           |        |         |                   |          |             |                         |            |             |         |          |           |

| ♥ c0_ddr3_a0][15:0]  | ffff,ffff |                 | ff              | ¥ ff     |              | ff   |           |        | ff      | ff                |          | ff          | ff                      | Ж          | <b>f</b> f  |         | (f)      | ff        |

| ♥ c0_ddr3_b1:0][2:0  | 7,7       | 7,7             | 7,7             | 7,7      |              | 7,7  | 7,7       |        | 7,7     | 7,7               |          | 7,7         | 7,7                     | E (X       | 7,7 7,7     |         | 7,7      | 7,7       |

| V c0_ddr3_addr[15:0] | ffff      |                 | ffff            | X ffff   |              | ffff | ffff      |        | ffff    | <mark>ffff</mark> |          | ffff        | ffff                    | СЖ         | ffff        |         | ffff     | ffff      |

| ♥ c0_ddr3_ba[2:0]    | 7         | 7               | 7               | <u> </u> |              | 7    | X 7       |        | 7       | <u>≭_7</u> ∠      |          | 7           | 7                       | <b>2</b> X | 7 7 7       |         | 7        | 7         |

| 🖥 c0_ddr3_ras_n      | 1         |                 |                 |          |              |      |           | /      |         |                   |          |             |                         |            |             |         |          |           |

| 🔓 c0_ddr3_cas_n      | 1         |                 |                 |          |              |      |           |        |         |                   |          |             |                         |            |             |         |          |           |

| 🔓 c0_ddr3_we_n       | 1         |                 |                 |          |              |      |           |        |         |                   |          |             | $\overline{\mathbf{V}}$ |            |             |         |          |           |

| ♥ c0_ddr3_dq[71:0]   | ZZZZZZZ   | Z               | ZZZZ            | zzzzz.   |              | ZZZZ | zzzzz     |        | ZZZZZ   | 22222             |          | ZZZZZZ      | ZZZ                     | <b>Z</b> Z | zzzzzzzz.   |         | ZZZZ     |           |

| 🕏 c0_ddr3_dqs_n[8:0] | ZZZ       | ZZZ             |                 | zzz      |              |      | ZZZ       |        |         | ZZZ               |          | Z           | zz                      |            | ZZZ         |         |          | zzz       |

| 😼 c0_ddr3_dqs_p[8:0] | ZZZ       | ZZZ             |                 | zzz      |              |      | ZZZ       |        |         | ZZZ               |          | Z           | ZZ                      |            | ZZZ         |         |          | zzz       |

| ADDR_WIDTH[31:0]     | 00000010  |                 |                 |          |              |      |           |        |         | 0000001           | 0        |             |                         |            |             |         |          |           |

|                      |           |                 |                 |          |              |      |           |        |         |                   |          |             |                         |            |             |         |          |           |

|                      |           |                 |                 |          |              |      |           |        |         |                   |          |             |                         |            |             |         |          |           |

#### Performance – improved bus utilization

| Name                   | <b>¢</b> ▼ Cursor | Q.             | ,420ns |          | 112,440n | 8    | 112,460 | ns     | 112,480 | ns   | 112,500 | ins <sub>.</sub> | 112,5  | 20ns     | 112,540              | )ns     | 112,   | 560ns   | 112,58  | Ons          | 112,    | 600ns   | 112,620n | ns                       |

|------------------------|-------------------|----------------|--------|----------|----------|------|---------|--------|---------|------|---------|------------------|--------|----------|----------------------|---------|--------|---------|---------|--------------|---------|---------|----------|--------------------------|

|                        | 1                 |                |        |          |          |      |         |        |         |      |         |                  |        |          |                      | 7       |        |         |         |              |         |         |          |                          |

| 🗄 🛲 c0_ddr3            |                   |                |        |          |          |      |         |        |         |      |         |                  |        |          |                      |         |        |         |         |              |         |         |          |                          |

|                        | e 1               |                |        |          |          |      |         |        |         |      |         |                  |        |          |                      |         |        |         |         |              |         |         |          |                          |

| 🔤 c0_ddr3_ck_p(0)      | 0                 |                |        | M        |          | MU   |         |        |         |      |         |                  | MU     |          | 107 <mark>/</mark> 0 |         |        |         |         |              |         |         | MMM      | nnn                      |

| ⊕ 🜆 c0_ddr3_ba[2:0]    | 'ከ 7              |                | 7      |          |          | ) (7 | ) (1    | ))/7   | ) //    | ) /1 | ))7     | ))7              | ))7    |          |                      |         |        |         |         |              |         |         |          |                          |

| ⊕ 🕼 c0_ddr3_addr(15:0) | 'h FFFF           |                | FFFF   | FFF      | F        | 0000 | 0000    | 0000   | ) (0000 | 0000 | 0000    | 000              | 0 00   | 00 FFFF  | 0000                 | ) (00   | 00 0   | 000 0   | )00 000 | 0 ) ( ) ( 0( | )00 \ 0 | 000 🔪 0 | 000 FFFF |                          |

|                        | 1                 |                |        |          |          |      |         |        |         |      |         |                  |        |          |                      | Т       |        |         |         | Т            |         |         |          |                          |

|                        | 1                 |                |        |          |          |      |         |        |         |      |         |                  |        |          |                      |         |        |         |         |              |         |         |          |                          |

| 🔤 c0_ddr3_ras_n        | 1                 |                |        |          |          |      |         |        |         |      |         |                  |        |          |                      |         |        |         |         |              |         |         |          |                          |

| 🔤 c0_ddr3_cas_n        | 1                 |                |        |          |          | Г    | Г       | Г      | Г       | Г    | Г       | Г                | Ъ      | /        |                      | Г       |        |         |         | Ъ            |         |         |          |                          |

|                        | 1                 |                |        |          |          | U    | U       | T      |         | l    | T       |                  |        | <u> </u> |                      | T       |        |         |         | Т            |         |         |          |                          |

| ⊡¶ (0_ddr3_dq[71:0]    | 'h zz_zz          | 222222_2222222 | 22_22  | 222222_2 |          |      | -000    |        |         |      |         | 000000           | 00000  |          |                      | 22){()) | 000000 |         | 0000000 | 00000        |         | 00000   |          | )))) <mark>22_222</mark> |

| € 👍 c0_ddr3_dqs_p(8:0) | 'h zzz            |                | 222    |          |          |      | -0000   | 000000 |         |      |         | 00000            | 000000 |          |                      |         | 000000 | 0000000 |         | 00000        | 000000  | 000000  |          | ()(() <del>222</del>     |

|                        |                   |                |        |          |          |      |         |        |         |      |         |                  |        |          |                      |         |        |         |         |              |         |         |          |                          |

#### Don't Reinvent the Wheel

| nemory v | com is the w<br>rendor partne<br>emory comp | ers, the eMemor             | id most complete inform<br>y infrastructure include<br>g new and emerging Di  | s a fully searchab         | le database of da    | atasheets, specificati | ons and simul | ation models for        |     |

|----------|---------------------------------------------|-----------------------------|-------------------------------------------------------------------------------|----------------------------|----------------------|------------------------|---------------|-------------------------|-----|

| Home     | My Cart                                     | My Download                 | ls Enterprise Annot                                                           | ations Enterpr             | ise Downloads        | Enterprise Monito      | rs            |                         |     |

|          | My Favorite                                 | Searches                    | Add this search                                                               |                            |                      | c                      | an't find a p | art? Make a rec         | que |

| Help E   | x: vendor<br>DRAMs: Syn                     | =MICRON,SAMS<br>nch Devices | :: Synch Devices;E<br>UNG;width=32bit;CA<br>Iimit to a type<br>(classes in th | S Latency 5=t<br>of memory | Vendor<br>Data Width | SearchAll All Widths   | S             | ize: min @Mb<br>max 1Tb |     |

| Add      | Vendor -+                                   | Ciam Co                     | réquision                                                                     | Part Number                | Downloa              | ads MMAW/VIPCAT Requir | ed Annota     | Compare                 | ]   |

| . All    | vendor.                                     | 6 more parts                | n red is available to<br>available under ND.                                  |                            |                      |                        |               |                         | rť  |

|          | EVERSPIN                                    | ST_MRAM 25                  | onto (4M x 8 bit x 8 bank)                                                    | EMD3D256M-                 |                      | 3.3.036 / 11.30.034    | -9+           | 0                       |     |

| 10       |                                             |                             |                                                                               |                            |                      |                        | -8+           |                         |     |

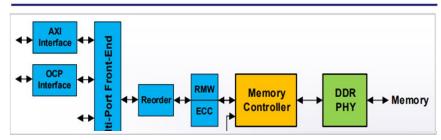

#### <sup>T</sup> Memory Interface Solution Overview

#### Solution Includes:

- Memory Controller Cores

- Supports HBM2, GDDR6, DDR4/3, LPDDR4/3 and MRAM

- 64 banks and 16 deep command queue support

#### **Key Features:**

- Complete Solution

- Full featured and modular solution enables IP to be configured to exact customer requirements

### Adapting Controllers for STT-MRAM

#### Summary

- Timing and page size changes needed for ST-DDR3

- Performance optimization in Xilinx MIG DDR3 with sequencing, FIFO depth and address ordering

- Power Up and Power Down simplified

- Persistent user data in memory needs to be accounted for

- Resources are available

- Xilinx MIG support and design guide

- ASIC design support from Cadence and Northwest Logic