# MRAM: Memory for the Edge... And Beyond

### Jeff Lewis SVP Business Development

Santa Clara, CA August 2018

# Intelligence Is Moving to the Edge

### Edge AI Required When:

Latency Unacceptable Communication Power Privacy Concerns Localized Training

ADAS, Robotics, Security, Industrial Process Local Processing more efficient than transmission GDPR, HIPAA, Surveillance Local surveillance, Google Federated Model, other

emerging NN architectures

Devices must get more sophisticated to prevent Fraud, Hacking, Mischief - Next step is Personalization -- Voice → MY Voice

# **Edge AI:** Smarter = Power Hungry

- Complex local computation

- E.g., Facial recognition, ADAS, Surveillance

- SRAM size/power grows as computation grows

- Or add external DRAM...

- Power consumption huge challenge

- Limits model sophistication

- Large battery

- Heat effects wearables, cameras

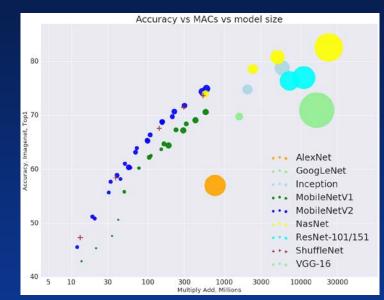

Accuracy of ImageNet classification versus neural net complexity – showing reducing complexity (and power) by 10x reduces accuracy by 15-20% (source Google MobileNet V2)

# Thanks for the Memories

- Edge AI Is All About (RAM) Memory

- "Never Enough Memory"...

- Most AI Chip Energy and Die Area consumed by Memory

- Han, ISCA 2016, many others

- ... And it better be On-chip

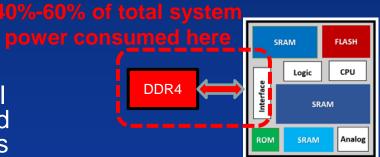

- Google study\*: 40%-60% of total mobile system energy consumed in DRAM ← → Chip data transfers

### *"Memory is one of the biggest challenges in deep neural networks (DNNs) today."* -- GRAPHCORE

HOW TO SOLVE THE MEMORY CHALLENGES OF DEEP NEURAL NETWORKS

#### Memory Holds the Key to Artificial Intelligence

\_avering Intel<sup>®</sup> Optane™ between SSD and RAM keeps more data closer to memory, making it readily available for AI initiatives.

🏠 by Karen Krivaa 肖相译 · May. 25, 18 · Al Zone · Opinion

\*Boroumond, Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks, © 2018

# App-Targeted MRAM for SoC's

10-15ns R/W **SRAM Replacement**  $>10^{13}$  cycles SRAM LLC, AI, DDI, many others Days-months retention High Speed & 25-50ns R/W Endurance NVM >10<sup>11</sup> cycles NVM IoT, Edge AI >10 years retention Foundry NVM MTJ Foundry SRAM MTJ 25ns Rd / 50-500ns Wrt eNVM 10<sup>6-8</sup> cycles NVM eFlash replacement >10 years retention Retention 10+ years

Endurance

∞ŏ

Speed

# **MRAM Replaces SRAM**

\* R. de Werdt et al., IEDM 1987; R.D.J. Verhaar et al., IEDM 1990; S.H. Kang et al., IEDM17

MEMORY

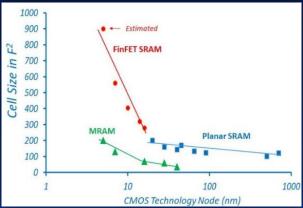

**SIZE:** 1T-bitcell – MRAM block 70%-80% smaller than SRAM

✓ LEAKAGE: No bitcell leakage

✓ **BEOL:** Simple Integration

✓ NO S.E.U.: Rad hard bitcells

✓ **PERSISTENT**: Data retained

## MRAM Materially Improves Edge AI

### **Challenge**

### **MRAM Solution**

| Lots of On-Chip RAM   | MRAM ¼ Size of SRAM → 4x More Memory in Same Footprint                                               |

|-----------------------|------------------------------------------------------------------------------------------------------|

| Lowest Possible Cost  | Size vs. SRAM<br>Low-cost BEOL Adder vs. Flash<br>Execute-in-Place Merged NVM + RAM                  |

| Lowest Possible Power | MRAM Low Write Energy<br>MRAM Persistence – No Leakage vs. SRAM<br>Easy + Efficient Sleep Management |

| Many Updates          | MRAM 100x – 10,000x Lower Write Power than<br>Flash, and Much Higher Endurance                       |

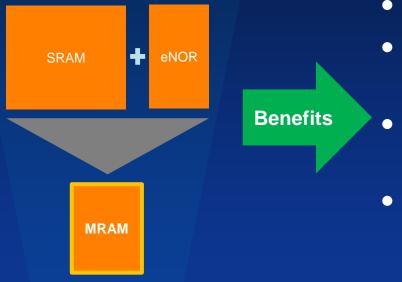

### MRAM Unified Execute-In-Place Memory

#### Merge SRAM + Flash

- ↓**Cost**: Much smaller die area

- ↓Cost: MRAM wafer cost

lower than flash wafer cost

- ↓Power: Eliminates memory data transfer latency + power

**Lifetime**: Enables frequent data updates, data logging, other write-intensive NVM

### Merged NVM + SRAM for up to ~40MHz Operation

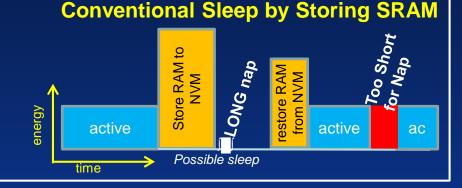

### MRAM Maximizes Sleep Cycles More Sleep = Longer Battery Life

- Going in / out of sleep burns energy

- Mostly storing / reloading SRAM

- Only sleep when: *EnergySavings*<sub>Sleep</sub> > EnergyCost<sub>LoadStore</sub> → Limits sleep to few, long periods

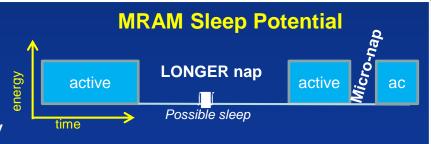

### Using MRAM instead of SRAM:

- Simply power memory off!

- Eliminates store/reload energy cost

- Enables frequent "Micro-Naps"

- save significant additional energy

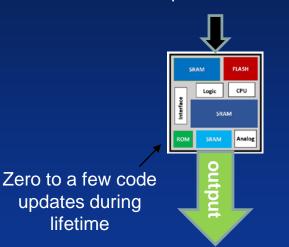

#### **Normal Processing Device**

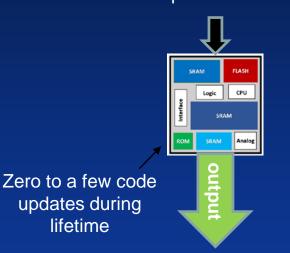

Code loaded to part at test

Flash write power + performance: No Problem

#### Normal Processing Device

Code loaded to part at test

Flash write power + performance: No Problem

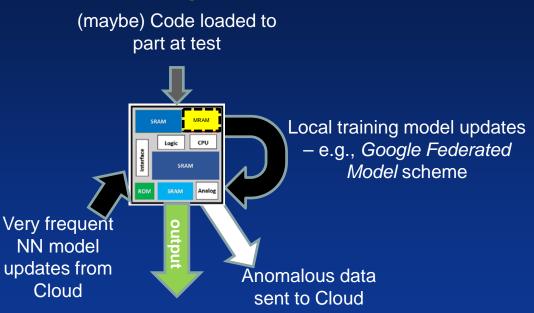

#### **"Smart" Edge Device**

Flash write power + performance: BIG Problem – MRAM 100-1,000X Better

Transformative memory → Enables applications other memories can't

• Will be as significant as SRAM and other memories

Will finally be able to answer the question: – Is this a Rabbit... or a Duck?