## MRAM Developers Day

August 2019

Martin Mason Sr. Director Leading Edge eNVM

#### 1 GF View of Market Dynamics and Strategy

#### 2 MRAM on 22FDX<sup>®</sup>

3 MRAM on 12LP+

#### 1 GF View of Market Dynamics and Strategy

#### 2 MRAM on 22FDX<sup>®</sup>

3 MRAM on 12LP+

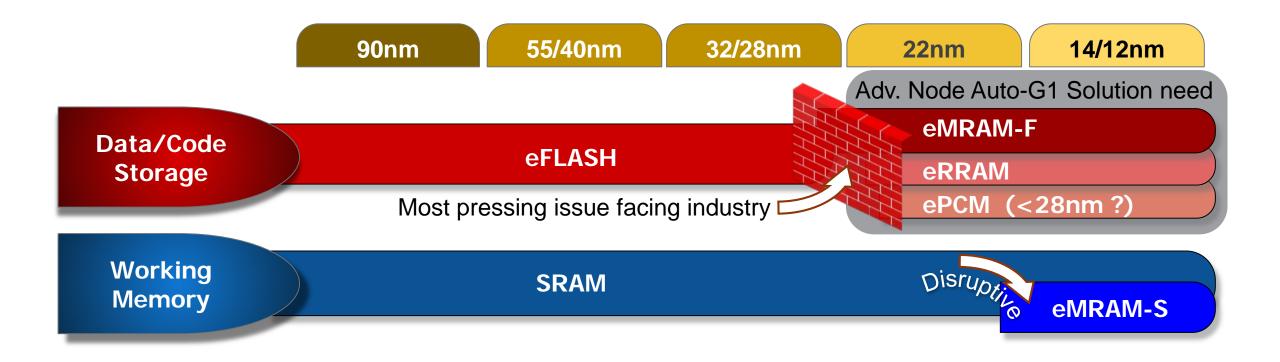

### Market Consensus: Memory challenges by Node

#### 1 GF View of Market Dynamics and Strategy

### 2 MRAM on 22FDX<sup>®</sup>

#### 3 MRAM on 12LP+

## MRAM Meets Growth Driver's Needs: High Density, Low Power Memory with 22FDX<sup>®</sup> Platform

- SOI ← Back Bias power optimization

- RF ← SOI efficiency

**Differentiated** and **optimized** for 'connected MCU based applications and emerging AI edge and AR

Development in IoT Computing

Leading clients applications: BTLE, IoT Wearables, Edge AI, Low power consumer, Low power ISM, Next generation GenPur MCUs Memory challenges by Node. General consensus in market.

28nm designs will stay with low-risk ESF3 eFLASH solution

- 28nm MRAM and PCM may struggle to get traction (too *risky*)

- 28nm PCM has burden of poor <28nm foundry roadmap

22nm MRAM-F from GF was architected to be as Flash like as possible

- Other 2x node MRAM solutions are more 'SRAM like' and less 'Flash like'

- 22FDX MRAM is robust (5x solder reflow) and has 2yr road-map to Auto-G1

- How about RRAM for eFLASH replacement at the 2x Node?

- Demonstrated 125C support? Auto-G1 roadmap?

### Value Proposition 22FDX<sup>®</sup> eMRAM-F: Like eFLASH – only better!

#### Next Best Alternative Analysis (Vs 28nm eFLASH):

- 3+1 MRAM masks Vs 11+ for eFLASH lower cost

- Better write speed

- Better endurance

- Better write power

- Better data retention (

- Roadmap to 1x nodes

- Paired with 22FDX SOI platform

| <u>Spec</u>         | 22FDX MRAM-F | <u>eFlash</u> |  |  |  |  |  |  |  |

|---------------------|--------------|---------------|--|--|--|--|--|--|--|

| Leakage             | 4            | 4             |  |  |  |  |  |  |  |

| Density             | 4            | 4             |  |  |  |  |  |  |  |

| Read Power          | 4            | 4             |  |  |  |  |  |  |  |

| Persistence         | 4            | 4             |  |  |  |  |  |  |  |

| Cost per bit        | 4            | 4             |  |  |  |  |  |  |  |

| 5X Reflow           | 4            | 4             |  |  |  |  |  |  |  |

| Adv Node Roadmap    | 4            | 1             |  |  |  |  |  |  |  |

| Mask Layers         | 4            | 1             |  |  |  |  |  |  |  |

| 22FDX Platform      | 4            | 1             |  |  |  |  |  |  |  |

| Write Speed         | 4            | 1             |  |  |  |  |  |  |  |

| Endurance           | 3.5          | 3             |  |  |  |  |  |  |  |

| Macro Support       | 3            | 3             |  |  |  |  |  |  |  |

| Read Speed          | 3            | 3             |  |  |  |  |  |  |  |

| Ext. temp support * | 3            | 4             |  |  |  |  |  |  |  |

| Write Power         | 3            | 2             |  |  |  |  |  |  |  |

| Maturity            | 2.6          | 3             |  |  |  |  |  |  |  |

1 = POOR

4 = GOOD

\* Auto Grade 1 MRAM target 1H 2021 Moves MRAM score to a 4

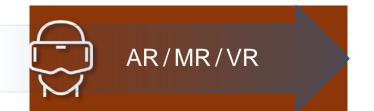

# Yield and Endurance

#### **Yield Data**

40Mb eMRAM  $t_0$  BER (< 6E-6) yield improvement trend over time.

Achieved 100% -yield at 6E-6 BER on some wafers. Average *Intrinsic* Yield in low 90's <u>without</u> ECC and Redundancy

### Endurance

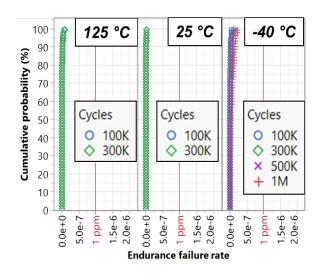

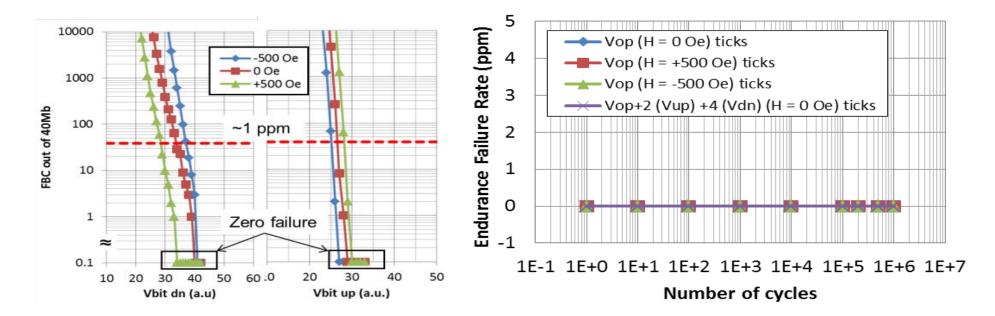

Endurance worse case is cold

Cycling endurance data of 40Mb eMRAM package parts at -40, 25 and 125° C after every interval of cycles up to 1M cycles.

All the parts passed endurance failure rate criteria of 1 ppm.

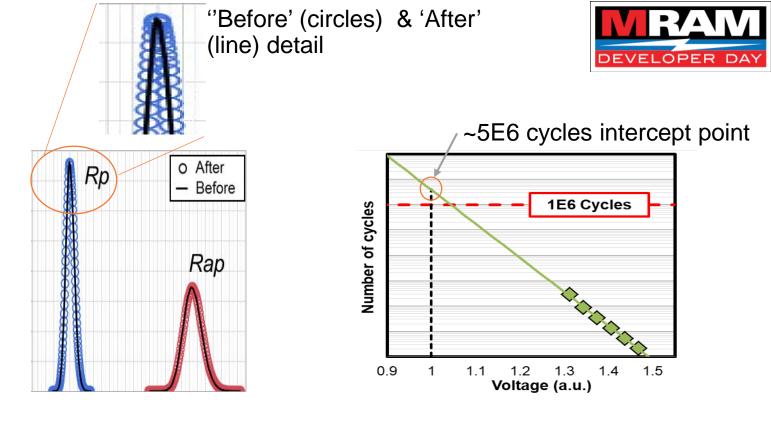

Bit-cell resistance distributions of  $R_p$  and  $R_{ap}$  states from 128Kb cell array before and after 1M endurance cycling.

No degradation in resistance observed after 1M endurance cycling. Projected number of cycles from TDDB (time dependent dielectric breakdown) data versus voltage at 25 ° C for failure rate of 1 ppm.

Macro has margin to endurance requirement of >1E6 cycles at  $V_{op}$ .

# Magnetic Immunity

GLOBALFOUNDRIES

### **MRAM Magnetic Immunity**

## eMRAM

## eFlash

eMRAM designers need to consider exposure to <u>strong</u> (DC) magnetic fields for data retention.

(minimal temp and endurance effects)

eFLASH designers need to consider endurance and temperature effects on data retention.

MRAM writing (and reading) in the presence of a strong magnet field needs to be considered

Active eFLASH write and read disturb need to be considered

### Magnetic Immunity ~600Oe @105° C 10Yrs

|                              | 25°C        | 125°C           |    |    |    |    |    |                  |    |    |    |    |    |    |

|------------------------------|-------------|-----------------|----|----|----|----|----|------------------|----|----|----|----|----|----|

|                              | 23 0        | Read bias (a.u. |    |    |    |    |    | Read bias (a.u.) |    |    |    |    |    |    |

| (D)                          | H-field\Vrd | 20              | 22 | 24 | 26 | 28 | 30 |                  | 20 | 22 | 24 | 26 | 28 | 30 |

| 0́<br>P                      | 0           | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |

|                              | 100         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |

| <u>e</u>                     | 200         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Р  |

| External magnetic field (Oe) | 300         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Р  |

|                              | 400         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |

|                              | 500         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Р  |

|                              | 600         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Р  |

|                              | 700         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Р  |

|                              | 800         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Р  |

| tel                          | 900         | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  | Р  |

| ш                            | 1000        | Ρ               | Ρ  | Ρ  | Ρ  | Ρ  | Ρ  |                  | F  | F  | F  | F  | F  | F  |

40500

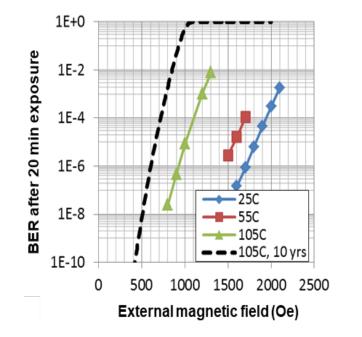

Stand-by magnetic immunity at 25, 55 and 105  $^{\circ}$  C for 20 min magnetic field exposure.

10 years projection shows 0.1 ppm failure rate below ~600 Oe at 105 ° C. Read disturbance shmoo data with magnetic field sweep at 25 and 125  $^{\circ}$  C

No read disturb up to 900 Oe at 125° C

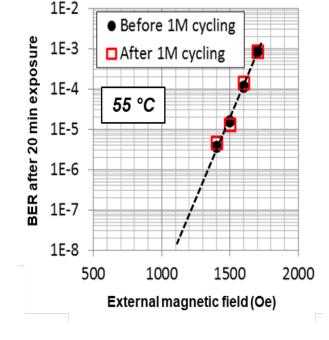

Stand-by magnetic immunity at 55 ° C for 20 min magnetic field exposure before and after 1M endurance cycling

No significant endurance induced changes in magnetic immunity observed

#### DEVELOPER DAY

### Writing MRAM in a Magnetic Field

WER (write error rate) plots of 40Mb eMRAM macro under zero, +/- 500 Oe field at 25  $^{\circ}$  C

**GF 22FDX MRAM can be written in** +/- 500 Oe magnetic field with no significant degradation to write error rate presence of +/- 500 Oe magnetic field (WER)

Cycling endurance data at -40  $^{\circ}$  C under zero and +/-500 Oe magnetic field to cover active mode magnetic immunity

No measurable effect on 1M cycle endurance failure rate during write in

## Magnetic Field Industry Spec.

<100 Oe is enough for most of normal uses</li>

\* The International Commission on Non-Ionizing Radiation Protection (ICNIRP)

\*\* European Union, IEC-61000-4-8, on the magnitude of magnetic fields that a device can experience under normal operation. The maximum value of 12.6 gauss

$Oe \rightarrow Oersted is 1000/4\pi$  ( $\approx 79.5774715$ ) amperes per meter. i.e. The H-field strength inside a long solenoid wound with 79.58 turns per meter of a wire carrying 1 A is approximately 1 oersted.

# Solder Reflow

GLOBALFOUNDRIES

### **Solder Reflow**

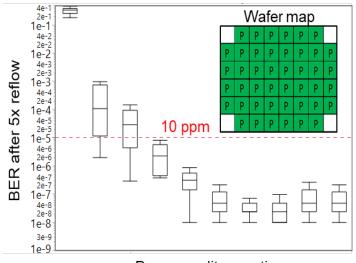

#### 260C x 1 min x 5 $\rightarrow$ 5x Reflow

Process splits over time

Post 5x reflows BER improvement trend for different MTJ processes.

Inset shows 100% 5x reflow performance across wafer for 10 ppm BER criteria

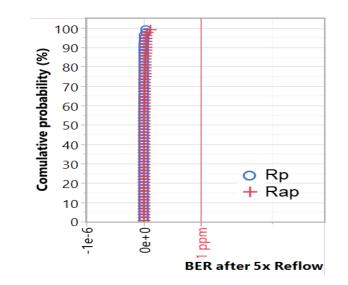

Post 5x reflow BER of 40Mb eMRAM package parts for  $R_p$  and  $R_{ap}$  states.

All the parts passed 1 ppm criteria after 5x reflow.

#### 1 GF View of Market Dynamics and Strategy

#### 2 MRAM on 22FDX<sup>®</sup>

3 MRAM on 12LP+

Memory challenges by Node. General consensus in market.

### **Disruptive** technology value...

- Clients seek *PPA reward* for technology & architectural risk

- Seeking >2x over incumbent tech in PPA (Pwr/perform/Area) metric

- Advance node eNVM bit cell size limited by drive transistor

### MRAM-S as SRAM replacement compelling on 12LP+

- 2x node MRAM-S >1/2 area SRAM-HD. Risk/Reward unfavorable

- 12LP+ MRAM-S <1/2 area SRAM-HD. Risk Reward favorable

- Power (Persistence & Area drive MRAM-S on 12LP+.

- Lwr Pwr./Heat as disruptive SRAM replacement technology

- Emerging use of MRAM-S for stochastic computing in AI/ML (?)

### Thank You

The information contained herein is confidential and the property of GLOBALFOUNDRIES and/or its licensors.

This document is for informational purposes only, is current only as of the date of publication and is subject to change by GLOBALFOUNDRIES at any time without notice.

GLOBALFOUNDRIES, the GLOBALFOUNDRIES logo and combinations thereof are trademarks of GLOBALFOUNDRIES Inc. in the United States and/or other jurisdictions.

Other product or service names are for identification purposes only and may be trademarks or service marks of their respective owners.

© GLOBALEOLINDRIES Inc. 2019. Unless otherwise indicated, all rights reserved. Do not conv.or redistribute excent

#### GLOBALFOUNDRIES