# MRAM Applications – Pros/Cons

- Panel Discussion

- Goal: Discuss upcoming MRAM Applications in Two Axes: Market and Performance

- Panelists:

- Mark Webb, President MKW Ventures

- Daniel Worlege, Distinguished RSM, IBM Research

- Terry Torng, Co-Founder, GyrFalcon

- Tetsuo Endoh, Prof. Tohoku Univ

- Tom Andre, VP Engineering, Everspin

- Jean-Pierre Nozieres, CEO, Antaios

- Two Domains:

- Market segments NVM / Unified / SRAM / AI / Auto, etc

- Performance axis Retention / Endurance / Cost / Scalability

• What is the main Market for MRAM in 2024?

• What are the Pros/Cons in Performance?

Chair: Satoru Araki

Market Segment

# Panelist Views 2019

|                  |                  | Mark                                                                                                             | Daniel                                                                                                                                                       | Terry                                                                                                                                              | Endoh                                                                                                                                                                                       | Tom                                                                                                                                 | Jean-Pierre                                                                                                                                                      |

|------------------|------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Market           | Target<br>Market | <ul> <li>Embedded, SOC,<br/>NOR/SRAM<br/>replacement</li> </ul>                                                  | <ul> <li>eNVM @ 105C</li> <li>eNVM @ 125C, solder reflow</li> <li>Mobile cache (10 ns)</li> <li>Last level cache</li> </ul>                                  | Edge AI and IoT, AI<br>for Robot and AI for<br>automotive                                                                                          | <ul> <li>e-Memory (SRAM &amp;<br/>e-Flash replacement)</li> <li>NV-Logic for IoT,<br/>Mobile, Car<br/>Electronics, Robot, Al</li> </ul>                                                     | <ul> <li>Entry: Storage (SSD)</li> <li>Next: Industrial, Auto,<br/>Aerospace</li> </ul>                                             | <ul> <li>Immediate: IoT<br/>(battery-operated, ex.<br/>Data logging)</li> <li>Near :Automotive / Al</li> </ul>                                                   |

| Performance      | Pros             | <ul> <li>Ability to support<br/>DRAM, NOR, SRAM<br/>applications</li> <li>storage in metal<br/>layers</li> </ul> | <ul> <li>eNVM @ 125C with<br/>solder reflow is doable<br/>now</li> <li>Mobile cache at 10 ns<br/>is doable now</li> </ul>                                    | <ul> <li>Non volatile , no<br/>leakage</li> <li>Memory density</li> <li>Scalability</li> <li>Potential universal<br/>memory</li> </ul>             | <sram replacement=""><br/>• Low Power<br/>• Small Cell Size<br/><e-flash replacemt=""><br/>• Low Power<br/>• Small Cell Size<br/>• Better Endurance<br/>• High Speed Write</e-flash></sram> | <ul> <li>High bandwidth non-<br/>volatile writes</li> <li>High Endurance</li> <li>Reliability</li> <li>ST-DDR4 Interface</li> </ul> | <ul> <li>Fast and non volatile</li> <li>Huge power savings<br/>at chip level</li> </ul>                                                                          |

|                  | Cons             | <ul> <li>Maturity in embedded applications</li> <li>Cost/Scaling</li> </ul>                                      | <ul> <li>Last level cache is<br/>very hard –reliable 2</li> <li>ns write with low<br/>current</li> <li>MRAM will never be<br/>SCM – no multi-bits</li> </ul> | <ul> <li>SRAM like ns<br/>Read/write speed for<br/>some application</li> <li>SRAM like<br/>endurance or better<br/>for some application</li> </ul> | <sram replacement=""><br/>• Endurance<br/>• Write Power<br/>• Cost<br/><e-flash replacemt=""><br/>• Retention @HT<br/>• Cost</e-flash></sram>                                               | <ul> <li>Density &lt; DRAM</li> <li>Ind/Auto grades not<br/>yet avail</li> <li>Clock Freq &lt; DRAM</li> </ul>                      | <ul> <li>Endurance-speed-<br/>retention trilemma</li> <li>Heavy ECC required</li> <li>Limited read speed</li> <li>STT is not RAM<br/>compatible as is</li> </ul> |

| Action<br>Needed |                  | <ul> <li>Demonstrated volume<br/>in production</li> <li>Achieve Cell size &lt;20<br/>F<sup>2</sup></li> </ul>    | <ul> <li>Develop new<br/>materials/device for<br/>reliable 2 ns write with<br/>low current</li> </ul>                                                        | <ul> <li>SRAM like<br/>performance</li> <li>MLC MRAM</li> <li>Next-gen MRAM,<br/>SOT, VCMA</li> </ul>                                              | <ul> <li>Adv.Process Tech,<br/>High throughput</li> <li>ECC Tech</li> <li>Testing Tech</li> </ul>                                                                                           | •MTJ Scaling and<br>Design to extend temp<br>and improve<br>power/perf/area                                                         | <ul> <li>Achieve speed AND<br/>endurance at the<br/>same time – SOT !</li> <li>Improve read margin<br/>to raise read speed</li> </ul>                            |

# 2019 MRAM Markets and Applications

## Mark Webb

# MKW Ventures Consulting, LLC 8/5/2019

# **MRAM Future and Challenges**

- MRAM technology is here today

- We know what it is and what the challenges are

- Cost, Performance, Density, Endurance, SOC integration, etc

- In past year, we have updates on multiple fronts

- Existing companies announced 1Gbit parts, updated us on revenue and growth

- Multiple Companies presented embedded MRAM technologies

- IEDM/ISSCC Papers were popular. Embedded is an option to choose

- New technologies and models and optimization

- No need to speculate on what is coming

- Embedded: MRAM is ideal for market (revenue not measurable)

- Potential to replace NOR, SRAM, DRAM applications

- Ability to integrate (metal stacks), density (Mbit), performance (DRAM) match

embedded needs well

- Endurance work needed for full RAM replacement

- Looks like Embedded "Universal Memory"... Why isn't it here already?

- Discrete: Targets and Market growth uncertain (Rev <\$100M today)</li>

- Target applications requires specific density, speed, with NVM requirement.

- Small markets exist, but they are vulnerable to attack on all sides.

- No measurable NAND replacement market (Too small, expensive)

- Performance/cost/density ratio not on track to match DRAM

- Needs to dominate Niche or have "Killer App"

# **Revenue Projections for MRAM**

- In 2018 we predicted >\$900M in Revenue by 2024

- This will not happen

- 2018/2019 did not breakout like we hoped/expected

|      | MRAM Revenue<br>Baseline | Notes/required milestone                                                                        |

|------|--------------------------|-------------------------------------------------------------------------------------------------|

| 2020 | \$115M                   | 1Gb selling for revenue in 2020,<br>DRAM-Like performance. Multiple<br>IP sources for foundries |

| 2022 | \$217M                   | Multiple foundries and 1+ Memory company in volume                                              |

| 2024 | \$429M                   | 2+ memory companies in volume                                                                   |

Included discrete chips (may be stacked) and revenue from licensing Does not include embedded memory (no revenue model)

# What is Needed to meet Revenue by 2024 (Forecast=\$429M)

- <u>ALL MRAM</u>: Volume production in applications in 2020

- These are required to allow people to commit the technology to <u>significant</u> products.

- <u>Embedded:</u> Multiple foundry support with multiple applications

- MRAM penetration into market is measureable in 2020

- MRAM becoming chosen technology in 2022 designs

- <u>Discrete</u>: Meet aggressive endurance goals, Cell size Goals, Density roadmaps and Cost

- To have any penetration into larger markets, confidence needs to increase in delivering specs.

- MRAM is unique enough to not allow easy "backup plans", so high confidence is needed

- More details on MRAM vs other memories in my memory update on Tuesday

- Mark Webb, www.mkwventures.com

# MRAM Developer Day Panel Discussion

Daniel Worledge IBM Research

Senior Manager, MRAM

Daniel Worledge

8/5/19

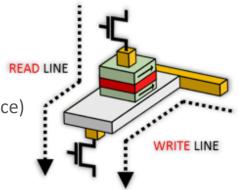

#### Key Advances in Spin-Transfer-Torque MRAM

| Device                                                            |                                                                                                                                 | Write                                                                               | Read                                                                                                               | Scaling                                                                                                   |  |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| 1974<br>Slonczewski (IBM)<br>invents magnetic<br>tunnel junction. | <b>1995</b><br>Moodera (MIT) and<br>Miyazaki (Tohoku U.)<br>demonstrate first room<br>temperature magnetic<br>tunnel junctions. | 1996<br>Slonczewski (IBM)<br>invents spin-transfer-<br>torque switching.<br>I < I c | 2004<br>Parkin (IBM) and Yuasa (AIST)<br>publish discovery of high magneto-<br>resistance in MgO tunnel junctions. | 2010<br>Worledge (IBM) and Ohno (Tohoku U.)<br>demonstrate first perpendicular<br>CoFeB tunnel junctions. |  |

| LOW RESISTANCE                                                    | HIGH RESISTANCE                                                                                                                 |                                                                                     |                                                                                                                    |                                                                                                           |  |

| Magnetic T                                                        | unnel Junction                                                                                                                  | Spin Transfer Torque                                                                | MgO Tunnel Barriers                                                                                                | Perpendicular<br>Magnetization                                                                            |  |

#### **MRAM** Applications

#### <u>Standalone</u>

- Replace battery-backed

SRAM or DRAM

- Buffer for hard disk drive

- Replace DRAM

Key requirements

Application examples

- Lower temp process is OK

- 0 C 70 C operation

- 256 Mb 1 Gb and up

- 30 70 ns read/write

- High endurance (10<sup>10</sup> 10<sup>15</sup>)

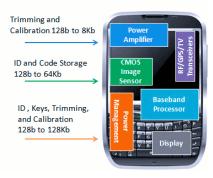

#### Embedded Non-volatile

Replace NOR eFlash to store:

Microcontroller code

Encryption key storage

Trimming and calibration

- 400C process required

- -40 C 105/125/150 C

- 1-64 Mb

- 30 ns read, 200 ns write

- Low endurance: 10<sup>6</sup>

#### Mobile Cache

Replace SRAM for low performance & power apps

- Wearable electronics

- Co-processors

- Internet of Things

- 400C process required

- 0 C 85 C operation

- 1-64 Mb

- 10 ns read/write

- High endurance (10<sup>12</sup> 10<sup>17</sup>)

#### Last Level Cache

- Fast dense memory for L3

or L4 cache

- Alternative to eDRAM

- 400C process required

- 0 C 85 C operation

- 1 Gb and up

- 1 2 ns read/write

- Unlimited endurance (10<sup>18</sup>)

#### Increasing difficulty

Daniel Worledge

MRAM Developer Day

8/5/19

# MRAM in Edge AI and AloT

# **Terry Torng**

\***Stealth Startup** co-founder Gyrfalcon Technology Inc

Santa Clara, CA August 2019

# Core Challenge To AI: Energy Efficincy

- Data Center Energy Use is Growing....

- "Global data centers used roughly 3% of total electricity in 2016, and will double every four years"

- Radoslav Danilak, December 15, 2017

- "Global IP traffic will increase nearly threefold over the next five years, and will have increased 127-fold from 2005 to 2021."

- Bill Kleyman, Mar 09, 2018

Edge and IoT Devices....

"Al is hungry for processing power. IoT is projected to exceed 20b devices by 2020. There are currently 10b internetconnected devices, doubling to 20 billion will require massive increases to our data center infrastructure, which will massively increase our electricity consumption." Radoslav Danilak, December 15, 2017

Need to make us greener... 5G is coming.....

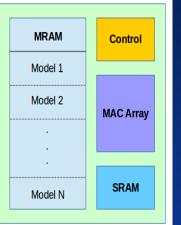

# MRAM for AI

#### Challenges for the Edge Al

Memory : 75 to 80+ % of chip area Memory : 67% or more leakage power

#### **SRAM like MRAM:**

- 1. Few ns read/write,

- 2. 10<sup>16</sup> endurance,

- 3. memory density 3 : 1 or more vs SRAM.

#### Goal:

1. Chip size ½ of less.

2. AloT (low duty), 60% less power consumption than SRAM only solution.3. less than 1mw "high performance" Al accelerator for edge or AloT

## PPP (power, performance and price) Now, Next and Future

- Hardware/software/MRAM co-design

- Simplify circuit design

- Manufacturing friendly for foundries

- high DR/R materials and different thermal budget processes...

- OST, SOT, voltage-controlled and MLC MRAM compatible

- Chip/wafer yield friendly

#### What is the main segment for MRAM in 2024? <My Position> e-Memory of Logic @ 2024

|                             | CMOS MTJ                |                       | смоя                            | MTJ                                            | Other NVM           |                      |

|-----------------------------|-------------------------|-----------------------|---------------------------------|------------------------------------------------|---------------------|----------------------|

|                             | SRAM-LLC                | STT-MRAM(S)           | eFlash                          | STT-MRAM(F)                                    | ReRAM               | PCRAM                |

| Operation Voltage           | <1.1 V                  | <0.5 V 🙂              | 12 V                            | <0.5V 😜                                        | > 6.5 V             | > 1.8 V              |

| Write Current               | 10 <sup>-5</sup> A      | 10 <sup>-5</sup> A    | 10 <sup>-4</sup> A              | 10 <sup>-5</sup> A 🙂                           | 10 <sup>-4</sup> A  | 10 <sup>-4</sup> A   |

| Write Speed                 | <10ns                   | <10 ns                | 10000 ns                        | <200 ns 😮                                      | 50 ns               | 100 ns               |

| Read Speed                  | <5ns                    | <5 ns                 | 30 ns                           | <25 ns                                         | < 5 ns              | < 5 ns               |

| Retention                   | Volatile                | 1~Several Month       | 10Years                         | 10Years                                        | 10Years             | 10Years              |

| Endurance                   | 10 <sup>15</sup>        | 10 <sup>15</sup>      | 10 <sup>3~4</sup>               | < 10 <sup>8~12</sup>                           | 10 <sup>6</sup>     | $10^9 - 10^{12}$     |

| Cell Size                   | 160 ~ 280F <sup>2</sup> | 12 ~ 28F <sup>2</sup> | 64 ~ 128F <sup>2</sup>          | 6 ~ 14F <sup>2</sup>                           | 6 ~10F <sup>2</sup> | 4 ~ 19F <sup>2</sup> |

| ①Low Power ②Small Cell Size |                         |                       | 1 Low Power (<br>3 Better Endur | 2) High Speed Write<br>ance (4)Small Cell Size |                     |                      |

Which application / market will drive it? <My Position> Mobile, IoT, Car Electronics, AI, Robot etc

Final Panel on MRAM in 2024

Tetsuo Endoh @ CIES Tohoku University

#### What are the challenges?

# <My Position> Improvement of MRAM Performance for each Application For higher level cache: High Speed Write & Low Write Power & over 10<sup>15</sup> Endurance@128Mb-GbMRAM For e-Flash of Automotive Application: Excellent Thermal Stability (Δ) For Main Memory : Scalability & High Density Array

#### What technological breakthrough needed?

<My Position>

- 1) Advanced Process Technology

- including High throughput & Damage Control Technology

- 2) Circuit Technology including ECC Technology

- 3) Testing Technology for mass production

### Most critical problem of MRAM is our mind. ⇒ Tough Mind to believe MRAM Potential

MRAM Developer Day 2019 Santa Clara, CA

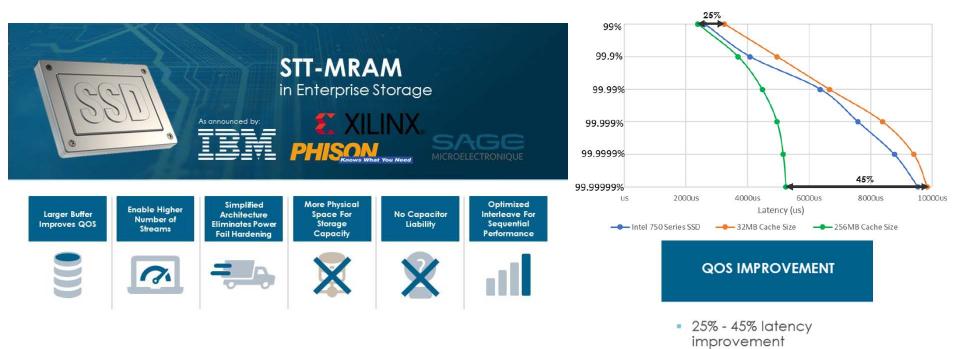

Data Persistence at Speed

## MRAM Developer Day 2019 Panel: MRAM Application – Pros/Cons

#### Tom Andre VP Engineering, Everspin Technologies

#### **STT-MRAM Applications Today**

Latency improvement is architecture dependent

#### **MRAM Performance**

| FEATURES     1M x 16 MRAM       • +3.3 Volt power supply     Fast 35 ns read/write cycle                                                                                                                                                                                                                                                                                                                                                                                       |                                 | 16Mb<br>Toggle                          | 256Mb<br>ST-DDR3                 | 1Gb<br>ST-DDR4                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------|----------------------------------|----------------------------------------|

| EMD3D256M08BS1<br>EMD3D256M16BS1                                                                                                                                                                                                                                                                                                                                                                                                                                               | VDD / VPP                       | 3.3V                                    | 1.5V                             | 1.2V / 2.5V                            |

| FEATURES       256Mb ST-DDR3 Spin-transfer Torque         • Non-volatile 256Mb (32Mb x 8, 16Mb x 16) DDR3                                                                                                                                                                                                                                                                                                                                                                      | Data Retention                  | <b>20 years / 85C</b><br>2 years / 125C | 3 months / 70C                   | 3 months / 70C<br>10 yrs / 85C capable |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Endurance                       | >1e16<br>(>10yrs constant use)          | <b>1e10 cycles</b><br>every page | <b>1e10 cycles</b><br>every page       |

| FEATURES 1Gb Non-Volatile ST-DDR4 Spin-transfer Torque MRAM                                                                                                                                                                                                                                                                                                                                                                                                                    | Uniform 10yr<br>writes per Chip | <b>18 PBW</b><br>(performance limit)    | <b>320 PBW</b> (cycle limit)     | <b>840 PBW</b><br>(performance limit)  |

| <ul> <li>128Mb x8, 64Mb x16 Organization</li> <li>Supports most DDR4 features</li> <li>Page size of 1024 bits for x8, 2048 bits for x16</li> <li>VDD = VDDQ = 1.2v</li> </ul>                                                                                                                                                                                                                                                                                                  | Peak Bandwidth<br>per x16 Chip  | 57MB/s                                  | 2.67GB/s                         | 2.67GB/s                               |

| <ul> <li>VPP = 2.5V</li> <li>Operating Temperature of 0°C to 85 °C</li> <li>667MHz clock frequency (fCK)</li> <li>On-Device Termination</li> <li>Multipurpose register READ and WRITE capability</li> <li>Per-Device addressability (PDA)</li> <li>Connectivity Test</li> <li>On-Chip DLL aligns DQ, DQS, DQS transition with CK transition</li> <li>Burst lengths of 8 addresses</li> <li>All addresses and control inputs are latched on rising edge of the clock</li> </ul> |                                 |                                         |                                  |                                        |

#### **STT-MRAM Areas for Development**

|                  | Storage / SSD                               | Industrial                        | Auto                                           | Aerospace                  |

|------------------|---------------------------------------------|-----------------------------------|------------------------------------------------|----------------------------|

| Application      | Non-volatile Data<br>Buffer/Cache/PMR       | Non-volatile Data<br>logs, params | Non-volatile Data<br>params, buffer            | Non-volatile Code,<br>Data |

| STT-MRAM benefit | Write Bandwidth,<br>Endurance               | Endurance,<br>Reliability         | Write BW, End,<br>Reliability                  | Rad Hard, Reliability      |

| Density          | 128MB - >1GB                                | 8MB - 128MB                       | 128MB - >1GB                                   | 8MB – 128MB                |

| Operating Temp   | 0C - 85C                                    | <b>-40C</b> – 85C                 | -40C - 125C (Grade 1)<br>-40C - 150C (Grade 0) | -40C – 125C<br>-55C – 125C |

| Data Retention   | 3 months / 70C                              | 10 years / 85C                    | Profile across temp                            | 15 yrs / 105C              |

| Endurance        | Buffer: 1e10 every page<br>PMR: >1e15 total | varies by app<br>>1e15 total      | varies by app                                  | varies by app              |

| Peak Bandwidth   | 5GB/s - >12GB/s                             | 10MB/s – 2GB/s                    | 10MB/s – 2GB/s                                 | <100MB/s                   |

MRAM Developer Day August 5, 2019

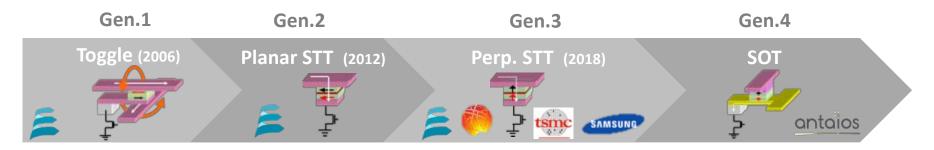

Mission Statement : Jointly develop and license SOT (technology and IPs) as the **next-generation MRAM** that solves STT shortcomings

Endurance-Retention-Speed tradeoff → Limited to e-NVM applications

Infinite endurance / High intrinsic speed = Fully RAM compatible (enables Cache applications)

# PERFORMANCES PROS & CONS (STT)

#### Pros

- Fast and low (write) power, beats eFlash hands down

- Huge power savings at chip level (+ endurance)

- Fast and non volatile

- Zero standby power, zero leakage, unlike SRAM

#### Cons (STT)

- STT not RAM compatible

- o Endurance / speed / retention trilemna

- Low read window = limited read speed

- Heavy ECC needed (cost, performance limitations)

24

#### "Low Hanging Fruit" Market : IoT

In particular for those applications involving large amounts of data for which power and endurance are key (ex. Data logging, audio/video monitoring)

#### Other "near-ready" markets

- Automotive Provided the temperature/reliability specs are met

- Al chips Killer benefits of MRAM (can hold data during compute) STT good enough as-is, but SOT should be even better

STT is excellent for NVM (e-Flash) replacement, but full benefit of MRAM migration will be achieved when cache (e-SRAM) is addressed as well

# ACTIONS NEEDED (AS NEXT STEP)

To unleash full potential of embedded MRAM ...

- Improve device towards RAM requirements

- Need speed AND endurance at the same time

- STT won't do it Need something new

- <u>SOT is the only solution (fast write & infinite endurance)</u>

- Improve read margin to raise (read) speed

- By materials (TMR increase)

- By design (device and chip level)

To address standalone market ...

- Achieve high capacities (>Gb)

- Control of BER, distribution (tails), ...

- Dedicated memory process / architecture for high density (low F2)